一、时钟基本概念

PLL:phase locked loop 倍频

Prescaler:预分频器

PFD:相位分数分频器(可升可降)

7个pll,pll2、pll3一共有8个pfd

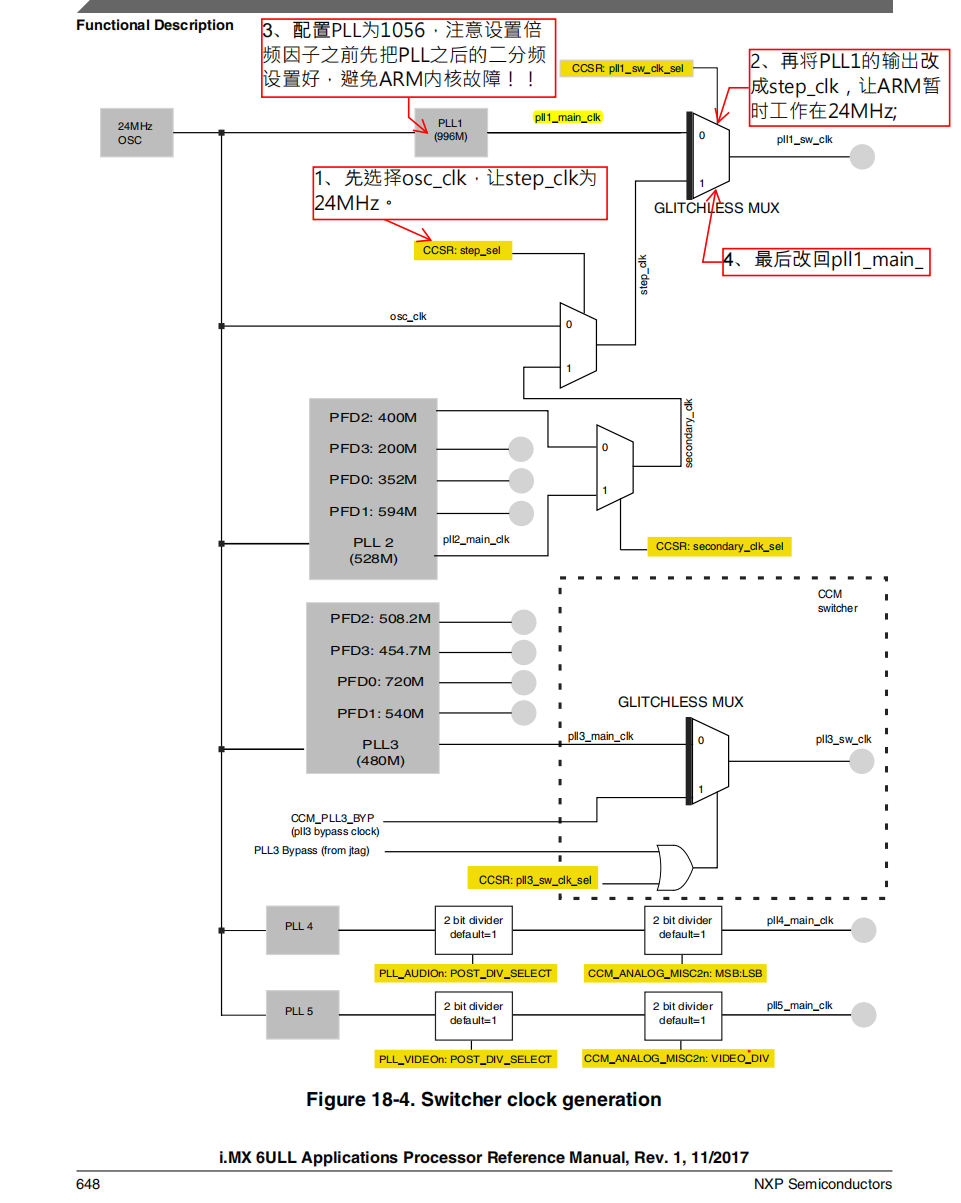

二、时钟原理

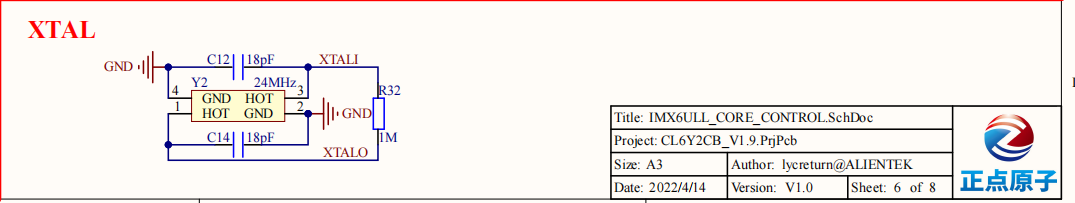

1.核心版原理图

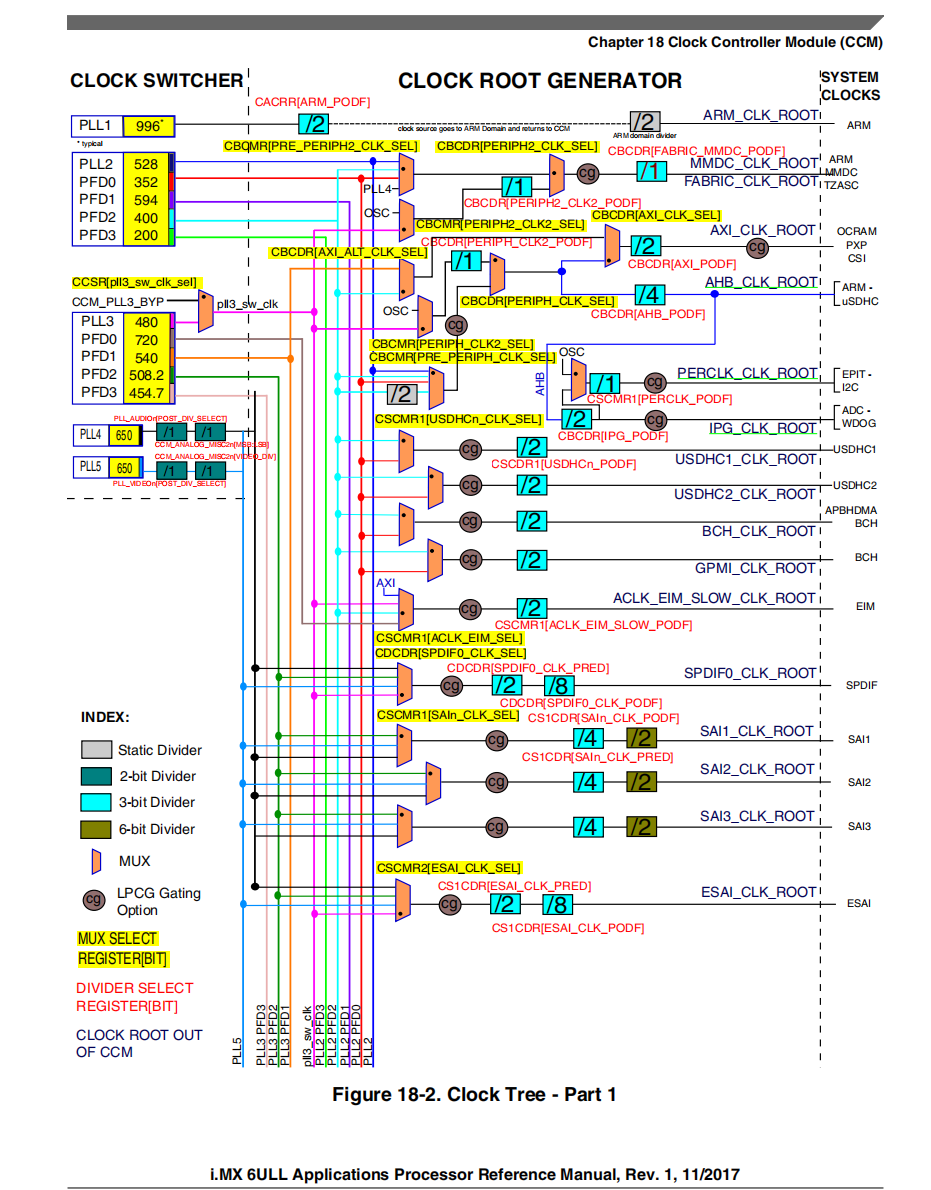

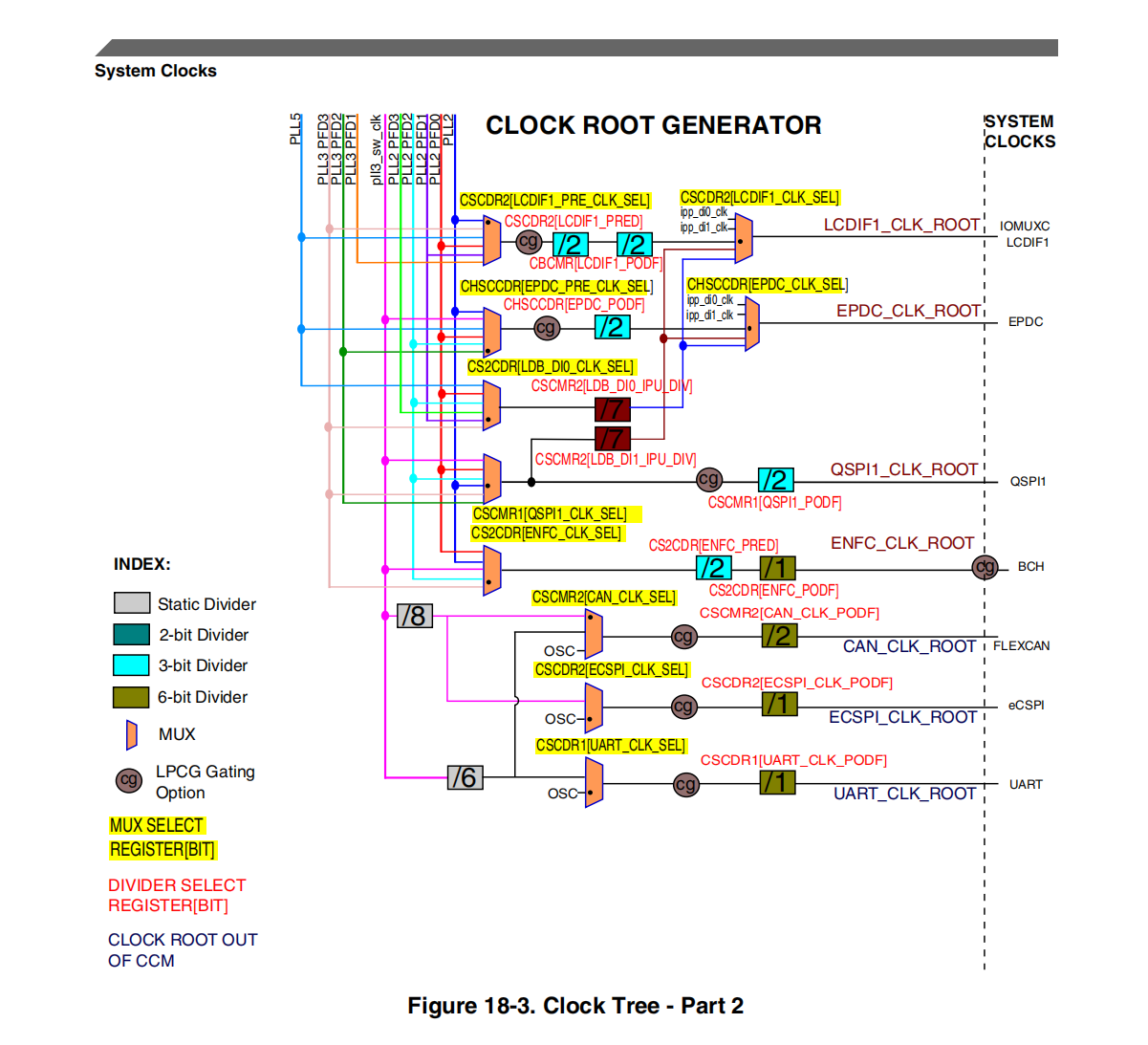

2.时钟树

2,3,4,为分频因子展开所占二进制位数,值要加一,因为要作为分母使用

参数配置如下

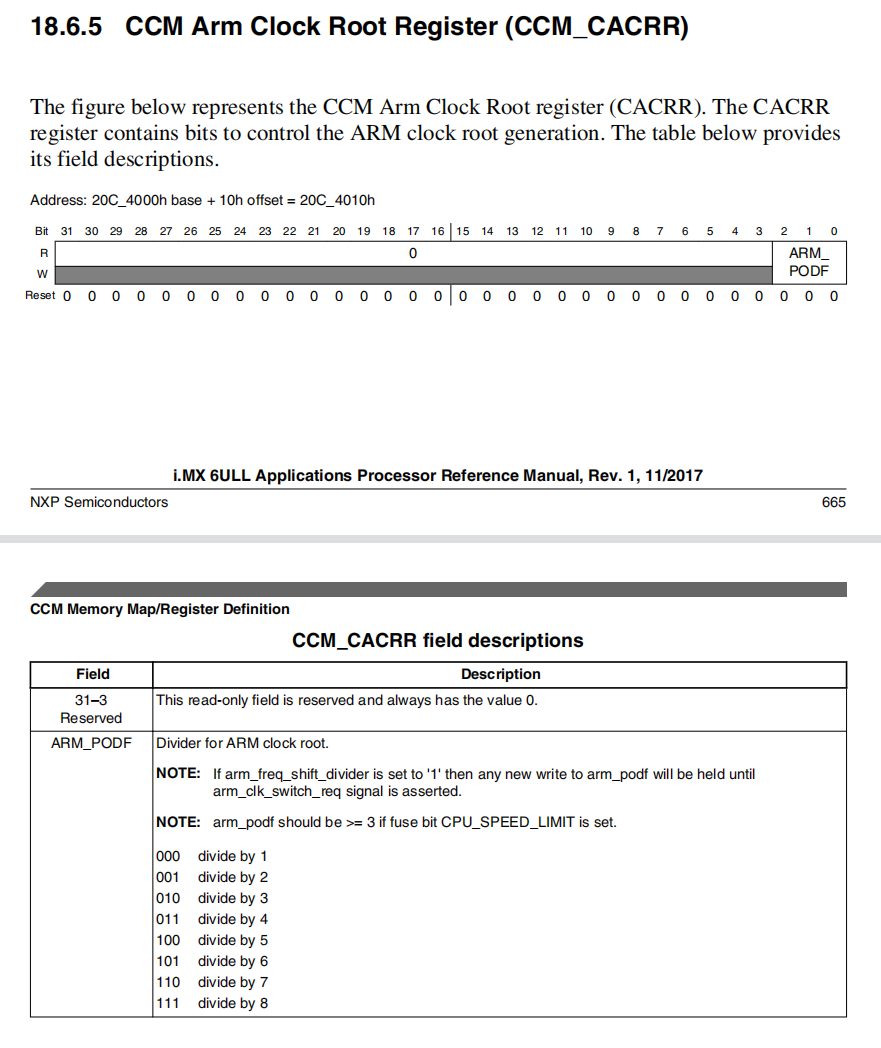

3.ARM PLL配置方法

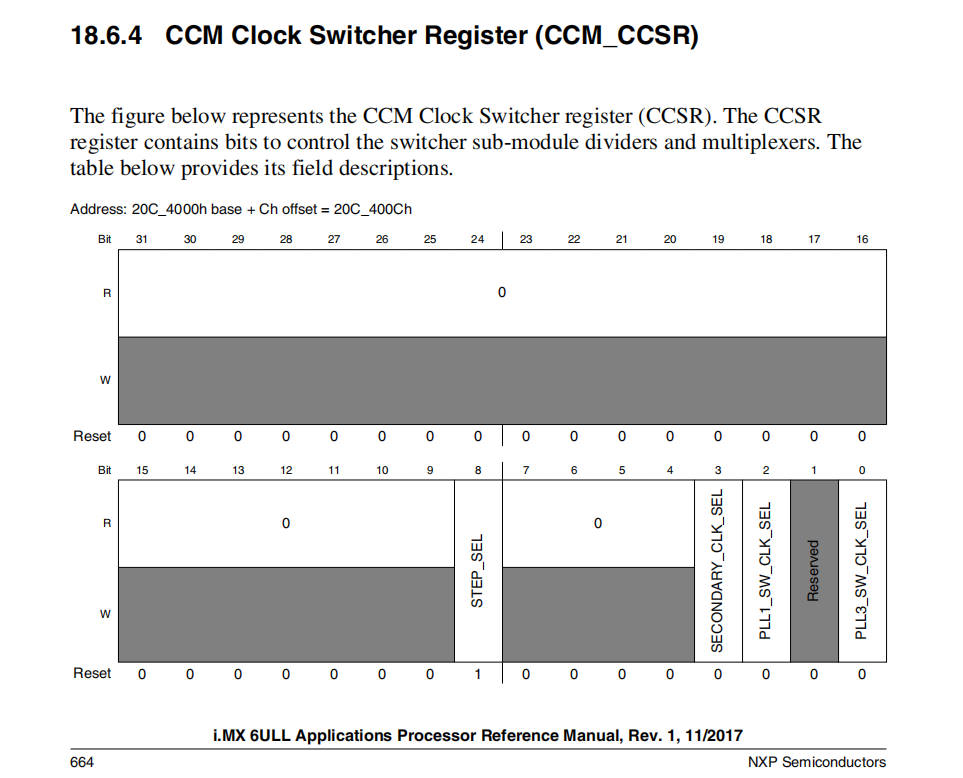

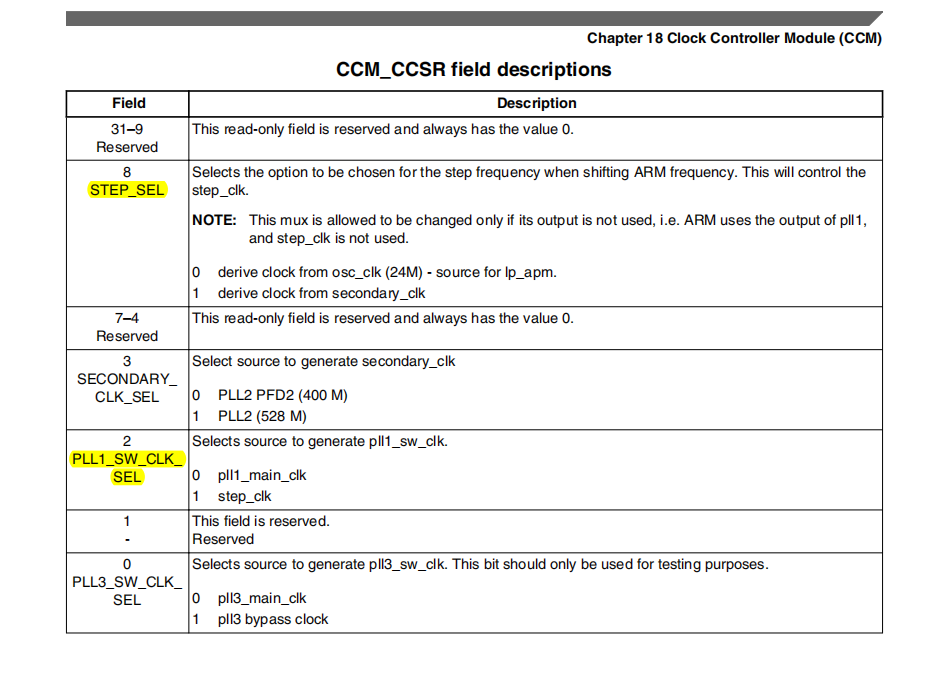

1)CCSR寄存器

第一二四步

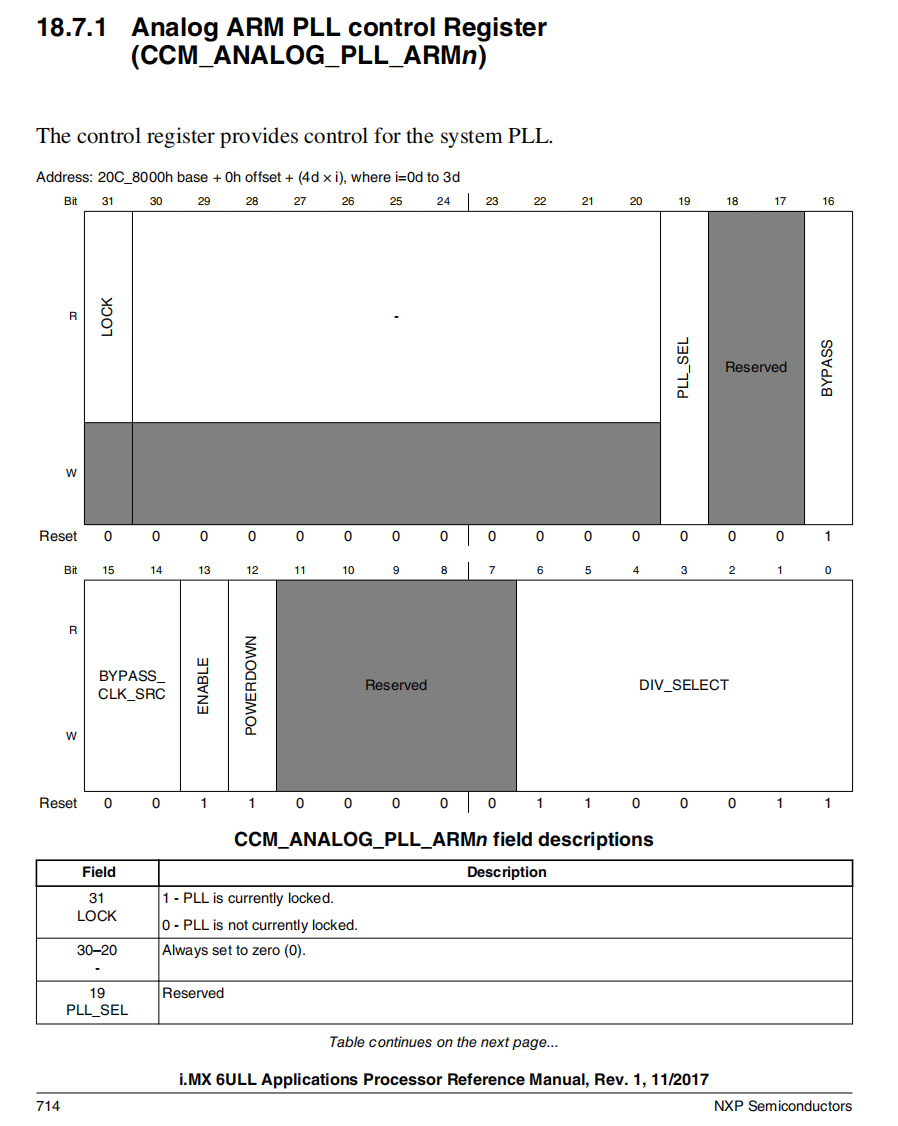

2)ARM_PLL寄存器

第三步

配置pll

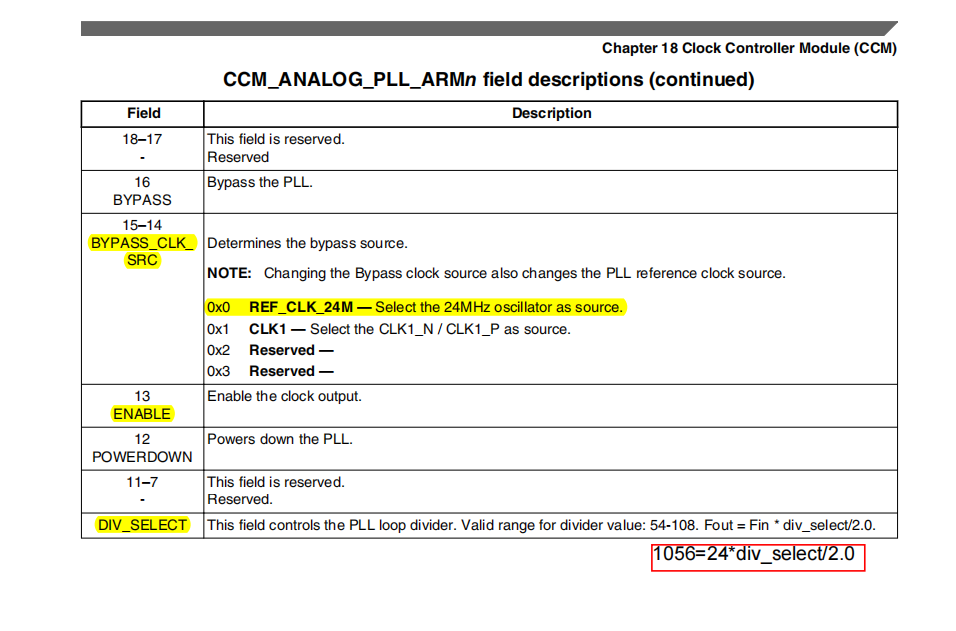

3)CCM_CACRR寄存器

第三步

设置分频因子

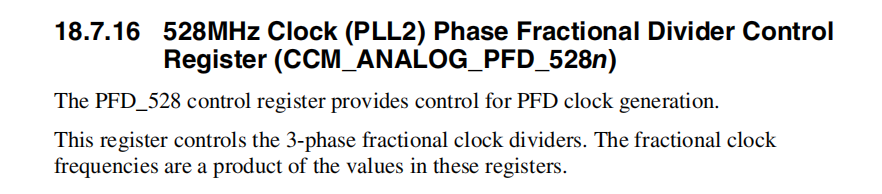

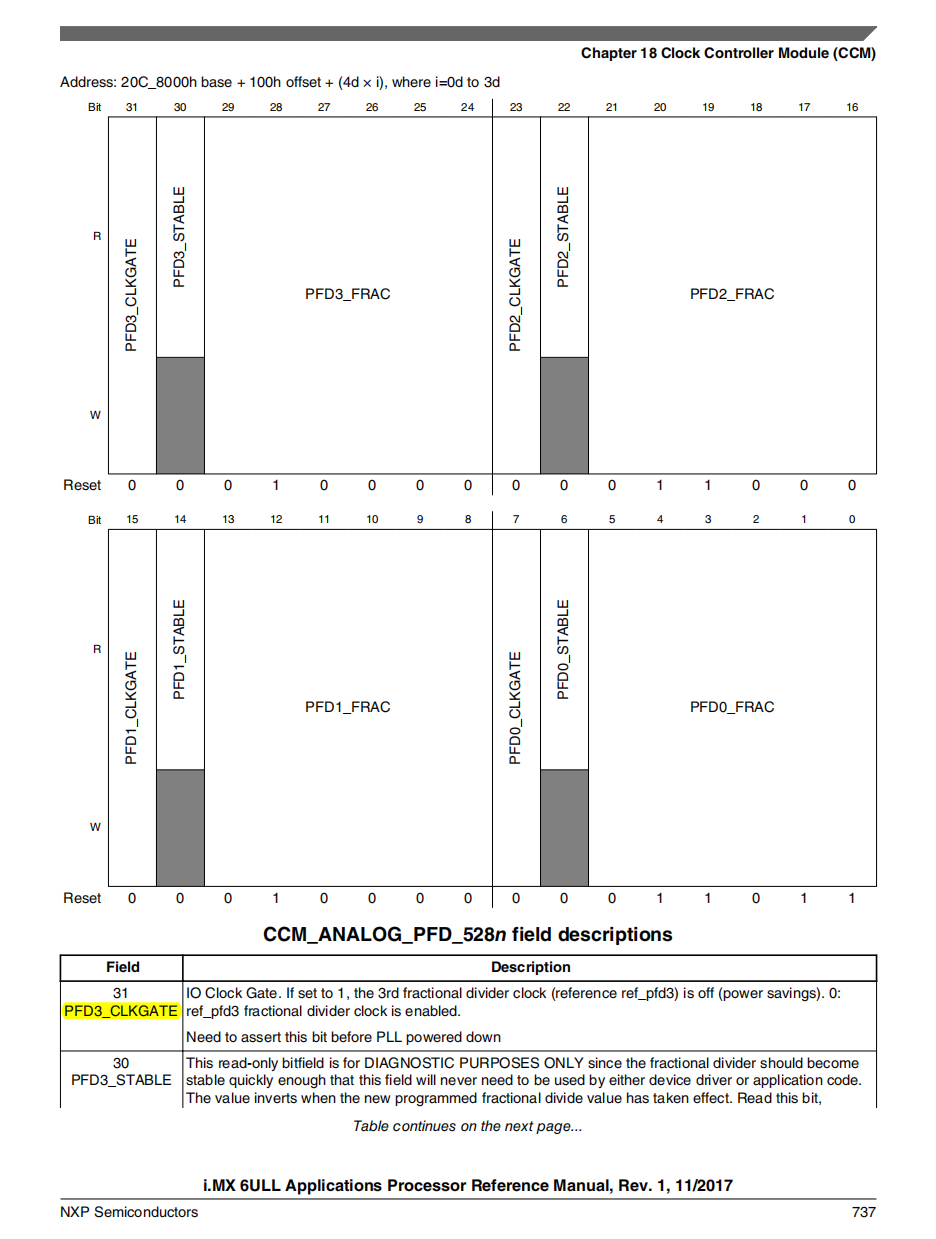

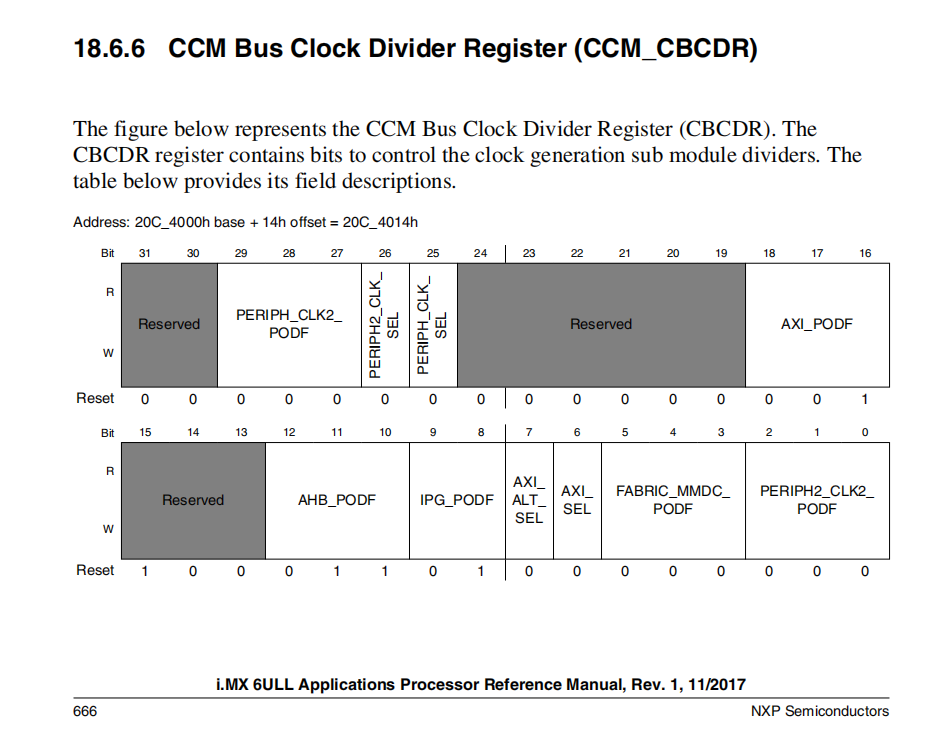

4.PLL2 配置(528)

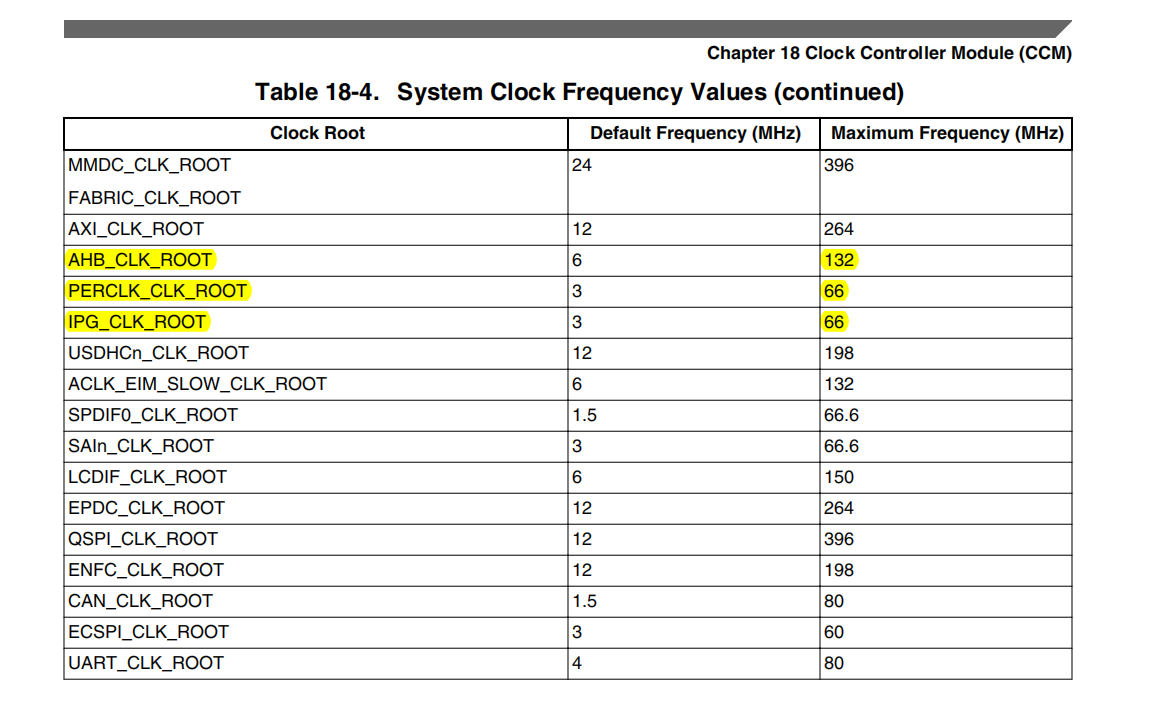

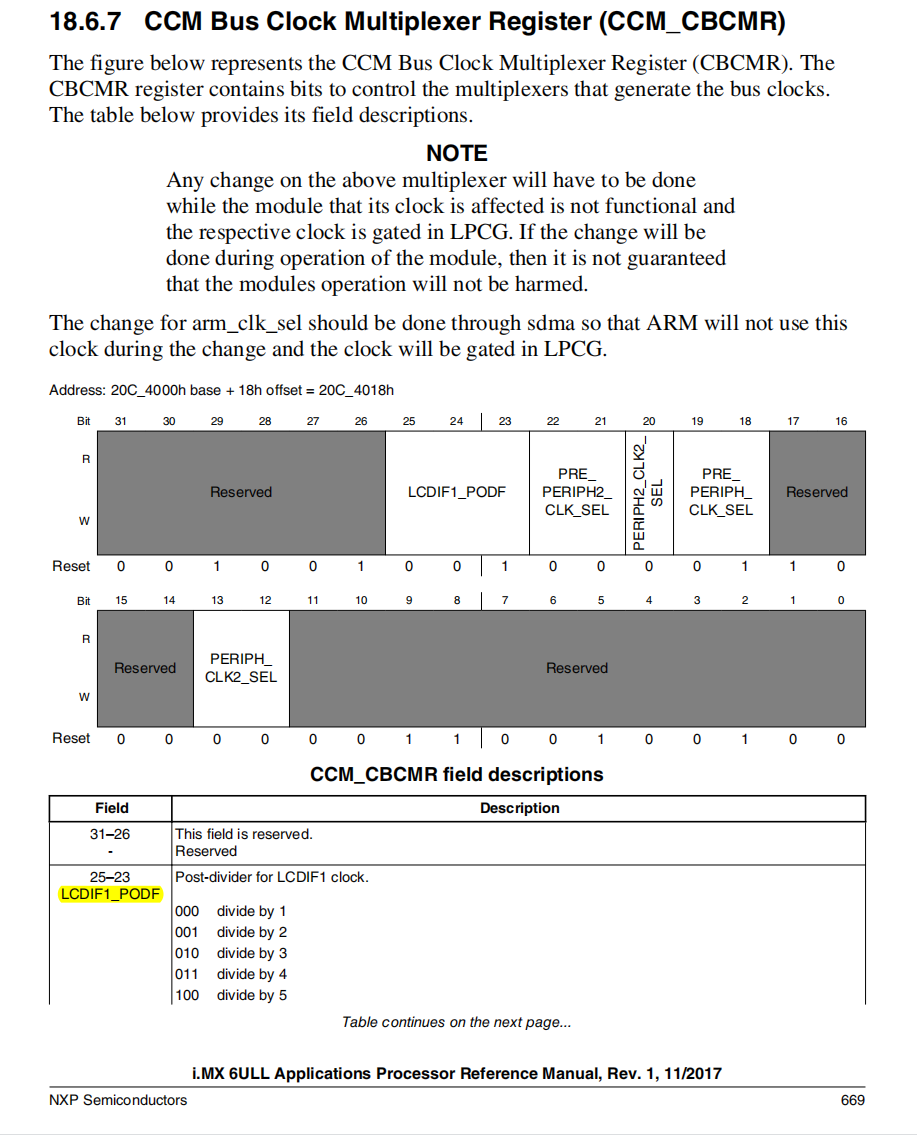

5.AHB_CLK_ROOT(绿色的线)

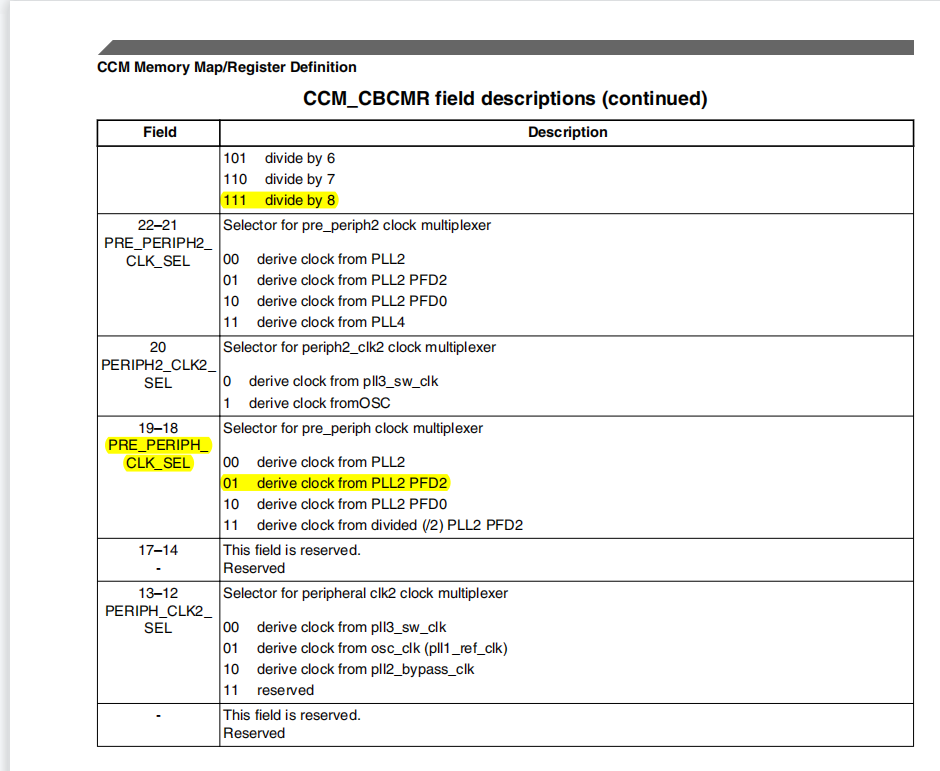

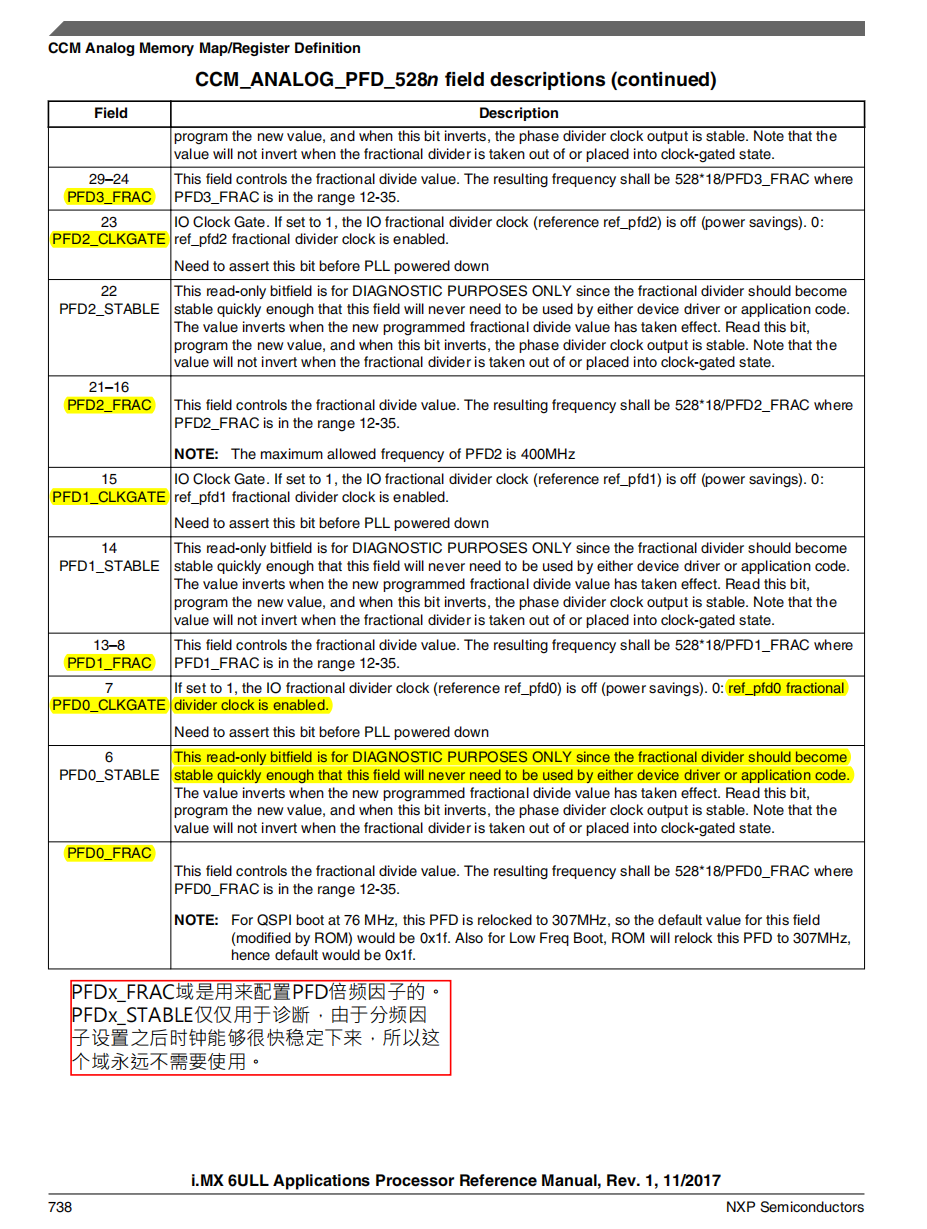

1)CBCMR

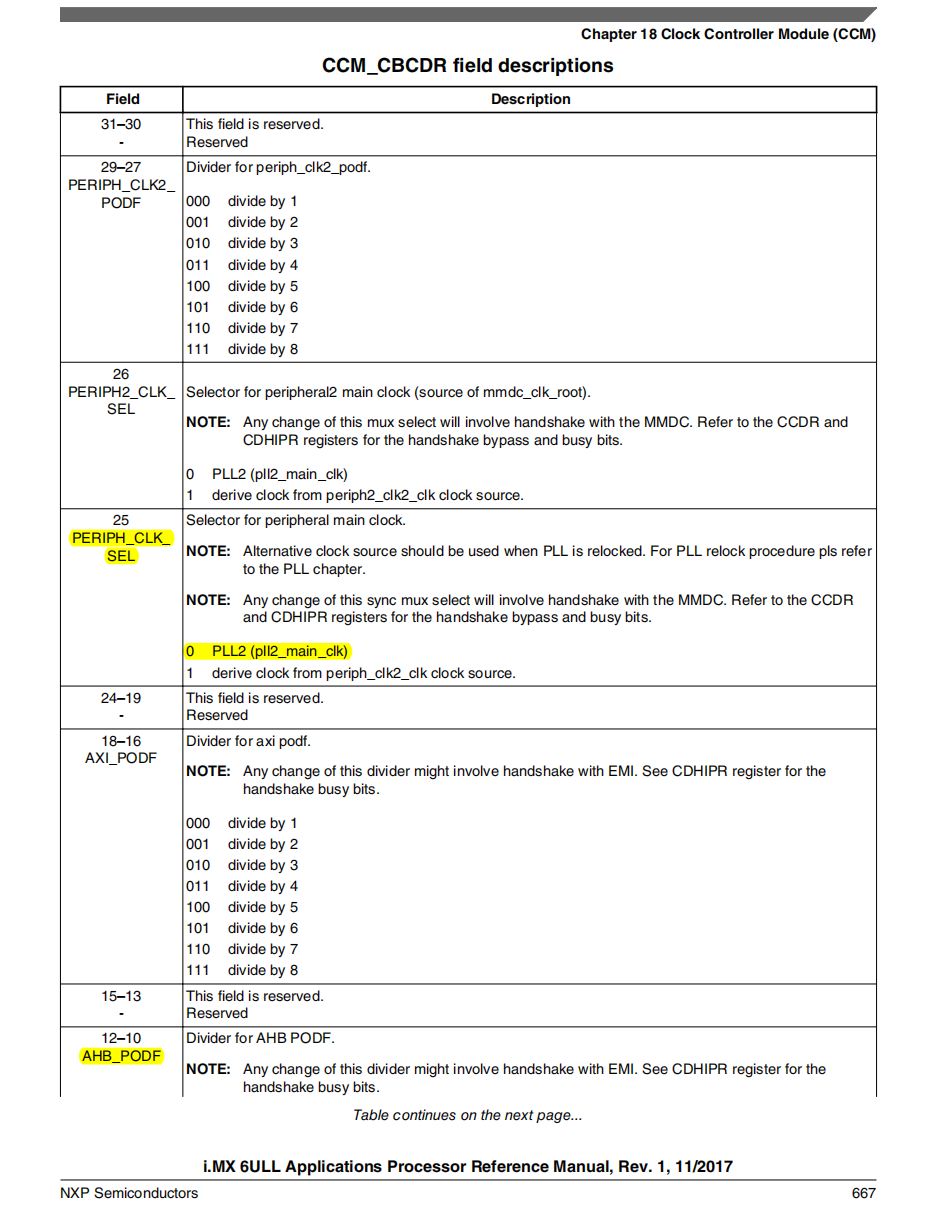

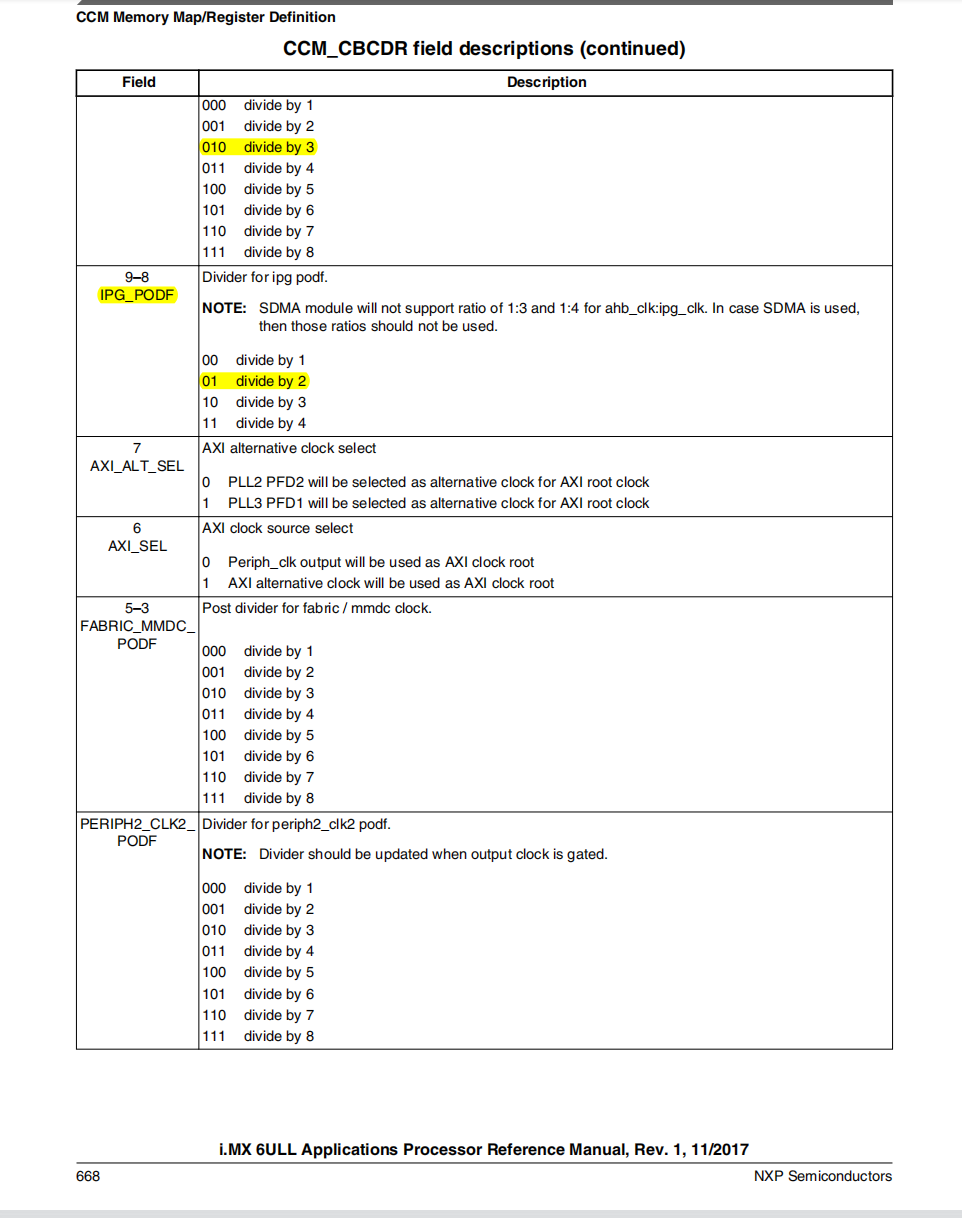

2)CBCDR

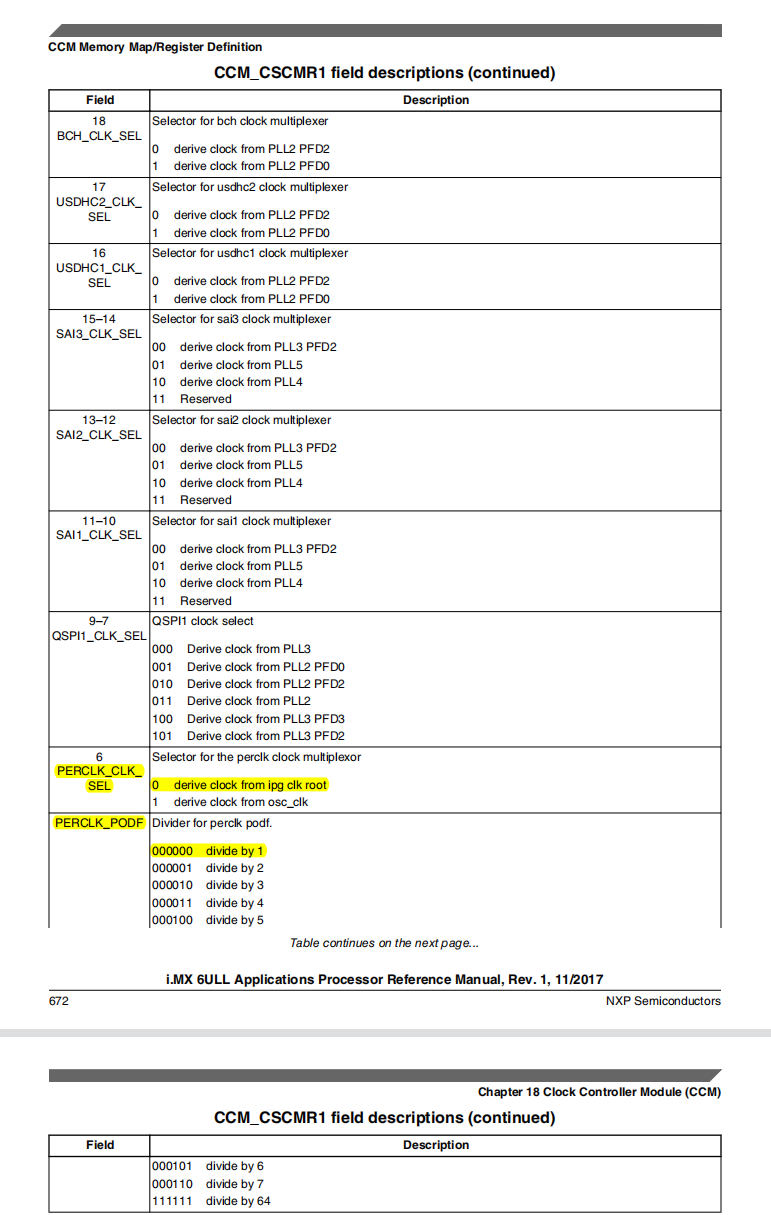

6.PERCLK_CLK_ROOT

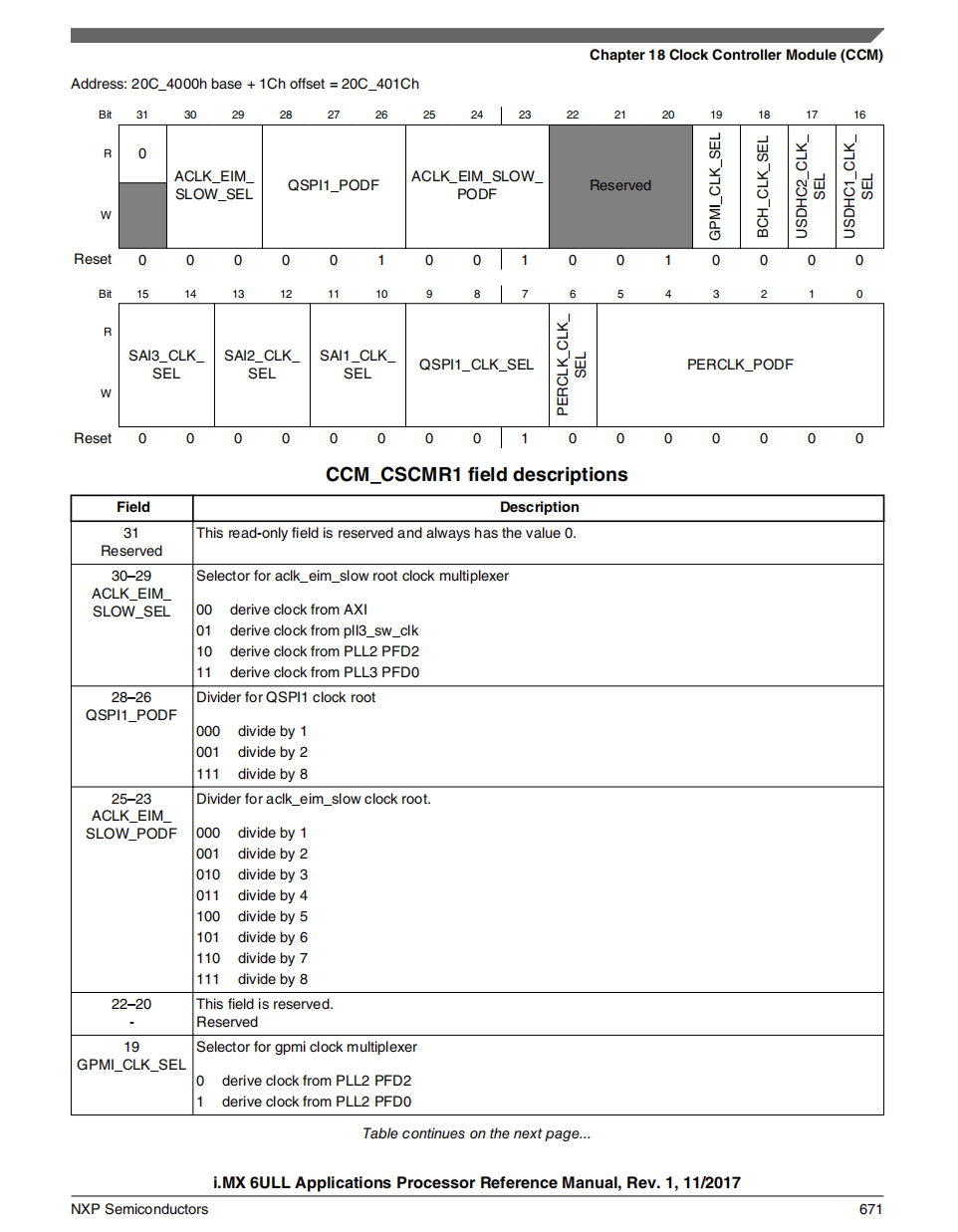

1) CSCMR1(修改一分频)

7.IPG_CLK_ROOT

AHB_CLK_ROOT(绿色的线)设置好后,通过CBCDR进行二分频

三、代码

结构不变

1.bsp

1)clock.c

#include "clock.h"

#include "led.h"

#include "MCIMX6Y2.h"

#include "core_ca7.h"

void init_clock(void)

{

unsigned int t;

CCM->CCSR &= ~(1 << 8);

CCM->CCSR |= (1 << 2);

t = CCM_ANALOG->PLL_ARM;

t &= (~(3 << 14));

t |= ((1 << 13));

t &= (~(0x7f << 0));

t |= (88 <<0);

CCM_ANALOG->PLL_ARM = t;

CCM->CACRR |= (1 << 0);

CCM->CCSR &= (~(1 << 2));

t = CCM_ANALOG->PFD_528;

t &= (~(0x3f << 0) | (0x3f << 8) | (0x3f << 16) | (0x3f << 24));

t &= (~((1 << 7) | (1 << 15) | (1 << 23) | (1 <<31)));

t |= ((27 < 0) | (16 << 8) | (24 << 16) | (32 << 24));

CCM_ANALOG->PFD_528 = t;

t = CCM_ANALOG->PFD_480;

t &= (~(0x3f << 0) | (0x3f << 8) | (0x3f << 16) | (0x3f << 24));

t &= (~((1 << 7) | (1 << 15) | (1 << 23) | (1 <<31)));

t |= ((12 < 0) | (16 << 8) | (17 << 16) | (19 << 24));

CCM_ANALOG->PFD_480 = t;

t = CCM->CBCMR;

t &= ~(3 << 18);

t |= (1 << 18);

CCM->CBCMR = t;

CCM->CBCDR &= ~(1 << 25);

t = CCM->CBCDR;

t &= ~((7 << 10) | 3 << 8);

t |= ((2 << 10) | (1 << 8));

CCM->CBCDR = t;

CCM->CSCMR1 &= ~(1 << 6);

CCM->CSCMR1 &= ~(0x3f << 0);

enable_clocks();

}2)clock.h

#ifndef _CLOCK_H_

#define _CLOCK_H_

extern void init_clock(void);

#endif2.project

1)main.c

#include "beep.h"

#include "led.h"

#include "key.h"

#include "MCIMX6Y2.h"

#include "core_ca7.h"

#include "gpio.h"

#include "interrupt.h"

#include "clock.h"

int main(void)

{

init_clock();

system_interrupt_init();

init_led();

init_beep();

//init_key();

while(1)

{

led_nor();

delay(0x0FFFFF);

}

return 0;

}2)start.S

.global _start

_start:

ldr pc, =_reset_handler

ldr pc, =_undefine_handler

ldr pc, =_svc_handler

ldr pc, =_prefetch_abort_handler

ldr pc, =_data_abort_handler

ldr pc, =_reserved_handler

ldr pc, =_irq_handler

ldr pc, =_fiq_handler

_undefine_handler:

ldr pc, =_undefine_handler

_svc_handler:

ldr pc, =_svc_handler

_prefetch_abort_handler:

ldr pc, =_prefetch_abort_handler

_data_abort_handler:

ldr pc, =_data_abort_handler

_reserved_handler:

ldr pc, =_reserved_handler

_irq_handler:

subs lr, lr, #4

mrc p15, 4, r1, c15, c0, 0

add r1, r1, #0x2000

ldr r0, [r1, #0x0C]

stmfd sp!, {r0-r12, lr}

stmfd sp!, {r0, r1}

cps #0x1f

stmfd sp!, {lr}

bl system_interrupt_handler

ldmfd sp!, {lr}

ldmfd sp!, {r0, r1}

str r0, [r1, #0x10]

ldmfd sp!, {r0-r12, pc}^

_fiq_handler:

ldr pc, =_fiq_handler

_reset_handler:

//mrs r0, cpsr

//bic r0, r0, #0x1F

//orr r0, r0, #0x12 //irq

//bic r0, r0, #(1 << 7)

//msr cpsr, r0

cps #0x12

ldr sp, =0x86000000 //起始地址80000000,ram大小为512mb(20000000) 80000000~A0000000-1

//mrs r0, cpsr

//bic r0, r0, #0x1F

//orr r0, r0, #0x1F //system

//msr cpsr, r0

cps #0x1f

cpsie i

ldr sp, =0x84000000 //给irq分配的栈指针空间

bl _enable_icahce

bl _set_vbar

bl _bss_clear

b main

_enable_icahce:

mrc p15, 0, r0, c1, c0, 0

bic r0, r0, #(1 << 13)

orr r0, r0, #(1 << 12)

mcr p15, 0, r0, c1, c0, 0

bx lr

_set_vbar:

ldr r0, =0x87800000

mcr p15, 0, r0, c12, c0, 0

bx lr

_bss_clear:

ldr r0, =__bss_start

ldr r2, =__bss_end

loop:

mov r1, #0

str r1, [r0]

add r0, r0, #4

cmp r0, r2

blt loop

bx lr

finished:

b finished