在上几章的内容中,我们从纯粹高速信号的理论分析,到 Cadence 工具的具体使用都做了详细的讲解和介绍。相信读者通过前面章节的学习,已经对高速系统的设计理念及 Cadence 相应的设计流程和工具有了一个基本的认识。但是,对于高速电路设计的学习就止于此的话,那么实际上还是纸上谈兵。

如果读者真正面对高速电路设计的挑战与乐趣,下面从本章开始,我们通过一个实际的设计实例来贯穿前面几章的所有内容,从调入网表的设计开始,一步一步带领读者,使用 Cadence 的高速设计流程工具链完成整个设计。

只有通过读者亲自动手,从头到尾做一个完整的设计,对高速电路设计有切身的体会,再加深理论的学习,不断总结和积累实际的设计经验,才能在技术飞速发展的时代利于不败之地。

本章所讲述的内容,是对一个设计实例的逐步实现过程。因此,需要读者能够积极参与,在阅读本书内容的同时,应该在自己的电脑上同步进行实际的操作演练,这样才能更好地理解所讲述的内容,也能够通过解决在操作过程中遇到的实际问题,将高速电路的设计精髓和理念变成自己的知识。在本章的讲述过程中,不再详细介绍工具的操作方法,而是注重工具的使用,也就是说,我们不会再介绍在哪个菜单里,选择哪个工具,然后点击哪个按钮,而是直接讲我们要打开哪个工具,做什么事情,得到什么结果。如果对 Cadence 的高速设计流程理念和工具链的使用还存在疑问的话,建议读者再熟悉一下第4章和第5章的内容。

再次请读者注意,本章所使用的设计实例及相关资料,可以通过合作网站提供的推广和论坛网站 shaopeng.pcteach.net 和 shaopeng.pccbsbs.com 找到下载链接进行免费下载。并且,对于本书推出之后的一系列相关技术探讨和交流,也将在这里进行。所以希望读者能够在此论坛进行免费注册,并定期查阅技术资料的更新和问题讨论。

需要声明,本设计实例项目“BookSI_Demo.brd”仅用于本书的讲解和示范目的。作者不保证该实例(包括整体及任何属于该设计实例之中的任何设计元素)被用于其他目的的正确性。对该实例被用于其他场合和目的时所引发的后果和损失,作者不承担任何责任!

好,现在请打开你的电脑,我们开始一步一步地完成这个设计。

6.1 设计实例介绍

在开始设计之前,我们要先了解这个例子的内容,清楚设计目的,也就是我们的任务。实际上,对于任何一件事情,在实际动手之前,一定要了解设计意图和目的,不清楚目标在哪里,是没有办法做好事情的。在这里给读者讲个故事,这是作者在上大学期间发生的真实事件。在一次电路实验课上,老师留了一个实验任务,用示波器测量一个 5MHz 的方波信号,只要能够让学生在示波器的屏幕上看到 5MHz 方波信号的波形就算完成。当时的示波器是那种非常笨重的示波器,测量带宽为 5M。老师说开始后,学生们就开始忙碌起来。看起来任务很简单,接入信号,调整示波器到适当的测量精度,显示出波形就算完成任务了,然而十几分钟后,没有一个人能够在示波器上看到老师要求的方波信号。聪明的读者,你明白其中的原因么?

是的,这是个不可能完成的任务,Mission Impossible!道理很简单,要观察到 5MHz 的方波信号,我们至少需要三次谐波进行重现,这样才能够看到方波波形的大致轮廓。可是示波器的测量带宽只有 5MHz,那么我们只能看到一个 5MHz 的正弦波,事实上,能看到 5MHz 的正弦波就算示波器调谐正确,完成了任务。可是当时我们没有人去想,我们的任务是什么?而面临的条件又是什么?

这堂课,给我留下的印象非常深刻,作为一名工程师,当我们面临一个问题的时候,我们始终要保持清醒的头脑,每时每刻都要问自己,我们面临的问题是 什么?有哪些现实条件和方法可以利用?如果不能完美地达到既定目标,那么能够完成的状态应该是什么程度,在这个过程中要做哪些折中?

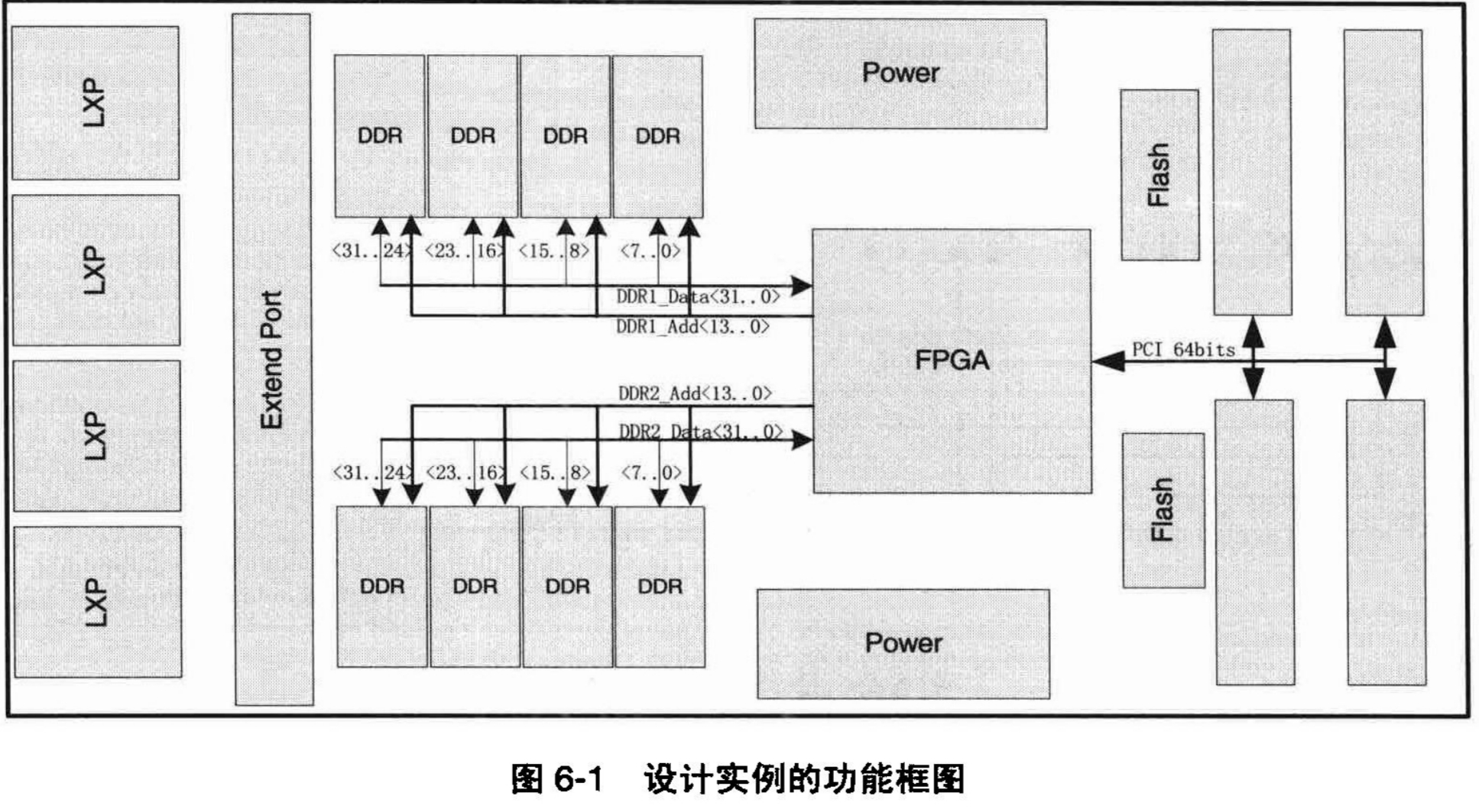

言归正传,我们回到本书的内容上来,来看看我们面临的任务是什么。参照图 6-1,这是个非常简单的功能框图,读者可以打开已经调入网表的 PCB 文件 “Booksi_Demo_Allegro160_UnRouted.brd” 进行对照理解。我们要完成的这个设计,是一个信号处理子板,FPGA 作为这个子板的主要器件,负责信号处理及和主机板进行数据交换。外部信号通过光电转换,通过 RocketIO 高速数字接口,进入 FPGA,FPGA 对接收的信号进行运算,以两组 DDR 作为缓存,该子板和主机板通过 64 位 VME-CPCI 接口相连。这是一个通用的数字信号处理平台的架构。

在这个设计中,我们并不是要实现所有的设计。为了能够让读者掌握高速电路设计方法和 Cadence 高速设计流程,我们仅仅对 DDR 部分进行详细的设计分析和实现。从图 6-1 中可以看到,该设计中,DDR 分为两组,功能和结构都相同,所以我们可以只对其中一组进行设计分析,然后将仿真设计分析结果,以及高速设计约束不加修改地应用到第二组 DDR 设计中。

6.2 DDR 设计分析

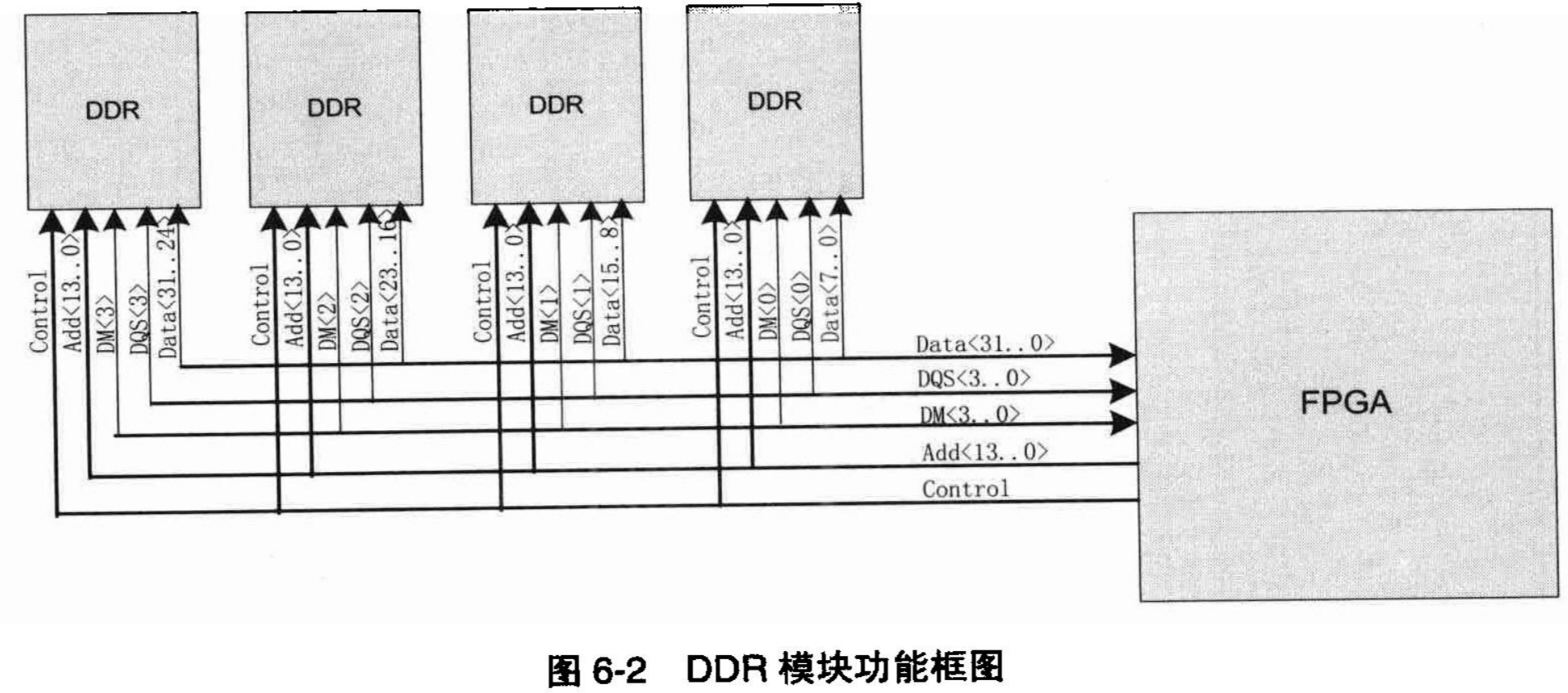

为了读者能够更好地理解 DDR 设计需求,在图 6-2 中,是对其中一组 DDR 功能模块的细化框图。在这个系统中,对 DDR 的设计需求如下。

- 整个 DDR 功能模块由四个 512MB 的 DDR 芯片组成,选用 Micron 的 DDR 存储芯片 MT46V64M8BN-75。每个 DDR 芯片是 8 位数据宽度,构成 32 位宽的 2GB DDR 存储单元,地址空间为 Add<13..0>,分四个 Bank,寻址信号为 BA<1..0>。

- 每个 DDR 芯片独享 DQS、DM 信号,四片 DDR 芯片共享 RAS#、CAS#、CS#、WE#控制信号。

- DDR 工作频率为 133MHz。

- DDR 控制器选用 Xilinx 公司的 FPGA,型号为 XC2VP30_6FF1152C。

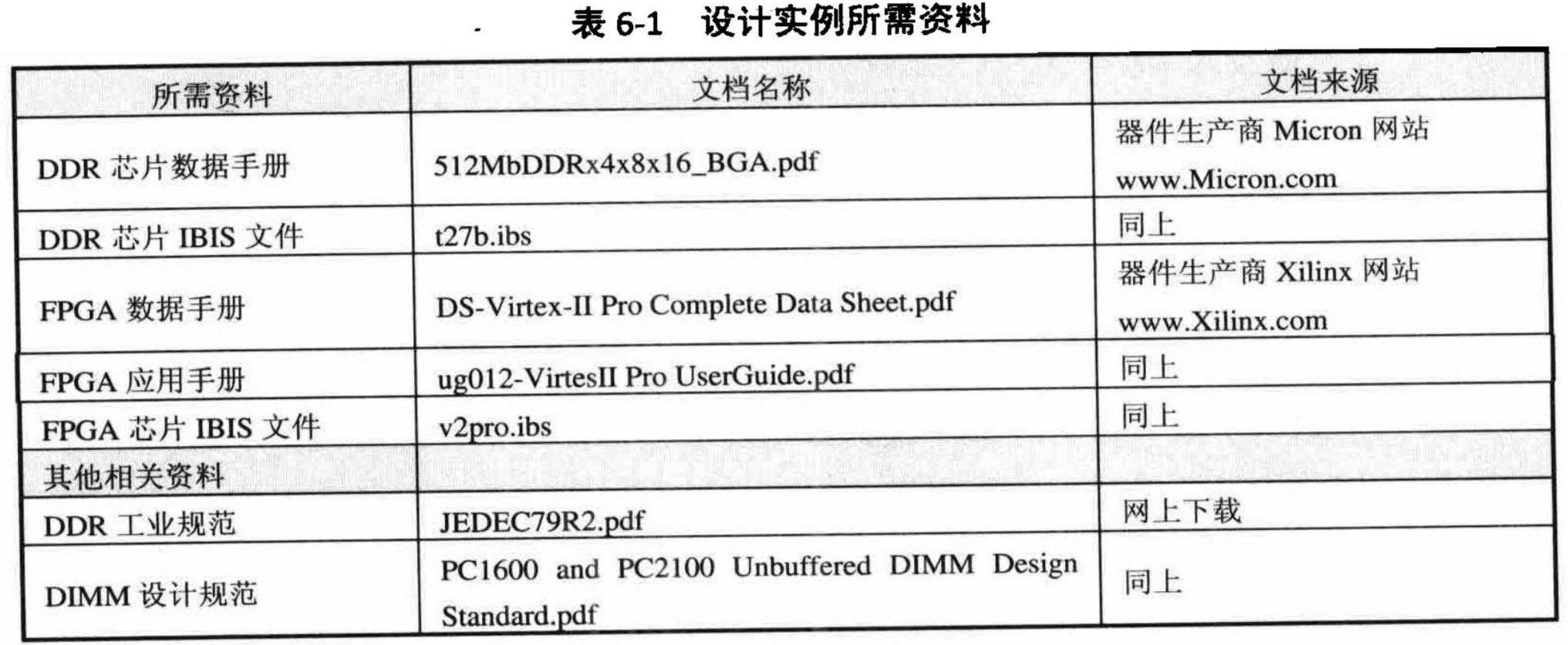

得到这个设计需求之后,我们首先要进行器件选型,然后根据所选的器件,准备相关的设计资料。一般来讲,对于经过选型的器件,为了使用这个器件进行相关设计,需要有如下资料。

- 器件数据手册 Datasheet:这个是必须的。如果没有器件手册,是没有办法进行设计的(一般经过选型的器件,设计工程师一定会有数据手册)。

- 相关器件的应用手册,Application Note:在这个文档中,厂家一般会提出一些设计建议,甚至参考设计,有时该文档也会作为器件手册的一部分出现在器件手册文档中。但是在资料的搜集和准备中,要注意这些信息是否齐备。

- 参考设计,Reference Design:对于比较复杂的器件,厂商一般会提供一些参考设计,以帮助使用者尽快实现解决方案。有些厂商甚至会直接提供原理图,用户可以根据自己的需求进行更改。

- IBIS 文件:这个对高速设计而言是必需的,获得的方法前面已经讲过。

- 工业规范标准,Specification:如果所设计的功能模块要实现某种工业标准接口或者协议,那一定要找到相关的工业规范标准,读懂规范之后,才能开始设计。

因此,为实现本设计实例中的 DDR 模块,需要表 6-1 中的技术资料和文档。

由于我们要设计 DDR 存储模块,那么在所有的资料当中,应该最先了解 DDR 规范。通过对 DDR 规范文件 “JEDEC792.pdf” 的阅读,我们了解到,设计一个 DDR 接口,需要满足规范中规定的 DC、AC 特性及信号时序特征。下面我们从设计规范要求和器件本身特性两个方面来解读,如何在设计中满足设计要求。

需要注意的是,由于技术的更新,在本设计实例中所使用的器件可能已经过时,这里仅做技术讲解之用。如果读者想获得最新的产品信息,包括器件手册和方针模型,请登录器件厂商的网站获得。

6.2.1 DDR 规范的 DC 和 AC 特性

众所周知,对于任何一种接口规范的设计,首先要了解其 DC 和 AC 特性要求,DDR 也不例外。

在 DDR 规范文件 “JEDEC79R2.pdf” 的第 51 页 “TABLE 6: ELECTRICAL CHARACTERISTICS AND DC OPERATING CONDITIONS”中对 DDR 的 DC 有明确要求:VCC=+2.5V±0.2V,Vref=+1.25V±0.05V,VTT=Vref±0.04V。

在我们的实际设计中,除了要精确设计供电电源模块之外,还需要对整个电源系统进行 PI 仿真,而这是高速系统设计中另一个需要考虑的问题,在这里我们先不讨论它,暂时认为系统能够提供稳定的供电电源。

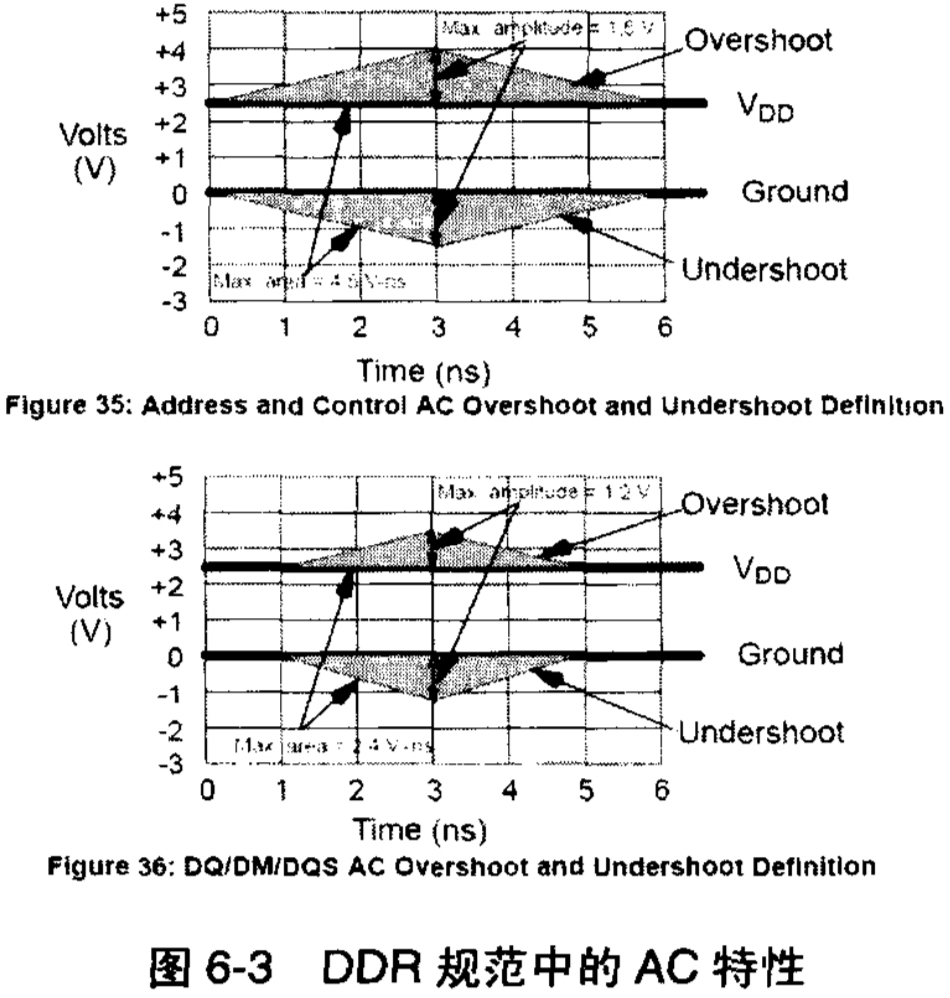

除 DC 特性外,我们还应该注意规范中提到的 AC 特性,所谓 AC 特性,就是信号在高速翻转状态下所表现出的动态变化特性。DDR 规范中第 60 页,对处于动态变化的地址信号、控制信号及数据信号分别给出了交流特性的要求。为方便读者,现把规范中对于信号交流特性的要求复制到这里,如图 6-3 所示。作为高速设计的一部分,要确保在我们的系统中,所有处于高速工作状态下的 DDR 信号要符合这个 AC 特性规范。

6.2.2 DDR 规范的时序要求

在明确了规范中的 DC 和 AC 要求之后,下一步,我们还应该了解规范中对于信号的时序要求。这是我们所设计的 DDR 系统能够正常工作的基本条件。

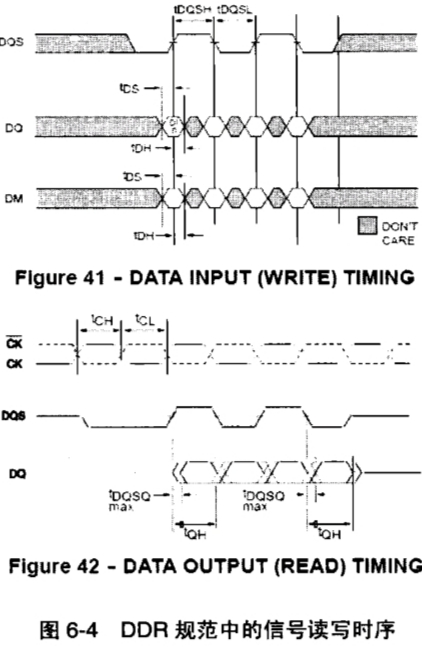

在规范文件中,有很多时序图,作者大致计算了一下,有 40 个左右。作为高速电路设计的工程师,我们不可能也没有时间去做全部的仿真波形来和规范的要求一一对比验证,那么哪些时序图才是我们关注的重点?事实上,在所有的这些时序图中,作为 SI 工程师,我们需要关注的只有两个,那就是规范文件的第 69 页,关于数据读出和写入两个最基本的时序图(注意,这里的读出和写入是从 DDR 控制器,也即 FPGA 的角度来讲的)。为方便读者阅读,作者把这两个时序图拼在了一起,如图 6-4 所示,而其他时序图的实现都是以这两个图为基础的。在板级系统设计中,只要满足了这两个时序图的质量,其他的时序关系要求都是对这两个时序图逻辑功能的扩展,应该是 DDR 控制器的逻辑设计人员所需要考虑的事情。

请读者注意,这两个图有其特殊含义,也是 DDR 体系结构的具体体现。而遗憾的是,在作者接触过的很多高速电路设计人员中,很多人还不能说清楚这两个图的含义。在数据写入(Write)时序图中,所有信号都是 DDR 控制器输出的,而 DQS 和 DQ 信号相差 90° 相位,因此 DDR 芯片才能够在 DQS 信号的控制下,对 DQ 和 DM 信号进行双沿采样;而在数据读出(Read)时序图中,所有信号是 DDR芯片输出的,并且,并且(这不是笔误,是强调)DQ 和 DQS 信号是同步的,并且都是和时钟沿对齐的!这时候为了要实现对 DQ 信号的双沿采样,DDR 控制器就需要自己去调整 DQS 和 DQ 信号之间的相位延时!这也就是 DDR 系统中比较难以实现的地方。DDR 规范这样做的原因很简单,是要把逻辑设计的复杂性留在控制器一端,从而使得外设(DDR 存储芯片)的设计变得简单而廉价。因此,对于 DDR 系统设计而言,信号完整性仿真和分析的大部分工作,实质上就是要保证这两个时序图的正确性。

那么在下面的仿真分析过程中,我们是不是可以就以这两个图中的时序要求作为衡量标准来进行系统设计呢?答案是否定的,因为虽然这个时序是规范中定义的标准,但是在系统实现中,我们所使用的是 Micron 的产品,而最后系统是否能够正常工作要取决于我们对 Micron 芯片的时序控制程度。所以虽然我们通过阅读 DDR 规范文件了解到基本设计要求,但是具体实现的参数指标要以 Micron 芯片的数据手册为准。换句话说,DDR 的工业规范是芯片制造商 Micron 所依据的标准,而我们设计系统时,既然使用了 Micron 的产品,那么系统的性能指标分析就要以 Micron 的产品为准。所以,接下来的任务就是我们要在 Micron 的 DDR 芯片手册和作为控制器的 FPGA 数据手册中,找到类似的 DDR 规范的设计要求和具体的设计参数。

6.2.3 DDR 芯片的电气特性和时序要求

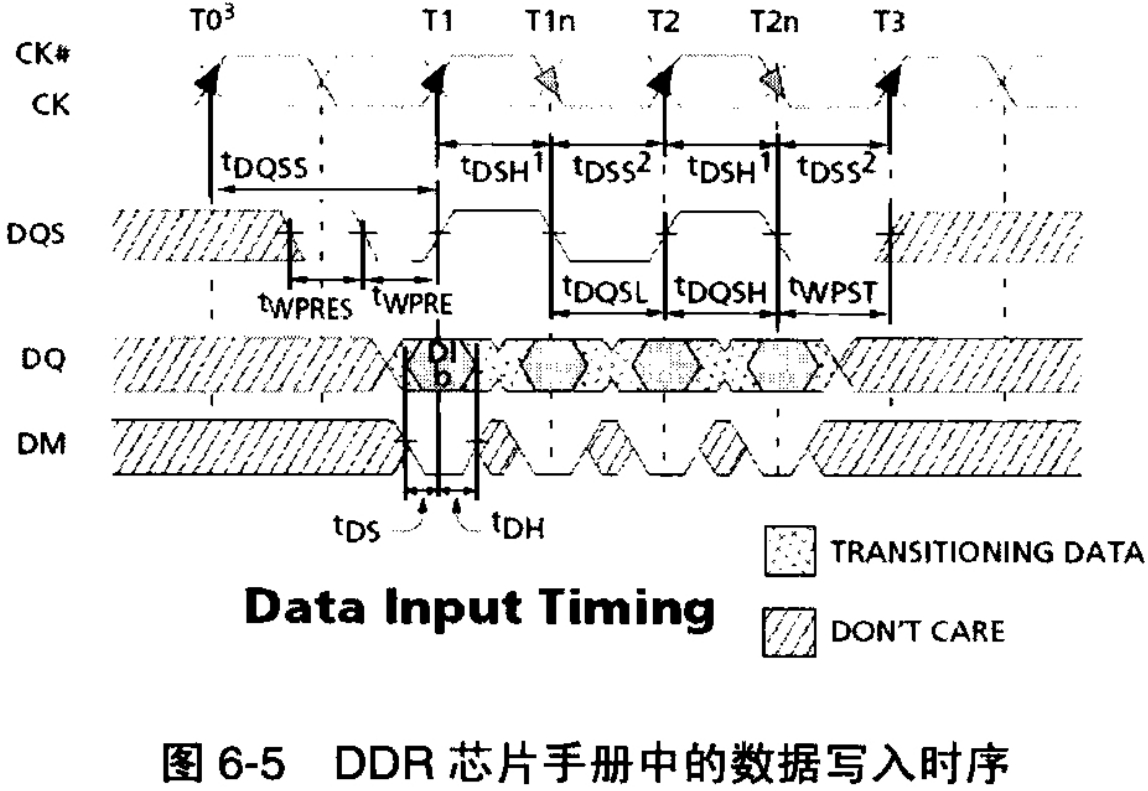

按照上一小节中最后的结论,我们需要在 DDR 芯片的数据手册中找到和 DDR 规范中电气和时序要求相符的内容,按照这个思路去阅读 DDR 器件的数据手册,读者不难找到,在 DDR 芯片手册的第 70 页的关于 DDR 数据写入的时序图,如图 6-5 所示。

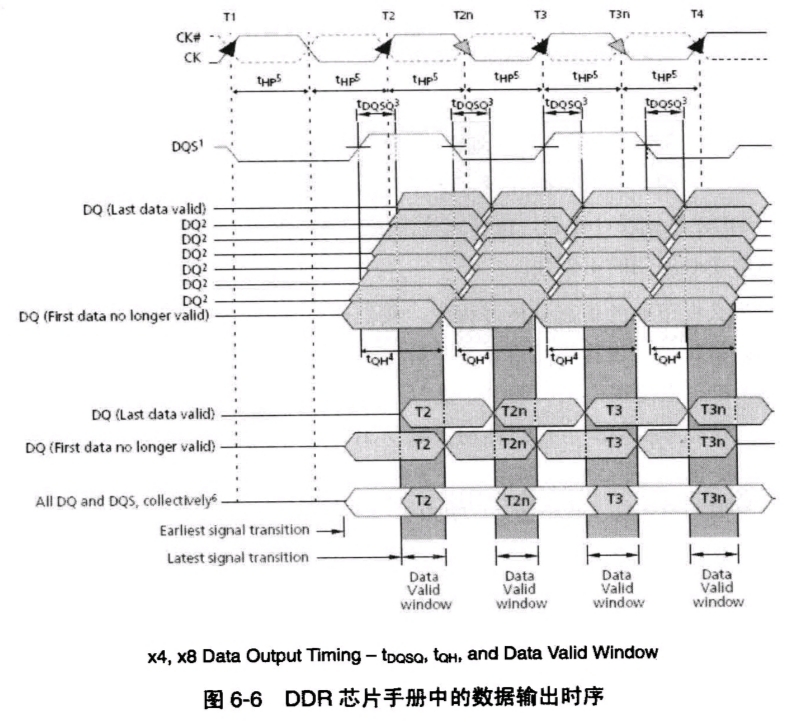

而在手册 67 页,可以找到数据输出时序图,如图 6-6 所示。

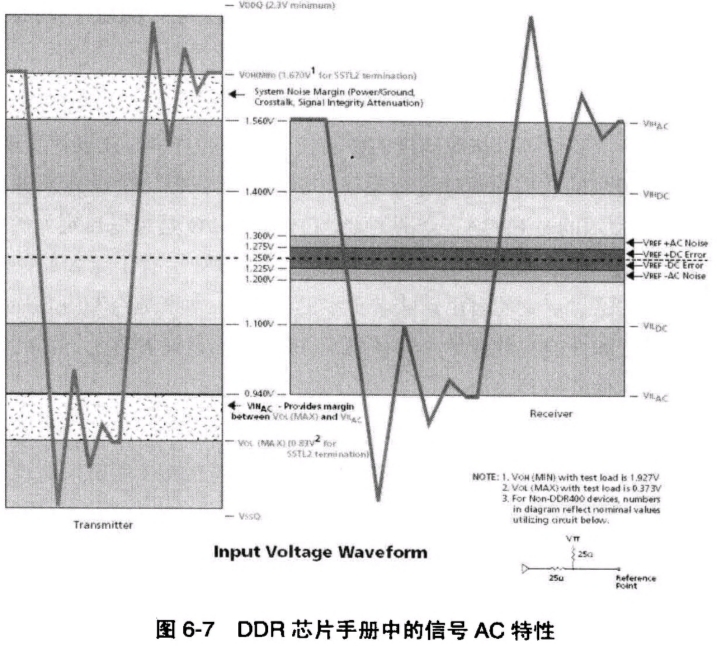

除了这两个时序图之外,我们还需要考察 DDR 芯片的 DC 和 AC 特性。前面我们讲过,对于 DC 特性,我们目前只能通过仔细设计电源模块,假设其符合规范要求,具体性能需要通过电源完整性分析进行验证。因此,在这里,我们只需要关心信号 AC 特性的要求,在 DDR 芯片手册的第 48 页有对 AC 特性描述的内容,如图 6-7 所示。

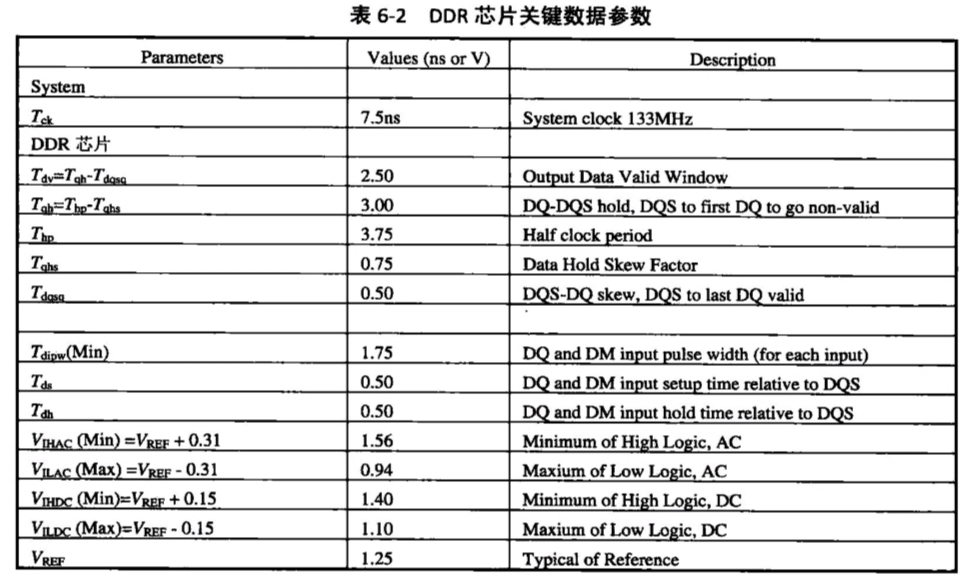

在找到 DDR 芯片的 AC 特性和时序特性要求的内容之后,需要仔细对图中的内容进行解读,并且需要了解该图中各参数的含义和具体指标。因此,读懂上述几个关键波形之后,还需要在数据手册中找到对应参数的具体要求,在 DDR 的手册中,位于第 59 页的表格 “Table 25: Electrical Characteristics and Recommended AC Operating Conditions(-75Z/-75)” 就是对各参数的描述及其指标的具体要求。为了方便下面的仿真分析工作,我们用表格的形式把 DDR 芯片中的关键参数记录下来,这也是一个很好的工作习惯,以免在需要时不停地查找数据手册。DDR 中关于数据读写的关键时序及电气参数,如表 6-2 所示。

6.2.4 DDR 控制器的电气特性和时序要求

上一小节中,我们在 DDR 芯片的器件手册中找到并记录了关键数据。接下来,我们需要对 DDR 控制器做同样的数据分析工作,以确保 DDR 控制器和存储芯片能够在一个系统中配合工作。

在一个 DDR 系统中,如果 DDR 控制器也是一个类似于 DDR 存储芯片那样的商用芯片的话,我们可以按照同样的做法找到需要的资料。在设计实现的过程中,按照资料中提供的数据对设计进行验证。然而对于我们这个设计来讲有些特殊,DDR 控制器使用的是 FPGA。众所周知,FPGA 的 IO 是可以自定义的,逻辑是可以动态配置的,看起来我们有了更多的自由,在设计上有了更大的灵活性,但是不要忘了那句话 “更大的自由意味着更多的责任”,本来是由专用芯片负责的一些功能逻辑设置和性能参数计算,转移到了 FPGA 的设计者身上。因此,我们在使用 FPGA 的时候要格外小心。

首先我们要确定在 FPGA 中所使用的 IO 逻辑,按照 DDR 的规范要求,我们应该选择 2.5V 的 SSTL_2C/SSTL_2 Compatible 标准的 IO 逻辑,这也就确定了我们将来做仿真分析器件的模型。

然后,按照阅读 DDR 芯片手册的方法,我们需要在 FPGA 的数据手册 120 页中找到 “Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics”,这就是 FPGA 中关于各种 IO 逻辑的电气特性和开关特性(开关特性也即 AC 特性)的描述。在这一节中,还有一个子标题 “Source-Synchronous Switching Characteristics”,这个正是我们要找的针对于 SSTL_2C 的接口特性参数。通过这一小节的内容后,读者应该能发现文章的重点在于 “Source Synchronous Timing Budgets”,这就是我们在 FPGA 和存储芯片之间实现 DDR 协议的时序保证,也是我们前面所讲的,DDR 时序规范在 FPGA 实现上的具体要求。

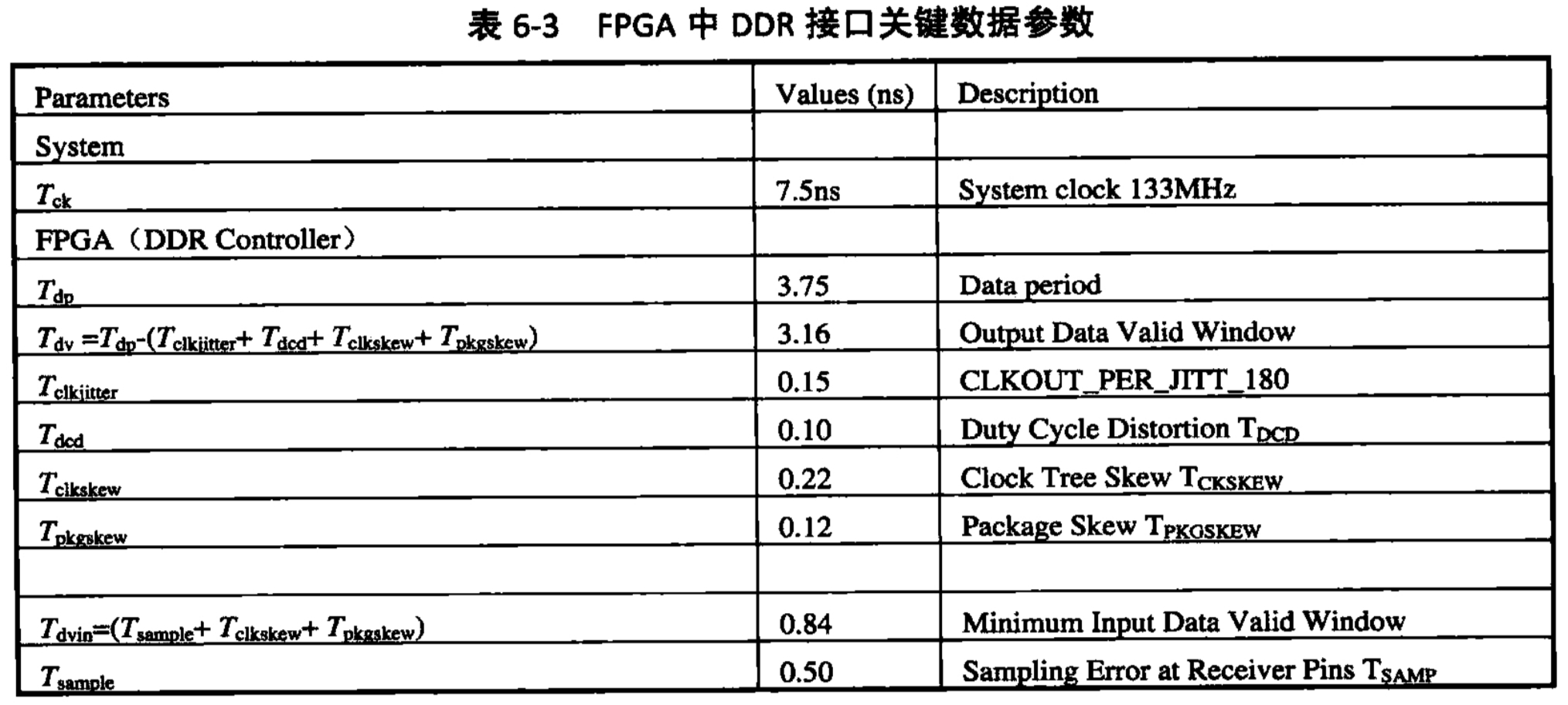

按照上一小节的方法,我们把找到的关键数据信息,按照 DDR 的时序做个基本的运算后列举如表 6-3 所示,以方便我们后续的信号仿真分析工作。

现在,我们通过对 DDR 规范、DDR 芯片的数据手册,以及作为 DDR 控制器的 FPGA 数据手册的阅读和总结,得到了要实现一个工作时钟频率为 133MHz 的 DDR 模块所需要满足的设计要求。我们的最终设计目标是要实现 DDR 芯片到 FPGA 的板级互连,而且这种互连需要保证满足 DDR 芯片及 FPGA 对于时序的要求。因此,我们做仿真分析的目的就是在进行实际的 PCB 布线之前,确保设计方案的正确性。明确了工作任务之后,我们就开始着手实际的设计工作。在以下章节的讲解过程中,建议读者准备好表 6-1 中所列举的设计资料,以及 Cadence 软件,我们来同步完成这个设计。

请读者注意,在下面的设计实现过程中,我们将完全按照 Cadence 的高速设计流程来进行,如果对这个设计流程及工具的使用还有疑问的话,建议读者重新阅读本书第 5 章的所有内容,有必要的话再练习一下工具软件的使用。因为在下面的讲解过程中,我们将重点放在设计实现过程和问题的分析解决上,而不是带领读者去熟悉软件的使用。

6.3 仿真库的建立

在前面的资料准备中,我们已经得到了 DDR 芯片和 FPGA 的 IBIS 模型文件,“127b.ibs” 和 “v2pro.ibs”,这两个文件都是可以从芯片厂商的网站上下载得到的。作为高速电路设计流程的第一步,我们需要用 Model Integrity 对这两个模型文件的正确性进行验证,并把它们转换成 Cadence 所需的 DML 模型库。

6.3.1 DDR 芯片的 IBIS 文件处理

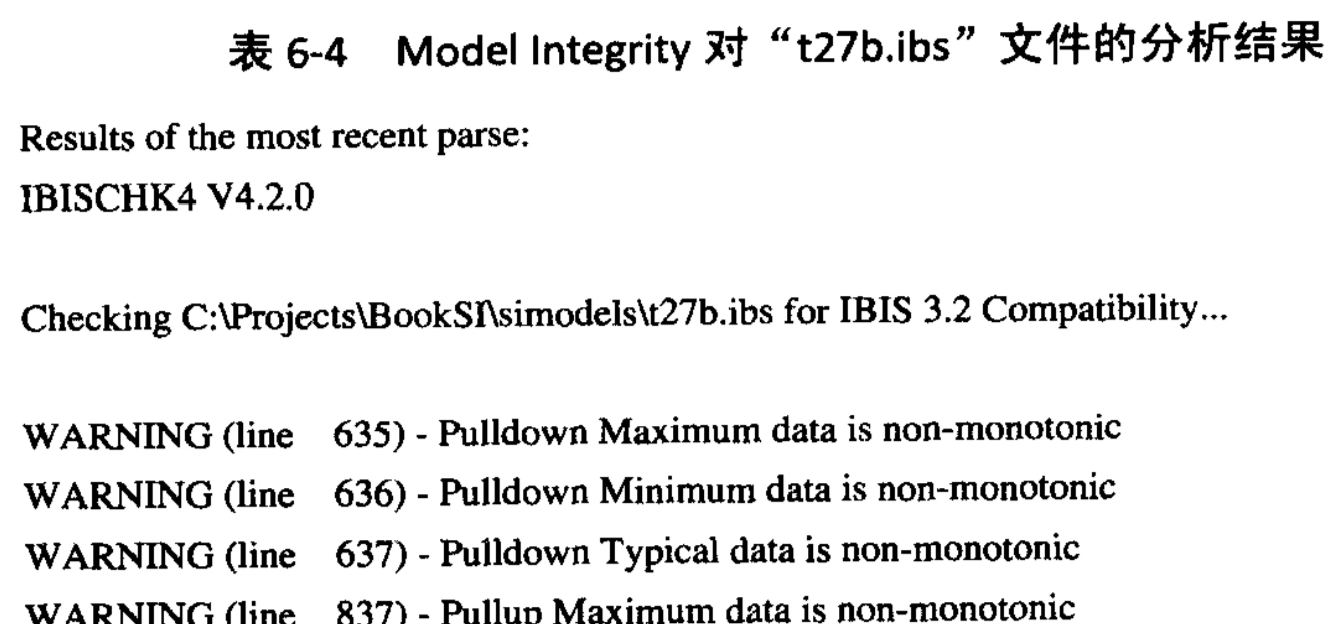

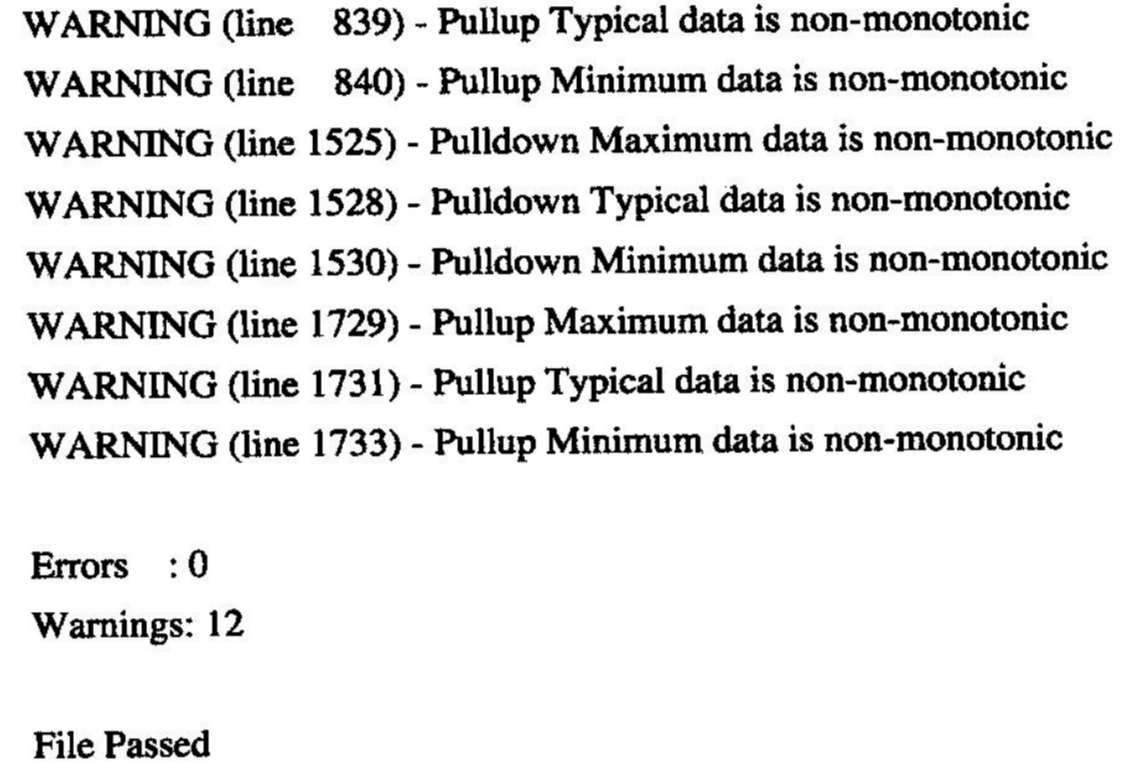

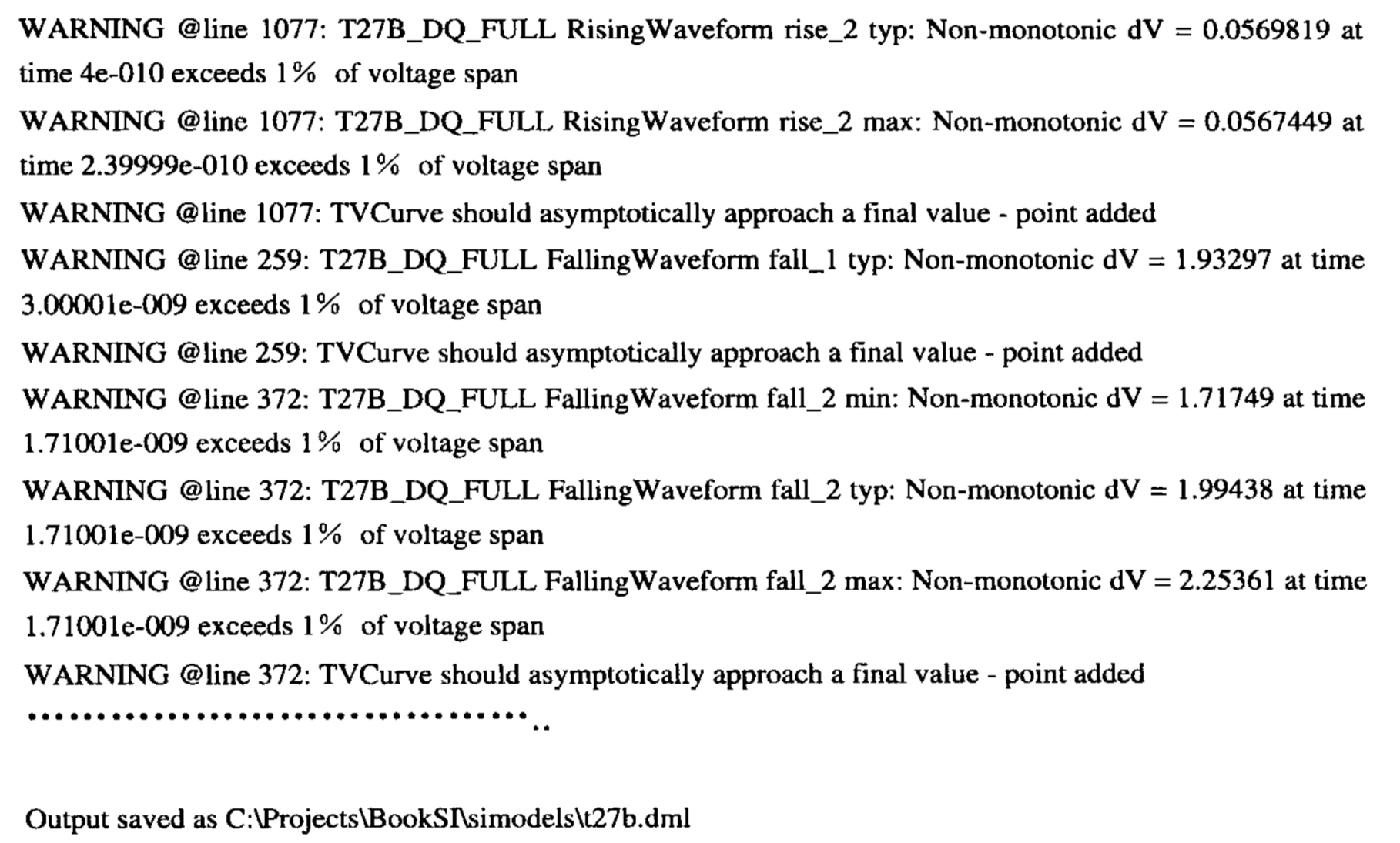

我们首先对 “127b.ibs” 文件进行处理,因为这个文件比较小,我们猜想遇到的问题不会多,处理起来也不会太复杂,所以先从简单的模型开始。在 Model Integrity 中打开这个文件之后,软件下半部的 “Parse Messages” 区域就会自动显示 Model Integrity 对这个文件的分析结果,如表 6-4 所示。

从最后几行可以看出,分析结果是成功的,没有发现错误,文件内容被接受,也就意味着这个文件可以被转换成 DML 文件,并在 Cadence 的仿真分析软件里使用。但是这个 IBS 文件中存在 12 个 Warning,为了让读者了解更多的 IBIS 知识,也为了确保随后的仿真结果的正确性,我们有必要对这些警告信息进行解读。

通过对这些 Warning 进行解读,我们发现这些 Warning 都是同一类错误,XXXX data is non-monotonic,也就是说这些数据具有非常规性,而且都出现在 Pullup 和 Pulldown 曲线中。为了搞清楚这些 Warning 的严重性,它们到底会不会影响我们高速信号的仿真分析结果,我们按照提示信息的指示到原文件中定位 Warning 的数据来源。我们先找到 635 行的位置,如图 6-8 中 “1” 标记所示。

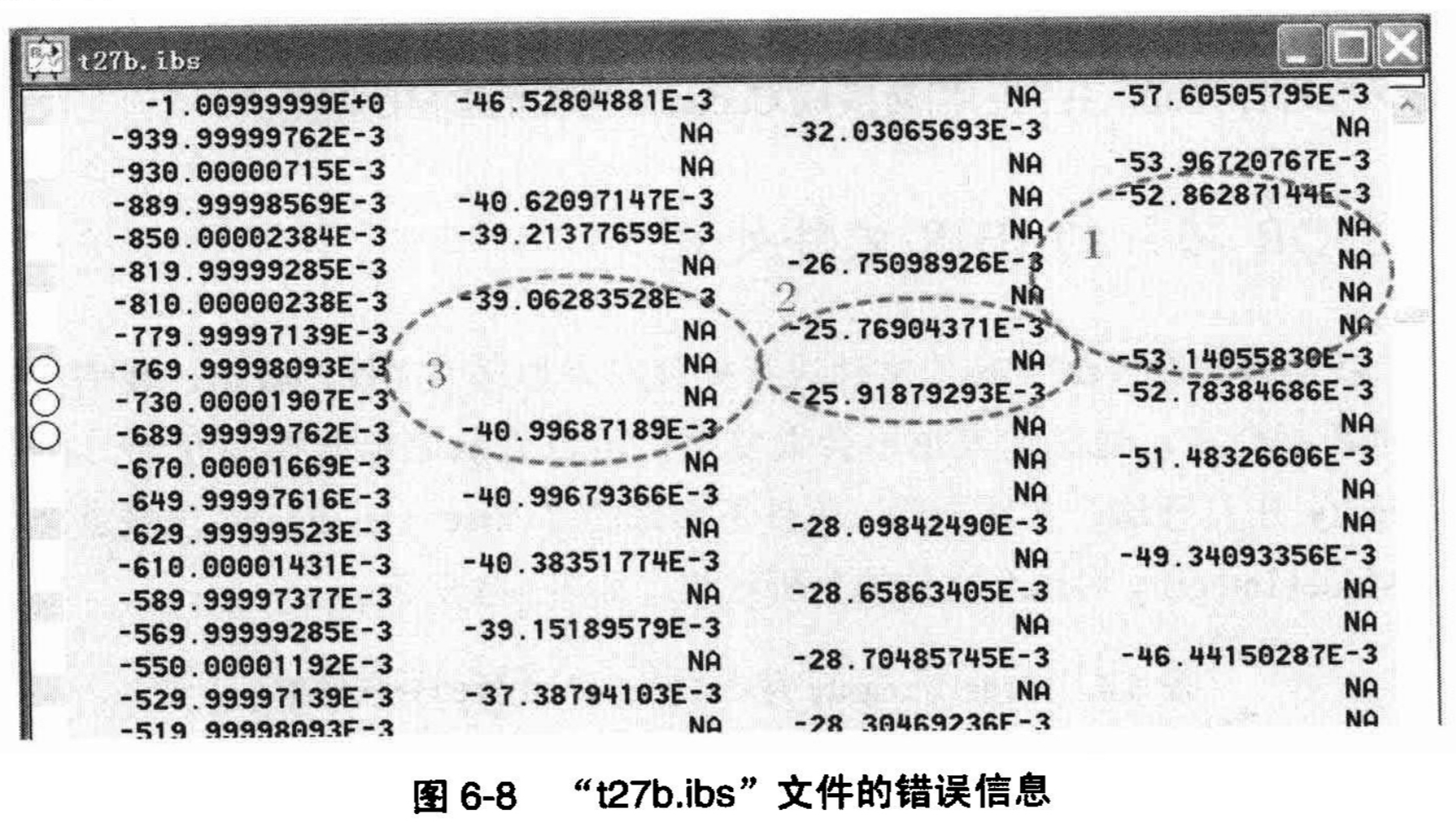

635 行的数据是 “-53.14055830E-3”,按照变化趋势,在它上面最近的那个有效数据 “NA” 不是有效数据行,即 629 行的值应小于这个值,可是 629 行的数据是 “-52.8628714E-3”,这就出现了数据单调性的错误。同样道理如图中 “2” “3” 标记处,就是 636 行和 637 行的两个警告性错误。那么这个错误会不会影响仿真结果的准确性呢?答案是不会的,因为我们已经讲解过 IBIS 模型的原理,IBIS 模型是一种抽象的理想化的模型,在理论上它要求 V/I 数据的单调性,但是由于实际器件的参数不一致性,或者测量的精度误差,在实际测量中会有些很小的偏差,但是这种偏差不影响曲线整体的单调性,所以像这样很细小的非单调性,我们完全可以忽略掉。另外,为了验证我们的分析结果,可以通过图形直观地看一下在“Model|DQ_FULL”下的 Pulldown 曲线,如图 6-9 所示。图中箭头所指之处就是非单调性发生的位置。从整个波形的趋势来看,这几个非单调性 Warning 确实不会影响整个曲线特性。同理,我们可以对其他几个非单调性 Warning 做出同样的结论。本书中就不一一列举,留给读者去分析数据观察波形。

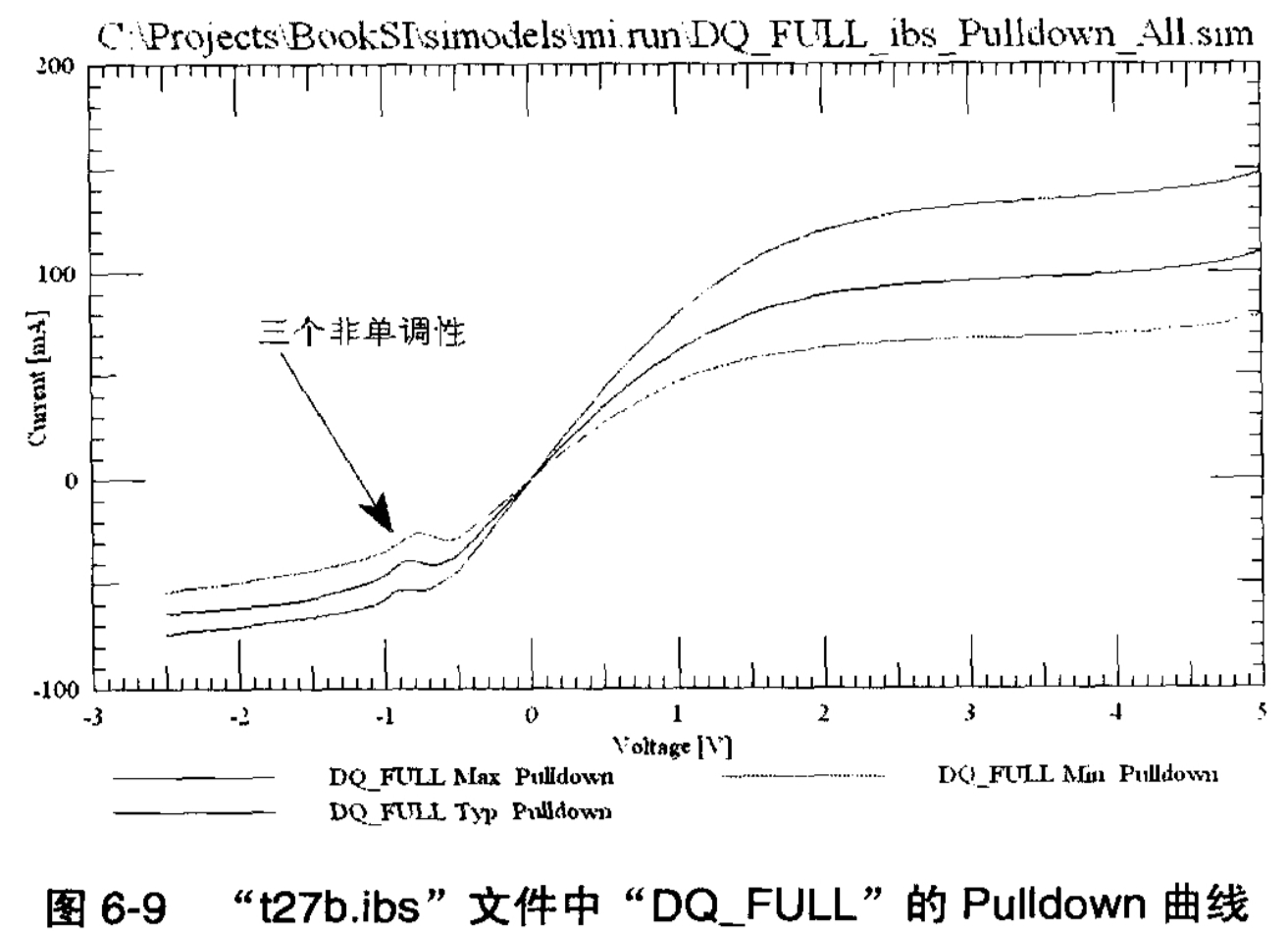

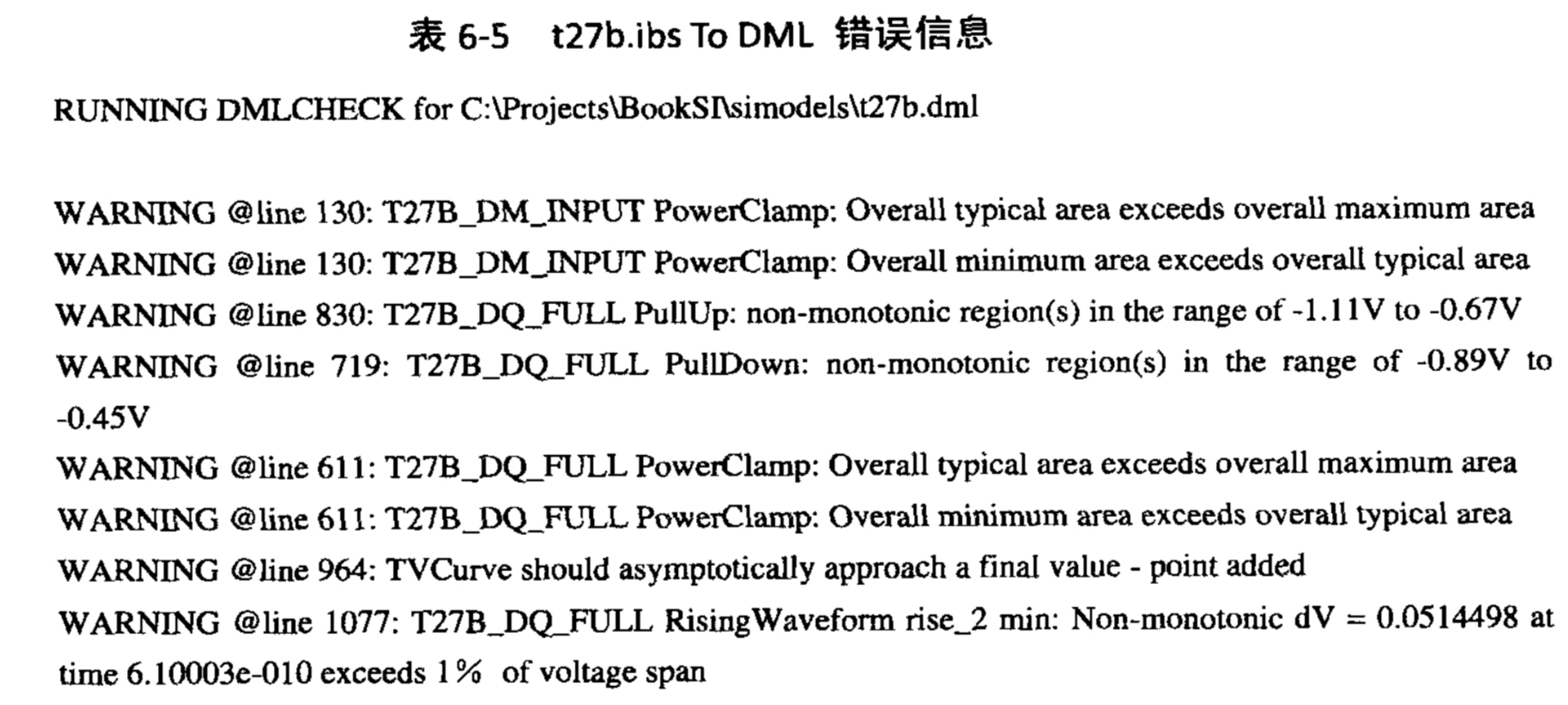

在得到这个结论之后,我们就可以通过 “Tools→IBIS→To DML” 命令,把当前这个 IBIS 文件转换成 DML 文件,在对 “127b.ibs” 文件进行转换时,Model Integrity 下部的 “Log File” 窗口中,又出现了很多警告信息,我们一起来看看是什么样的警告。由于内容太多,对于出错信息,在这里只截取一部分内容显示,如表 6-5 所示。

对于上面的众多错误信息,可以分为以下几类进行分析讲解,其他信息参考这里的分类进行理解。

- “Overall typical area exceeds overall maximum area”,此类信息是出自 IBIS 文件的定义。IBIS 的规范要求,在 Min、Typical 和 Max 三个测量条件下,所测量的电压范围应该保持一致,也就是说 Typical 测量的是 -3V 到 +6V 之间的电压范围,那么另外两种条件下测量范围也应该是 -3V 到 +6V 之间,并且两个端点,-3V 和 +6V 这两个测量值,不能是 NA。

- “non-monotonic region(s) in the range of ...”,这个警告的起因和处理方法在前面已经讲过了,生成 DML 时无非是对同样的错误再一次检查。

- “TVCurve should asymptotically approach a final value - point added”,曲线的采样点不够,没有达到测量范围,软件会根据 V/T 曲线自动进行估值,把数据补充完整。

其他的信息都是这三类警告的重复,读者可详细阅读 LOG 文件,对所有的出错信息进行对比检查。在对以上这些出现在 DML 转换过程中的警告信息进行分析后,我们发现 DML 转换最终还是会成功的,而且根据我们的理解,这些错误警告并不影响仿真结果。所以我们接受这个 DML 把它存储起来并记下存储路径。在后面的流程中,我们需要把这个 DML 文件添加到仿真库中。

6.3.2 FPGA 的 IBIS 模型文件处理

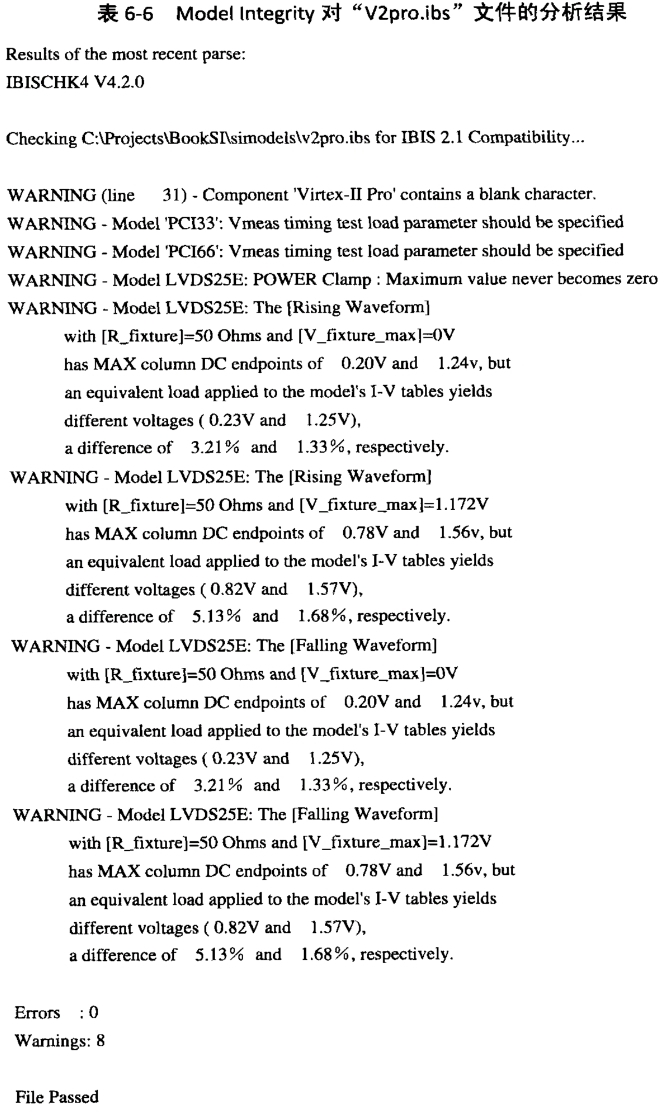

现在,我们开始处理 FPGA 的 IBIS 文件 “v2pro.ibs”。首先,还是在 Model Integrity 中打开这个文件进行 IBIS 解析,结果如表 6-6 所示。

这里的错误类型比较多,我们一一来分析。

-“WARNING (line31)- Component 'Virtex-II Pro' contains a blankcharacter.",这个错误很简单,就是要求器件名称中不能有空格,而这里在 P 字母之前有个空格。这个错误可以忽略掉。因为在转换成 DML 时,软件可以自动更改这个错误。

- “WARNING - Model PCF33: Vmeas timing test load parameter should be specified” 是说,对于 Model PCF33,缺少了一个测量电压 Vmeas 的定义。Vmeas 是 SigXP 中用来测量 Switch-Settle Delay 的参数,但它在 IBIS 模型中不是必需的。如果器件模型中没有这个参数的定义,那么 SigXP 就不能自动测量 Switch-Settle Delay。所以,如果读者在意这个测量,那么可以在修改 IBIS 文件加入 Vmeas 值,或者在 SigXP 的测量设置中加入 Vmeas 参数。

- “WARNING - Model LVDS25E: POWER Clamp: Maximum value never becomes zero.” 简单讲过,IBIS 是理想模型,所以它要求当对器件施加的电压为 0 时,相应 V/T 曲线的 I 值也应该是 0。也就是我们常说的 V/T 曲线过原点的问题。但是这个文件中,Model LVDS25E 的 POWER Clamp 数据中,I(max) 的值在 voltage=0 时,还有 3.2770uA,所以 Model Integrity 会报这个错。实际使用中可以不理睬这个警告,也可以手动更改 I(max) 的值,小于 0.1uA 后,就不会再报这个警告了。

- “WARNING - Model LVDS25E: The [Rising Waveform]...”,这个警告类型就比较复杂了,包括以下的几个警告都是属于同一类型的。这个错误的产生原因比较复杂,涉及 IBIS 模型的测量数据处理机制。这里作者只做简单解释,如果读者想了解更多的内容,请阅读 IBIS 模型关于 COMS 器件模型创建的相关内容。在 IBIS 模型中,尽管对曲线数据进行了分类,比如四个 V/I 曲线,以及两个 V/T 曲线,但是各个曲线之间不是独立的,为保持数据的完整性和一致性,这几个曲线之间可以相互验证。以这个错误为例,V/T 曲线的含义是:在 V/T 曲线中的第一个点,0 时刻开始,这也应该是相应驱动器(具体是哪个驱动器,要看是上升曲线,还是下降曲线)关闭的状态;而 V/T 曲线中的最后一个测量点,应该是该驱动器完全打开的状态,又已知当测量负载 R_fixture=50 Ω 时,在相应的 V/T 曲线中也应该能找到对应的数据点,并且该点的电压、电流值与 V/T 曲线中保持一致。但事实上,由于 V/I 曲线和 V/T 曲线并不是从同一次测量中的数据转换而来的,因此必然会存在一定的误差或不一致的情况。这里警告信息报告的就是两个曲线总数据点不一致的情况。我们可以看一下这个误差的大小,一般在 5%以下,所以这个警告也可以忽略,不影响 IBIS 文件的正确性。

对这些警告信息有了清楚的认识之后,我们就可以放心地使用这个 IBIS 文件了。那么下一个步骤就是把这个 IBIS 文件转换成 DML 文件。和处理 DDR 芯片IBIS 模型文件的步骤一样,在菜单中选择 “Tools→IBIS→To DML” 命令,对 IBIS 文件进行转换。

可是……我们遇到了更多的问题……首先是工具弹出了一个窗口,报告由于错误太多,具体出错位置不在原 IBIS 文件中一一标注,这时单击 “OK” 按钮关闭这个窗口。我们转到 Log 窗口,仔细查看这些错误信息。对于 Log 窗口中的错误警告信息一一检查之后,我们发现,所有的错误类型都能在上一节中找到,在这里就不再重复了。在最后一行可以看到 “Output saved as C:\Projects\Books\Simmodels\V2pro.dml”,说明 DML 文件转换成功,经过适当的路径设置后,就可以在仿真分析中使用了。至此,我们完成了为 DDR 进行仿真分析所需的 IBIS 模型文件处理过程,也希望通过这一部分的介绍读者能够在处理其他器件的 IBIS 模型文件时解决出现的类似问题。

6.3.3 仿真库的建立

在我们对仿真所需要的两个 IBIS 文件进行转换之后,还需要在软件中把转换成的两个 DML 文件加入到仿真库中,否则在器件的模型设置的时候,找不到器件所需的模型,或者在仿真环境中,找不到 I/O 所需的 Buffer 模型。

把仿真库加入到设计中的方法是,在菜单中选择 “Analyze→SI/EMI Sim→Library” 命令,将打开如图 6-10 所示的关于仿真库的设置界面,选择 “Add existing Library→Local Library” 命令把上面已经做好的两个 DML 文件加入到设计中。这样,在随后的器件模型指定或者 I/O 管脚模型定义中就可以使用已经由 IBIS 文件转换好的 DML 模型了。

6.4 仿真条件设置——Setup Advisor

在上一节中,我们已经对设计中需要使用的两个器件的 IBIS 文件进行了转换,并准备好在后续的工作中使用。从这一节开始,我们按照在第 5 章中对 Cadence 高速设计流程的介绍逐步实现这个设计。有条件的读者,现在可以打开 Cadence 的 SPB 设计系统,并打开网上下载的设计文件 “Booksi_Demo_Allegro160_Unrouted.brd”,这是一个未完成 DDR 布线文件,按照本章节中实现高速系统设计的步骤来同步进行操作。

前面讲过,为了方便用户的使用,Cadence 提供了一个对仿真分析进行条件设置的集成环境 Setup Advisor。先请读者在软件中打开 Setup Advisor 环境,我们来完成仿真前的环境和参数设置。

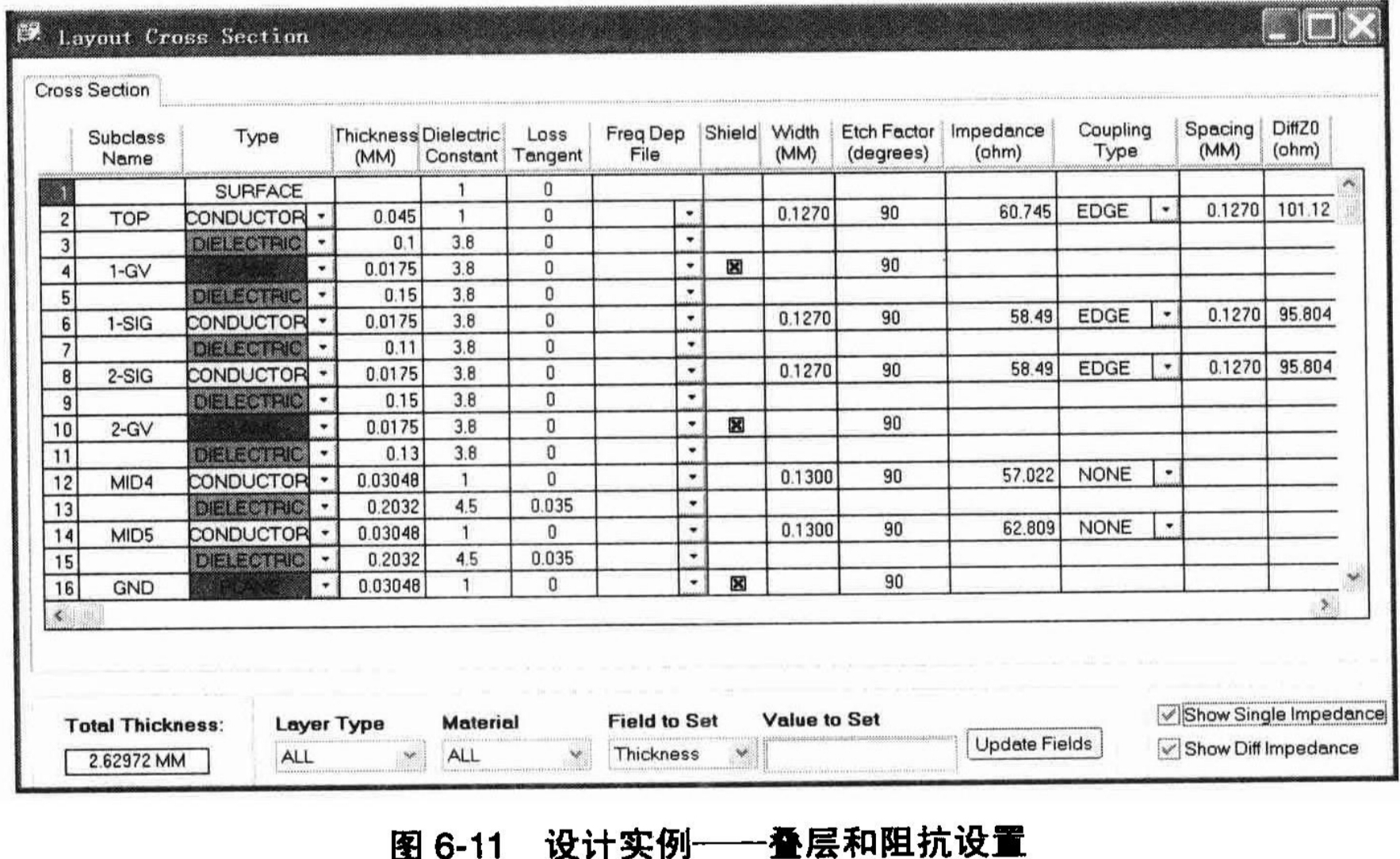

6.4.1 设置叠层和阻抗特性

第一步就是对将要设计的 PCB 设计叠层和阻抗参数设置,具体的参数设置如图 6-11 所示。当打开设计实例文件后,这些参数都已经设计好了,用户可以根据自己的需求进行更改。在 Cadence 软件中,会根据用户输入的各参数,自动对各层的布线阻抗,包括单端阻抗和差分阻抗进行计算。如果读者对于叠层参数如何影响传输线的阻抗特性还有疑问的话,请参考本书 2.4 节对传输线各参数的详细描述。

在我们设置的叠层结构下,传输线的阻抗总体上在 60 Ω 上下变动,所以在下面的前仿真环境中,需要采用 60 Ω 的传输线。可以看到,对于叠层的参数设置,不是按照用户的喜好随意设置的。在确定叠层参数之后,一定要积极和 PCB 生产商联系,按照厂商的工艺条件,对叠层参数和阻抗要求进行复核。有可能需要根据他们提出的一些要求进行更改,以保证设计和现实之间最大程度的吻合。

设置好叠层参数后,单击下一步进入 DC 电压设置。

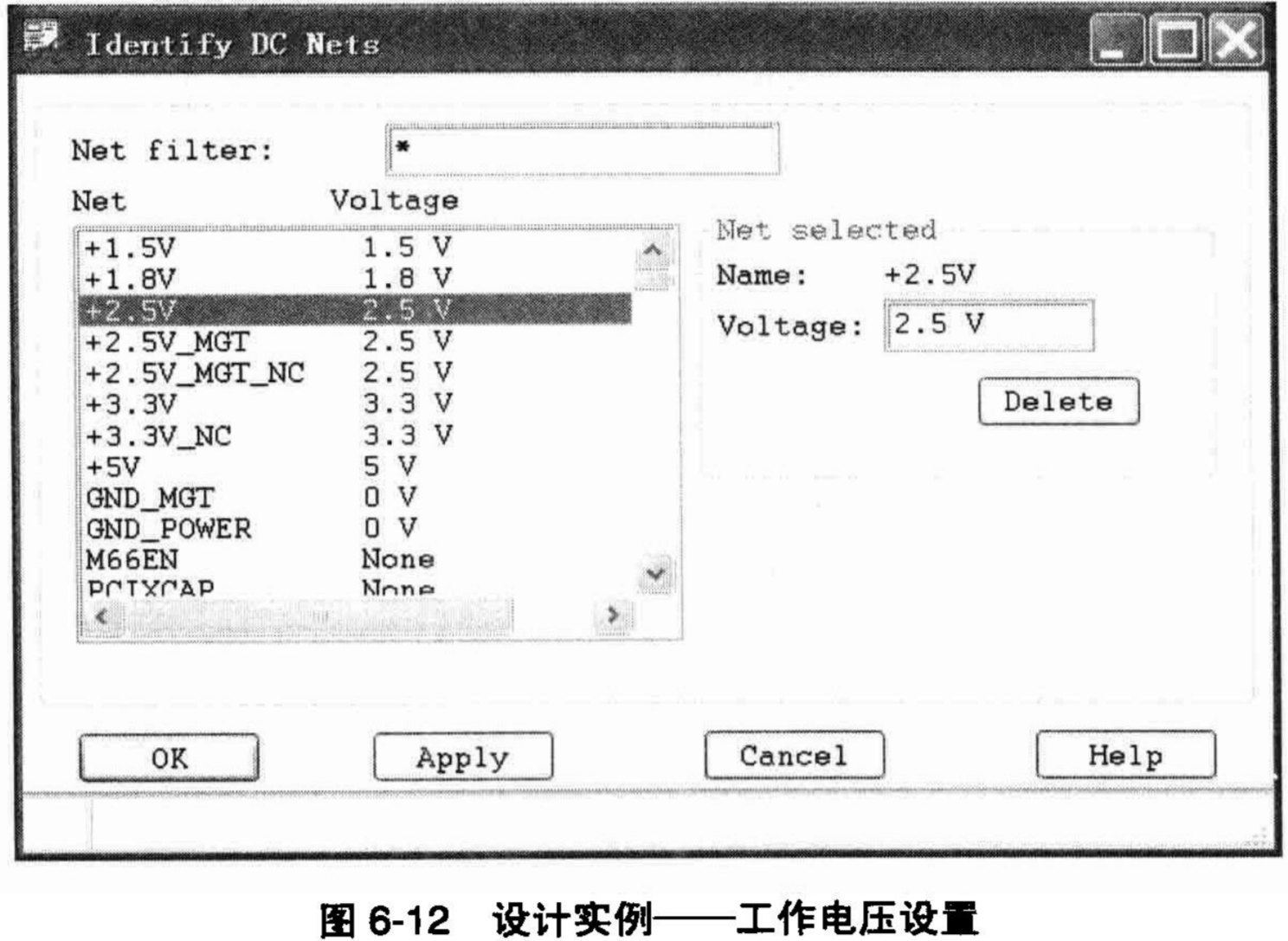

6.4.2 设置电压

对于电压的设置,这里唯一要提醒读者的是,所有在我们仿真中遇到的直流电压,一定要设置正确的工作电压,否则在仿真过程中,可能会由于供电电压引起工作点改变,进而影响器件的正常开关状态,从而导致仿真结果完全不可信。在我们的这个设计实例中,除了要设置图 6-12 中的一些工作电压之外,一定不要忘记还需要设置 DDR 的端接电压 \(V_{TT}\),该电压的网络名称为 \(V_{TDQS}\),按照字母排序,位于整个网络表的后部,因此很容易把它遗忘掉。在网络列表的后部找到 \(V_{TDQS}\) 之后,把电压值设置成 1.25V。用户还可以通过在 “Net Filter” 文本框中设置网络名称的过滤条件,以便能够更快地找到 \(V_{TDQS}\) 这个电压网络。

在本书 5.4.2 节中,我们第一次介绍工作电压的设置时,留给读者一个思考,那就是并不是对设计中的所有工作电压都需要设置。其原因就是,对于仿真分析工作而言,我们只需要设置仿真工作所需的电压即可,和当前仿真网络没有关系的电压可以不用设置。由此可以推出,也并不是对设计中的所有器件都要赋予仿真模型,只设置那些和仿真分析对象相关的器件模型,使得我们能够进行正常的仿真分析即可。

6.4.3 器件类型和模型设置

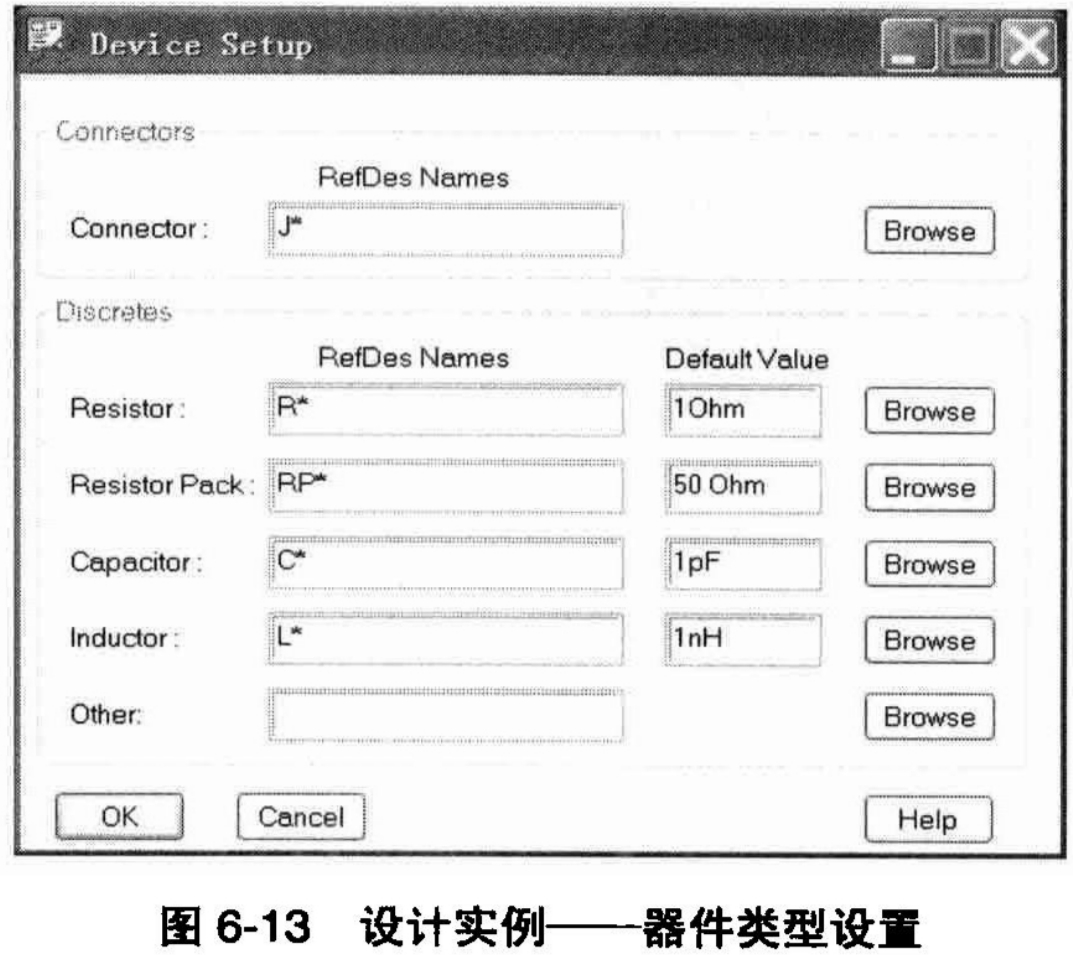

设置好工作电压后,继续进行器件模型设置,如图 6-13 所示的设置界面。这个界面中的参数不建议用户修改,除非你有足够的理由要这么做。另外,即使修改,也绝对不能把默认值改成 0,例如,不能让电容的默认值是 0pF。这样做的话,有可能会使仿真软件算法溢出或者不收敛。对于 0 值的使用,我们通常会用一个很小的值代替,比如 0.01pF。另外,对器件的默认标号字母也不要修改,除非你拿到的网表就是一个特殊的网表,比如非要把电容器件命名为 K123,这纯属个人偏好问题,但不利于交流。

对于读者手中的设计实例,我们还需要加入一个默认的标号类别,即如图 6-13 所示的那样,用 RP*代表阻排 Resistor Pack,默认阻值为 50 Ω。正确地设置器件标号类别,是下一步进行模型设置的基础,马上我们就会讲到。

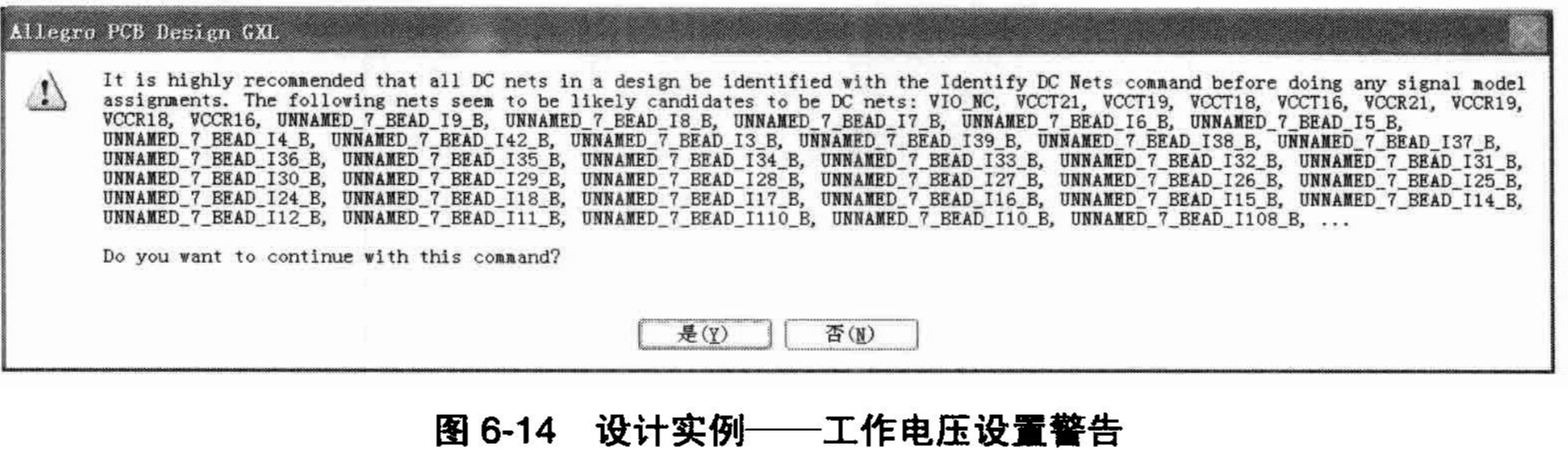

设置好默认的器件类型后,下一步是仿真模型的设置。本例中,单击 “SI Model Assignment” 按钮,软件会弹出如下的警告信息,如图 6-14 所示。在这个提示信息中,软件检查到在设计中,网络都可能是电源网络,但是却没有被设定电压值,所以软件认为这些都是仿真分析中潜在的错误,并建议设计者对所有的电源网络都设定电压值。事实上,我们讲过,我们做的工作仅仅是为了仿真分析,对于仿真分析中没有用到的电压值,就是可以忽略的。所以,对于这个警告提示,我们再一次检查一下,有没有什么电源网络是仿真中需要的而被我们忽略掉的,如果没有,那么可以放心地进行下一步,否则,就需要回到电源电压设计界面,对仿真所需的电源网络重新设置工作电压值。

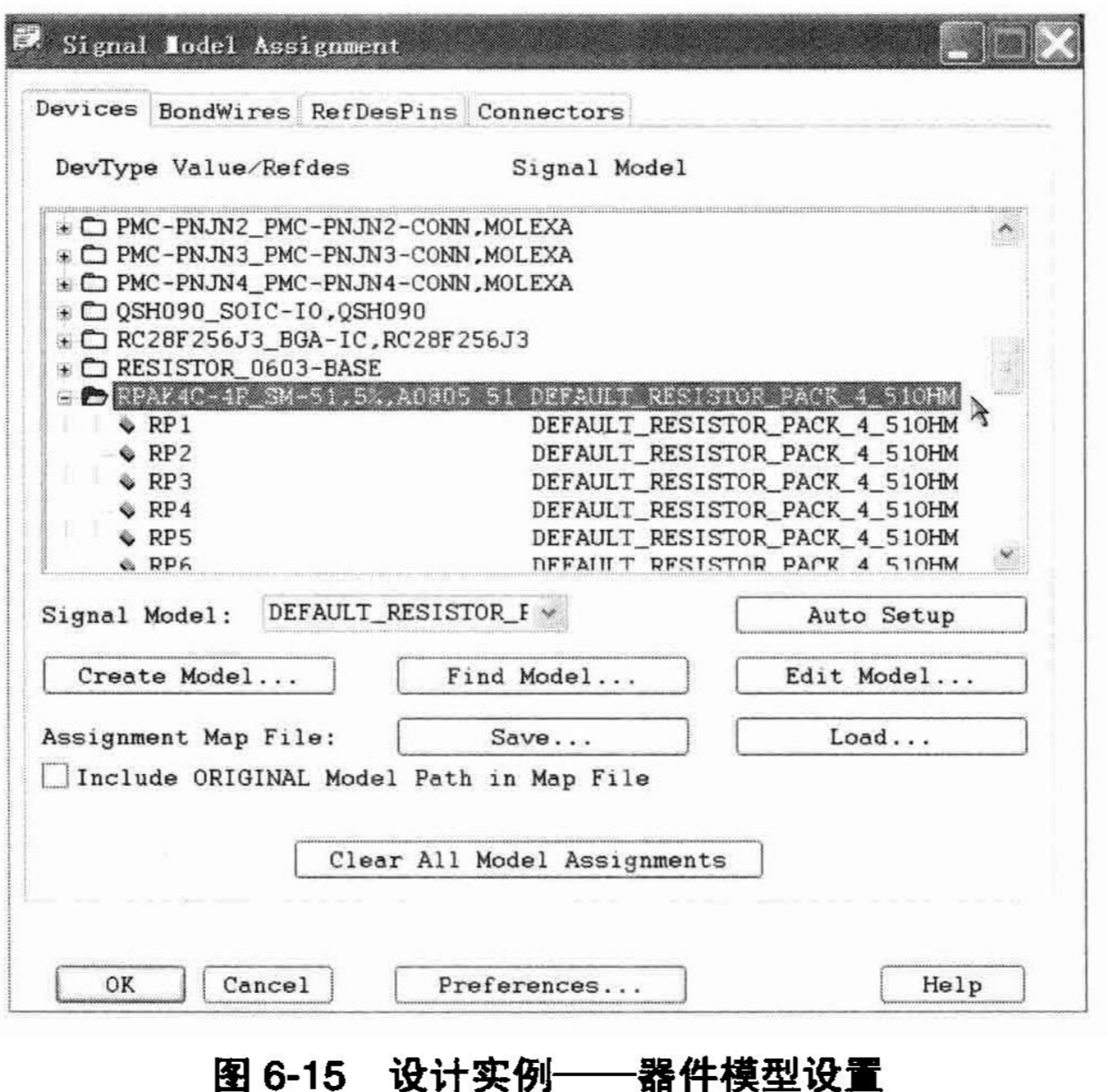

进入到模型设置界面 “Signal Model Assignment” 后,首先我们要做的是单击 “Auto Setup” 按钮,这一步是让系统对 RLC 等元件自动生成所需的模型。在执行完成之后,界面显示如图 6-15 所示。找到 “RPACK4C-AR_SM-S1” 这一行,展开显示后,我们可以看到,所有阻排器件都被赋予了一个 “DEFAULT RESISTOR PACK 4.510HM” 的模型。这个模型及其参数,就是系统根据器件的属性而自动生成并赋予的模型。

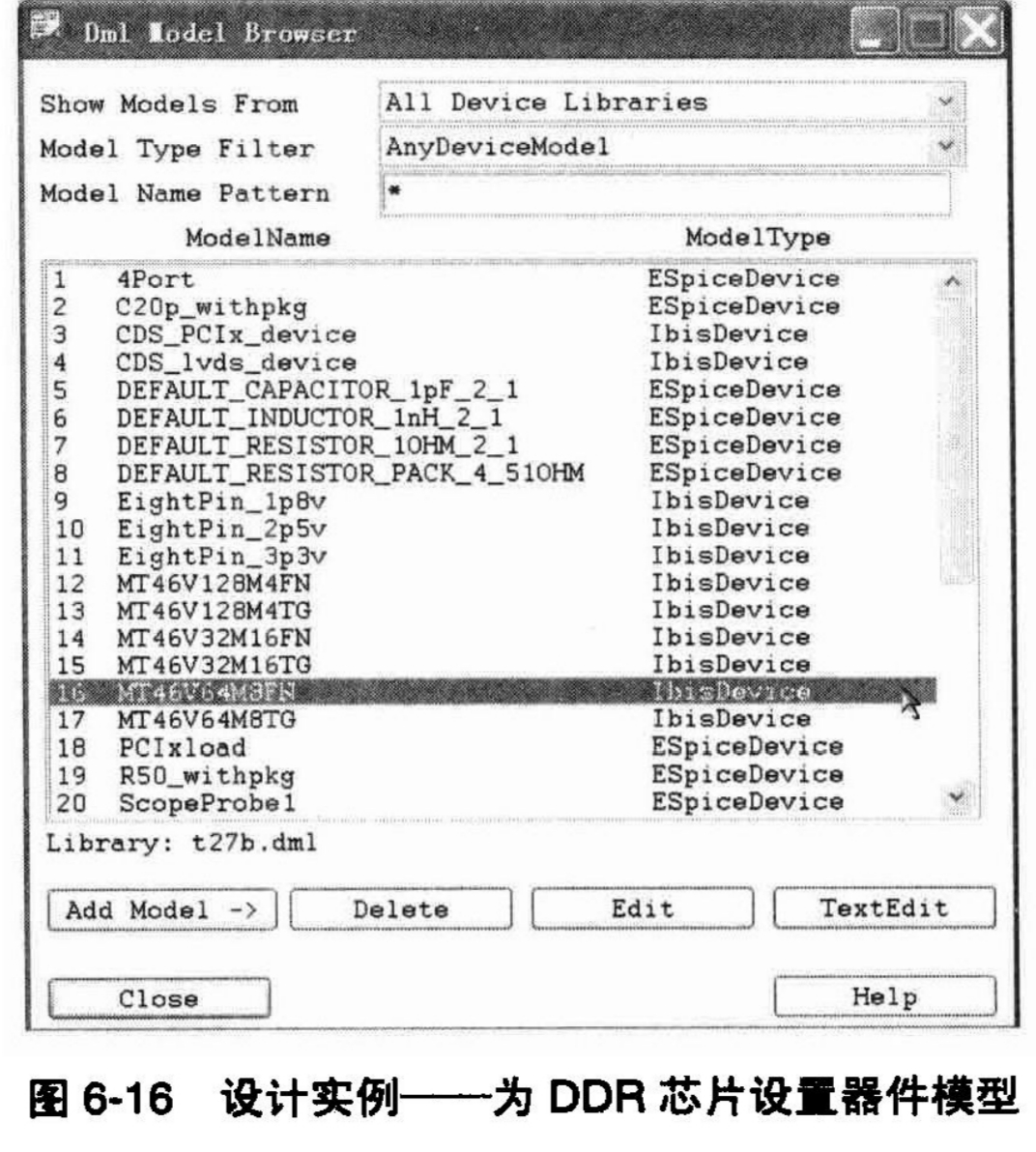

让系统自动生成器件模型后,我们注意到需要做仿真分析的 FPGA(标号为 U1)和 DDR 芯片(标号为 U5 到 U12)还没有被指定模型。这两个器件的模型需要我们手工指定。首先选中 DDR 芯片的器件类别 “MT46V64M8_BGA-MT46V64M8FN”,然后单击 “Find Model...” 按钮,在弹出的 “DML Model Browser” 界面中,找到 “MT46V64M8FN” 这个模型,选中它即可,如图 6-16 所示。

这样,所有 DDR 芯片都被赋予了 “MT46V64M8FN” 这个器件模型。

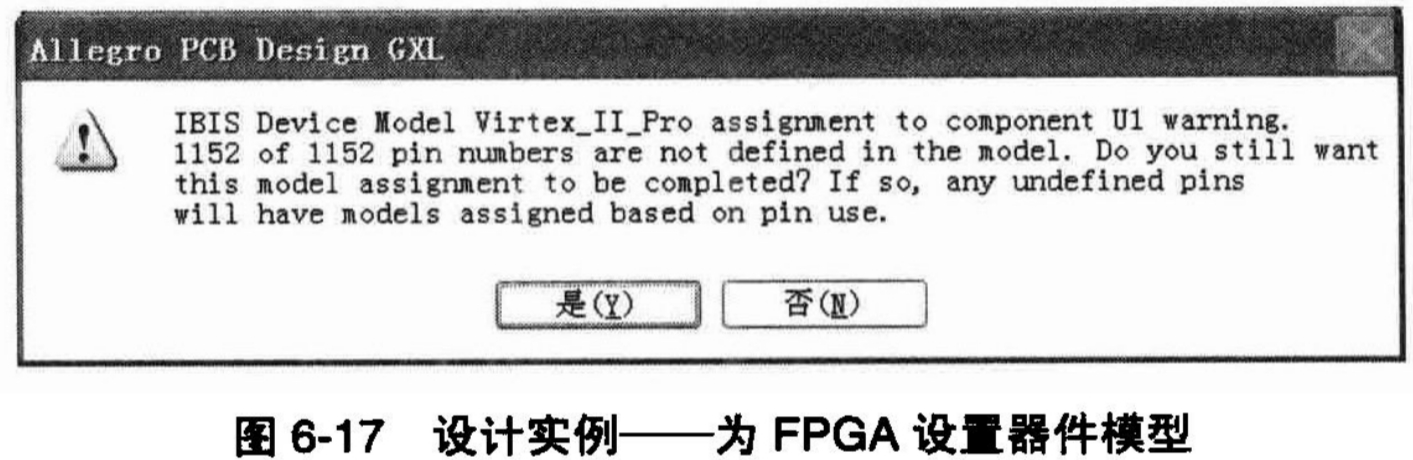

接下来,我们需要对 FPGA 器件,也就是 U1 指定器件模型。但是请读者考虑一下,我们确定要这样做么?让我们先来看看这样做会有什么结果。按照同样的步骤,我们对 U1 指定器件模型,当我们在上图 “DML Model Browser” 界面中对 U1 指定 “Virtex_II_Pro” 这个器件模型时,并没有得到预期结果,而是弹出了如图 6-17 所示的信息提示。

这个提示所描述的信息是,器件 U1 中的 1152 个管脚在模型中没有定义,是否继续执行指定模型的任务,如果继续执行,那么系统将按照管脚属性自动进行管脚的模型指定。在决定是否之前,我们要搞清楚为什么出现这个警告提示。我们知道,器件 U1 是一个 FPGA,它的管脚电气特性是由用户通过配置程序指定的,在配置程序生效之前,所有的管脚都是 “一样” 的,也即通用 I/O 管脚。那么在制作 FPGA 的 IBIS 文件的时候,是没有办法知道哪个管脚应该使用什么样的 I/O 逻辑的,所以在 FPGA 的 IBIS 文件中是没有管脚模型定义这一项的,而只有具体的 I/O 模型,至于系统中到底选用哪个 I/O 模型,是由用户来决定的。也就是说 FPGA 的 IBIS 文件中根本就不存在对器件中某一个具体管脚的描述(读者可以打开 DDR芯片的 IBIS 文件和 FPGA 的 IBIS 文件,将两个文件进行结构上的对比分析,不难发现其中的区别),也就没法从整体上对器件赋予一个模型,而只能针对某个管脚单独地指定模型。基于这个原因,我们在图 6-17 所示的对话框中单击 “否” 按钮,放弃对 U1 进行器件模型的指定。

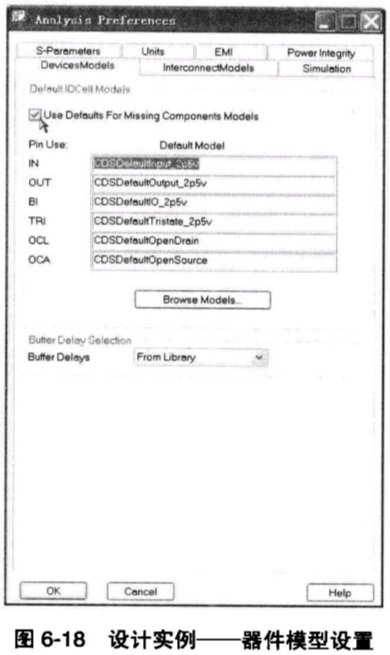

既然放弃了对 U1 进行器件模型的指定,那么接下来的问题,我们需要在仿真环境中使用 FPGA 的 I/O 模型时,该怎么办?答案是:先让系统对当前设计中所有没有被指定模型的 I/O 自动指定一个默认的 I/O 模型,这样就不会影响我们对信号线拓扑结构的抽取。在进入 SigXP 进行仿真分析时,按照具体的信号性能需求,再针对具体的器件管脚单独指定所需的 I/O 模型。所以,为了实现这个过程,我们需要检查一下,系统所指定的默认的 I/O 模型有哪些。

在信息提示界面中单击 “否” 按钮之后,我们回到图 6-15 所示的 “Signal Model Assignment” 界面,在这个界面的最下方,单击 “Preferences...” 按钮,打开如图 6-18 所示的界面。注意,在这个界面中,为了让系统对没有指定模型的器件指定默认的模型,必须选中 “Use Defaults For Missing Components Models” 复选框,这样当前设计中的所有器件管脚按照下面列举的 I/O 类型,进行默认模型设置。

需要提醒读者的是,对于这个界面中的其他参数,本书不一一做详细介绍,但是并不等于这些参数不重要,相反,对于这些在仿真中所需参数的设置和使用方法读者必须加以了解并且是彻底理解。本书中不做介绍的原因是因为这些参数对于一个 SI 工程师来讲,对参数的字面意义理解起来没有什么难度,不用在此赘述,但是对于这些参数如何影响仿真结果和产品的性能,读者必须要理解得非常透彻。在实际工作中,常常会发生由于参数设置不当,而对设计结果造成影响的例子。

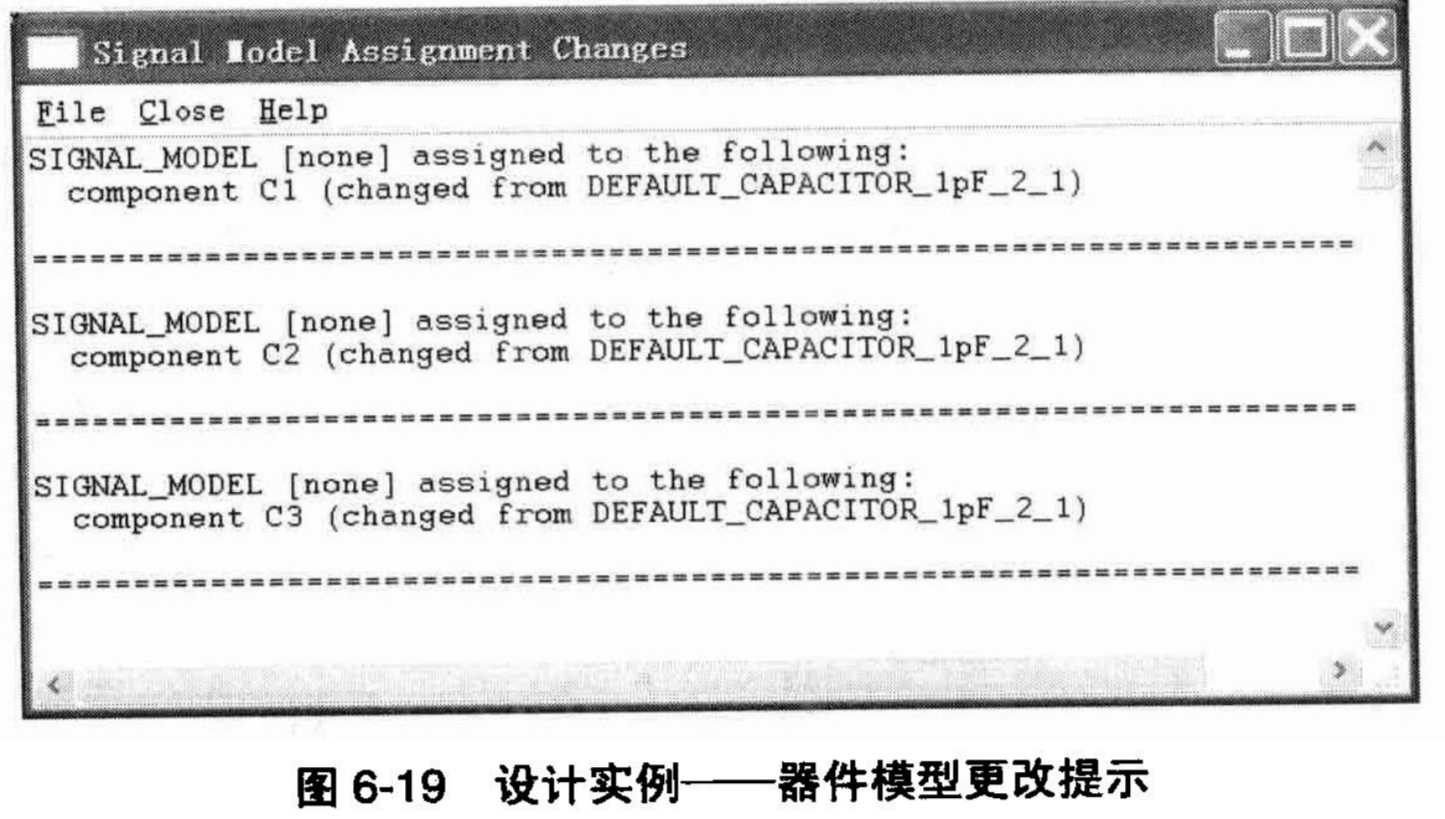

至此,我们已经完成了对所需器件的模型指定工作。单击 “Signal Model Assignment” 界面中的 “OK” 按钮,结束对模型的指定工作。这时,系统又会弹出一信息,如图 6-19 所示。通过阅读其中的内容,读者可以发现,这个信息提示我们哪些器件通过刚才的一些设置被赋予了新的模型。读者需要对这些信息进行检查,以确保下面的仿真工作中所需的器件及 I/O 模型被正确地指定了。

6.5 (预)布局

经过上面几步的工作,我们已经准备好了关键信号仿真分析的条件和参数设置。在目前这个状态下,已经可以开始对关键信号进行拓扑结构的抽取和仿真分析了。但是在这之前,作为一个完整的高速系统设计流程还有一个关键因素没有确定,那就是系统设计要求和预布局。

在上一章对高速系统设计流程的介绍中,我们已经讨论过这个问题。一个具体的 PCB 设计的布局要受很多方面因素的影响,这些预先确定的对布局或者系统性能的要求,在子系统的设计的约束中具有最高的优先级别,在不违反这些要求和约束的前提下,才能谈到对当前设计的实现和优化,如果违反了这些预先设定的要求,那么不论子系统做得多么精细和认真,对于整个项目来讲,都是没有意义的。例如,在我们的这个设计实例中,可以列举出如下的要求。

- 作为一个符合工业标准的板卡,其外型和尺寸都是有严格要求的,没有任何改变的余地;作为和主机系统进行连接的板卡,相关接口的接插件的物理位置也是事先定义的,如实例中右面的四个 VME-CPCI 接口;

作为通信子板,其外接光口的位置也是被限定的,如实例中最左面的四个光接口;

为了适应整个系统的操作和使用要求,按钮和指示灯的位置也是有要求的;

在和主机板互连时,还要考虑物理空间的限制,即在某个区域中对器件高度的要求。

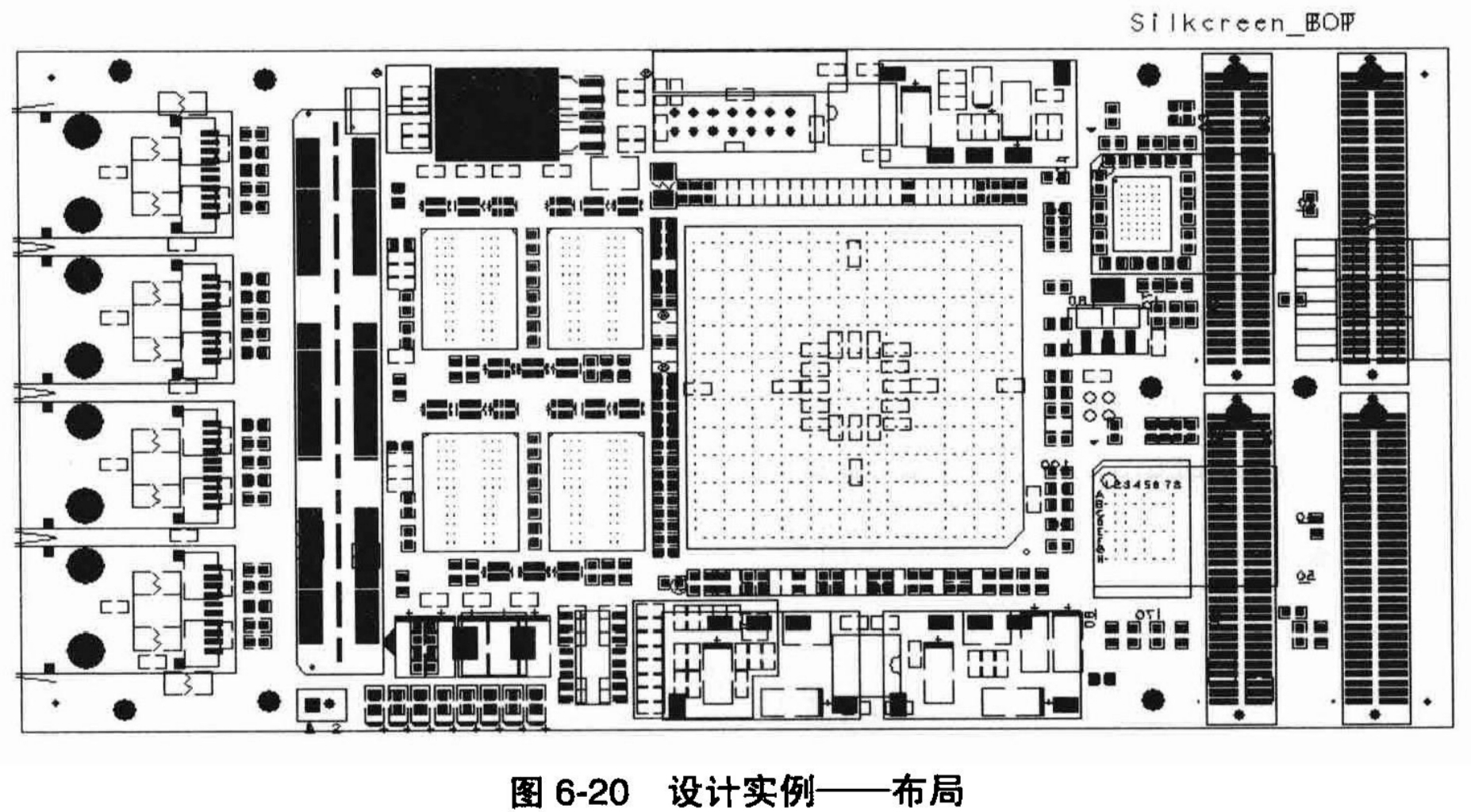

在满足这些预设要求的前提下,再通过对各类信号和互连关系进行合理的规划,我们所见到的设计实例,大致如图 6-20 所示的布局。