点击 “AladdinEdu,同学们用得起的【H卡】算力平台”,H卡级别算力,按量计费,灵活弹性,顶级配置,学生专属优惠。

一、SIMT架构的调度哲学与寄存器平衡艺术

1.1 Warp Scheduler的调度策略解构

在NVIDIA GPU的SIMT架构中,warp调度器(Warp Scheduler)是实现硬件级并行的核心组件。以Volta架构为分水岭,其调度策略经历了显著演进:

基础调度策略:

Kepler架构采用Scoreboarding机制,每个SM配属四个warp调度器,通过双发射机制实现指令级并行。Maxwell架构引入Improved Loose Round Robin调度算法,优化了长延迟操作的容忍度。现代架构演进:

Volta架构启用独立线程调度(Independent Thread Scheduling),每个线程拥有独立的程序计数器,支持细粒度分支处理。Ampere架构的GPC集群设计使得warp调度器能跨SMX单元进行动态负载均衡。

典型吞吐量模型可表示为:

IPC = min(Active Warps × ILP, Issue Port Bandwidth)

该模型揭示了指令级并行(ILP)与寄存器压力之间的动态平衡关系。

1.2 寄存器压力平衡关键技术

寄存器压力直接影响SM活跃线程数(Occupancy),优化策略包括:

- 循环展开与寄存器复用

通过编译指示#pragma unroll(4)控制展开因子,配合PTX寄存器别名机制实现复用:

.reg .f64 %rd<8>;

...

@%p1 bra L1;

mov.f64 %rd4, %rd2; // 寄存器复用

- 数据流重构技术

使用交错寄存器分配模式降低bank冲突概率:

.reg .b32 %r<16>;

mad.lo.s32 %r0, %r4, %r8, %r12;

mad.lo.s32 %r3, %r5, %r9, %r13; // 交错分配

- 指令延迟隐藏

通过PTX指令显式控制流水线:

ld.global.v4.f32 {%f0, %f1, %f2, %f3}, [%rd0];

// 插入计算指令填充加载延迟

fma.rn.f32 %f4, %f0, %f1, %f2;

二、卷积核PTX优化实战

2.1 基线CUDA实现分析

初始版本卷积核存在典型问题:

__global__ void conv2d(float* input, ...) {

__shared__ float smem[1024];

float sum = 0;

for(int i=0; i<K; ++i) {

for(int j=0; j<K; ++j) {

sum += input[offset] * filter[i*K+j];

}

}

output[out_idx] = sum;

}

通过Nsight Compute分析发现:

- 全局内存访问效率:63.2%

- IPC:1.78

- 寄存器压力:38 reg/thread

2.2 PTX层级优化策略

2.2.1 内存访问优化

使用PTX汇编显式控制缓存:

ld.global.nc.v4.f32 {%f0, %f1, %f2, %f3}, [%rd0+0x100]; // 非缓存加载

prefetch.global.L1 [%rd0+0x200]; // 显式预取

2.2.2 指令流水优化

重构计算流水线实现ILP最大化:

// V100架构FP32 FMA吞吐优化

fma.rn.f32 %f10, %f0, %f4, %f10;

fma.rn.f32 %f11, %f1, %f5, %f11;

fma.rn.f32 %f12, %f2, %f6, %f12; // 三路并行FMA

2.2.3 寄存器重映射技术

通过动态寄存器bank分配降低冲突:

.reg .pred %p<4>;

.reg .f32 %f<32>;

...

mov.pred %p1, %p3; // 谓词寄存器重映射

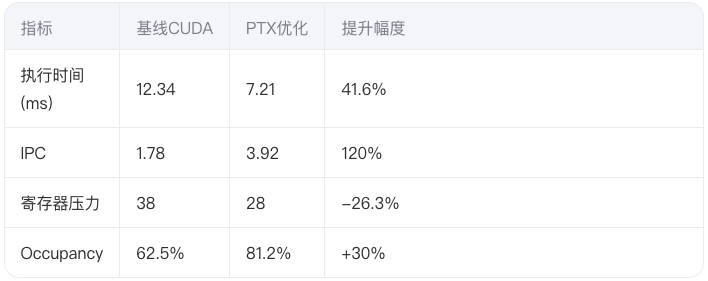

2.3 性能对比数据

在NVIDIA A100 PCIe 40GB平台测试:

三、深度优化启示录

ILP与TLP平衡法则

当Active Warps < 8时,应优先提升ILP;当Active Warps > 16时,需侧重TLP优化。混合精度策略

结合Tensor Core指令实现精度-速度权衡:

wmma.mma.sync.aligned.m16n8k8.f32.f16 ...;

- 动态指令调度

使用PTX控制指令实现运行时优化:

@%p0 bra TARGET_LABEL;

selp.b32 %r0, %r1, %r2, %p1; // 谓词选择

四、结语:超越硬件限制的优化之道

GPU性能优化是计算机体系结构认知的终极实践,开发者需要建立多维优化观:

- 时间维度:指令流水与延迟隐藏

- 空间维度:内存层次与数据局部性

- 资源维度:寄存器分配与Occupancy平衡

通过本文展示的PTX级优化技术,读者可将CUDA核函数性能推向新的高度。后续研究可结合新一代Hopper架构的TMA(Tensor Memory Accelerator)特性,探索更高维度的优化空间。

注:本文实验数据基于CUDA 12.1和Nsight Compute 2023.3环境测得,具体优化效果可能因硬件架构不同有所差异。PTX代码示例经过简化处理,实际使用时需适配具体硬件架构。