1:能不复位尽量不要复位,减少逻辑扇出数:比如打拍信号。

2:xilinx的FPGA推荐高复位,ATERAL的FPGA推荐低复位。

3:尽量使用异步复位:大多数厂商目标库内的触发器都只有异步复位端口,采用同步复位需消耗较多逻辑资源。

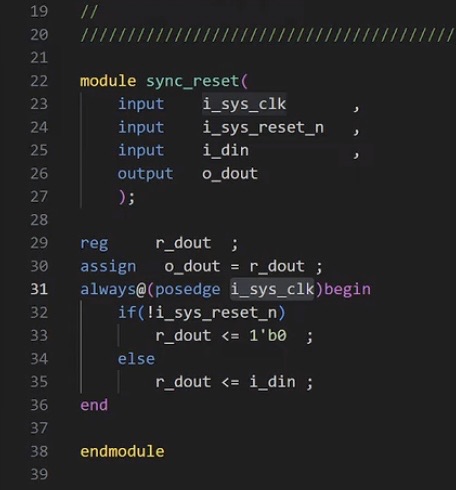

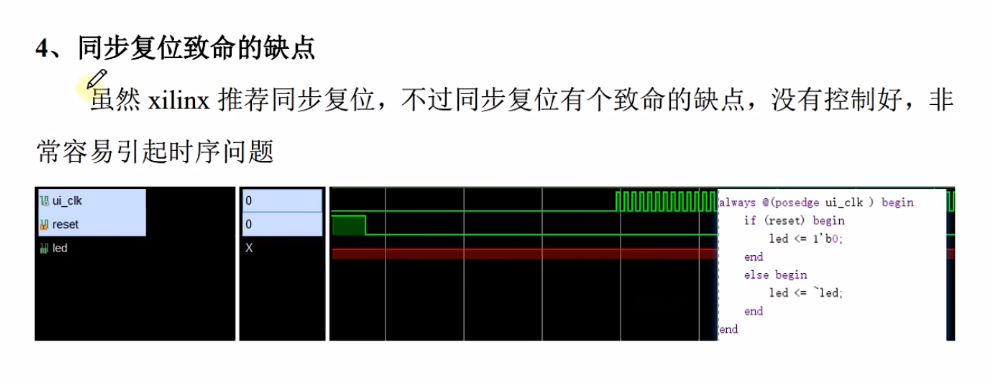

一:同步复位

1优点 :比较容易满足时序,都在时钟上升沿才触发。

2缺点:

2.1复位有延迟,有可能复位开始了由于要在时钟沿才有效所以并未及时响应。

2.2异步复位更加消耗逻辑资源。

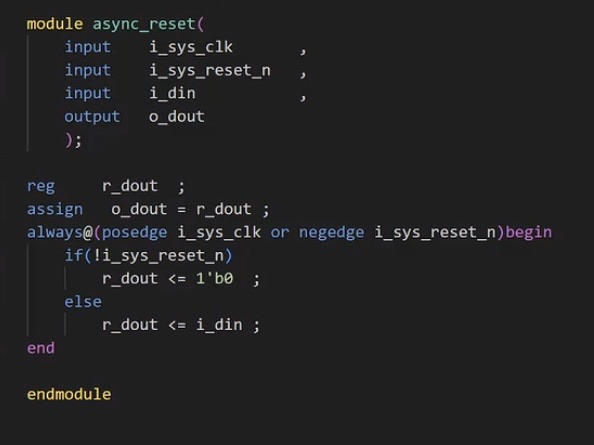

二异步复位:

1优点:复位响应及时,因为不需要在时钟沿才响应

2缺点:

2.1:因为是异步信号,容易导致亚稳态 。

2.2:复位信号只要有点干扰,就会导致复位响应。

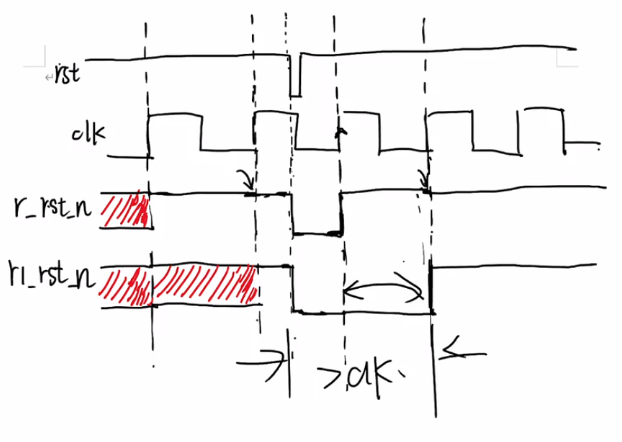

三:异步复位同步释放——推荐实战就用这个方式复位

module rst(

input sys_clk ,

input sys_rst_n ,

input data_in ,

output reg data_out

);

reg sys_rst_n_reg0;

reg sys_rst_n_reg1;

//对复位信号打两拍

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

sys_rst_n_reg0 <= 1'b0;

sys_rst_n_reg1 <= 1'b0;

end

else begin

sys_rst_n_reg0 <= sys_rst_n;

sys_rst_n_reg1 <= sys_rst_n_reg0;

end

end

//使用同步后的复位信号对数据进行复位

always @(posedge sys_clk or negedge sys_rst_n_reg1)begin

if(!sys_rst_n_reg1)

data_out <= 1'b0;

else

data_out <= data_in;

end

endmodule

优点:

只要异步复位信号出现一点毛刺复位都能使系统复位。有人会说这算啥优点和异步复位电路一样缺点太神经质了,万一人家根本不想复位呢。——

1.1系统不希望出现X态,异步复位电路由于未作同步释放,有可能出现一个及其窄的复位电平,导致有的慢时钟域处于未复位状态,有点快时钟域处于复位状态,有的临界时钟域刚好采集到沿上处于亚稳态(X)。而同步释放如图进行在本时钟域打拍延拓了复位周期,本时钟域都能采集到稳定复位信号。

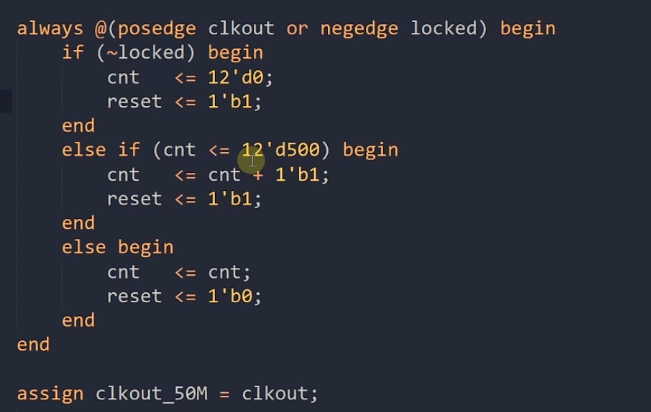

四:复位信号的来源——由于实际运用不太可能用按键复位,一般就用pll的locked信号

优点1:因为是Xilinx平台,所以产生的reset信号是高复位。

优点2:时钟lock后并未马上释放复位,而是等时钟完全稳定后在释放复位信号。

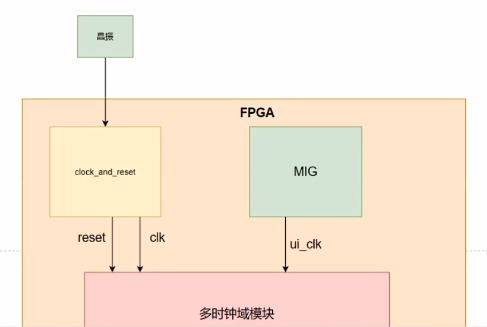

五案例:遇到mig的ui_clk,需要我们lock制造的异步复位信号,来复位整个系统。

此时我们就需要使用异步复位同步释放+加上一段时间的时钟稳定计数器操作即可。