一、STM32MP157AAA开发板套件介绍

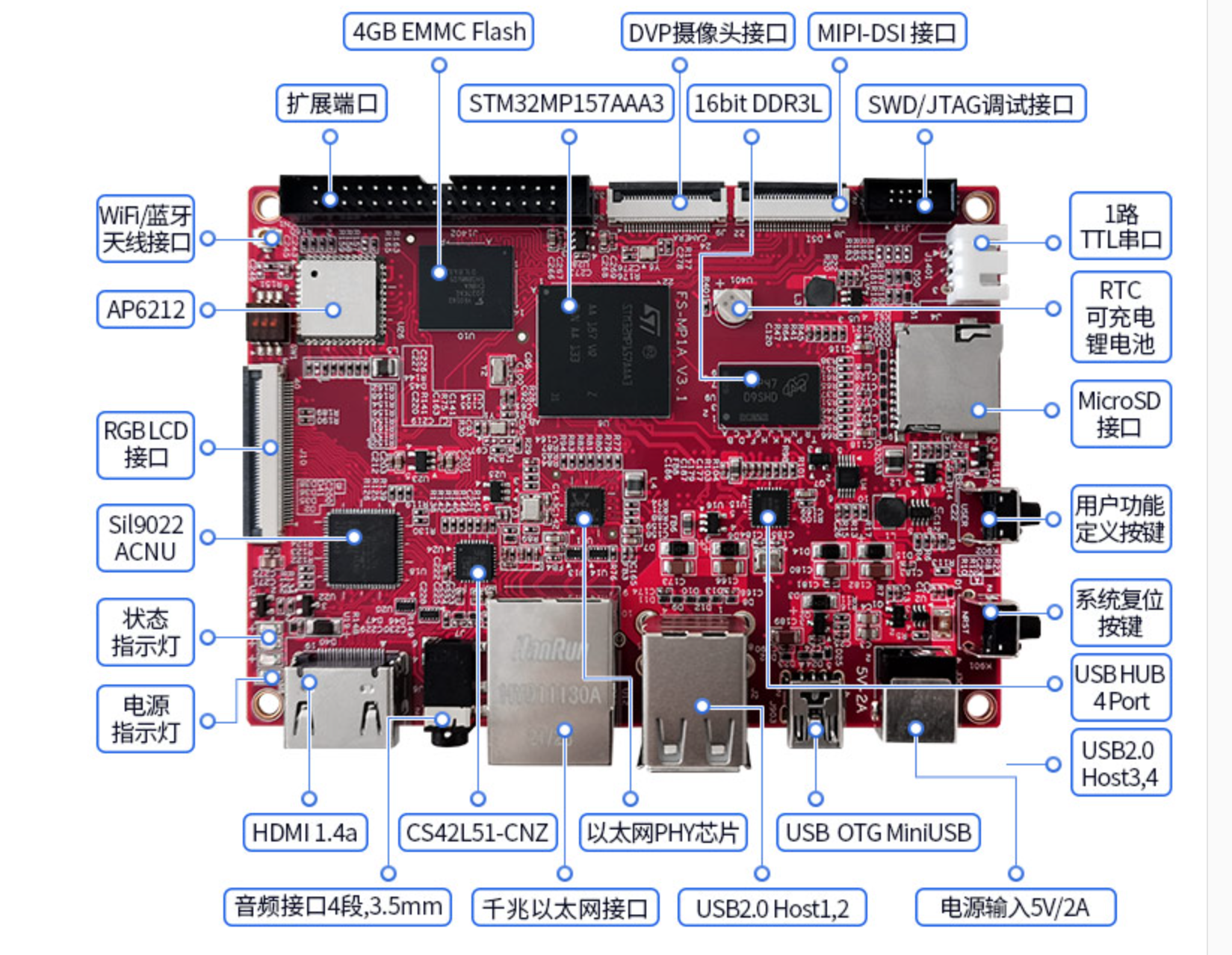

1.1 核心板 - 主板

如图所示:

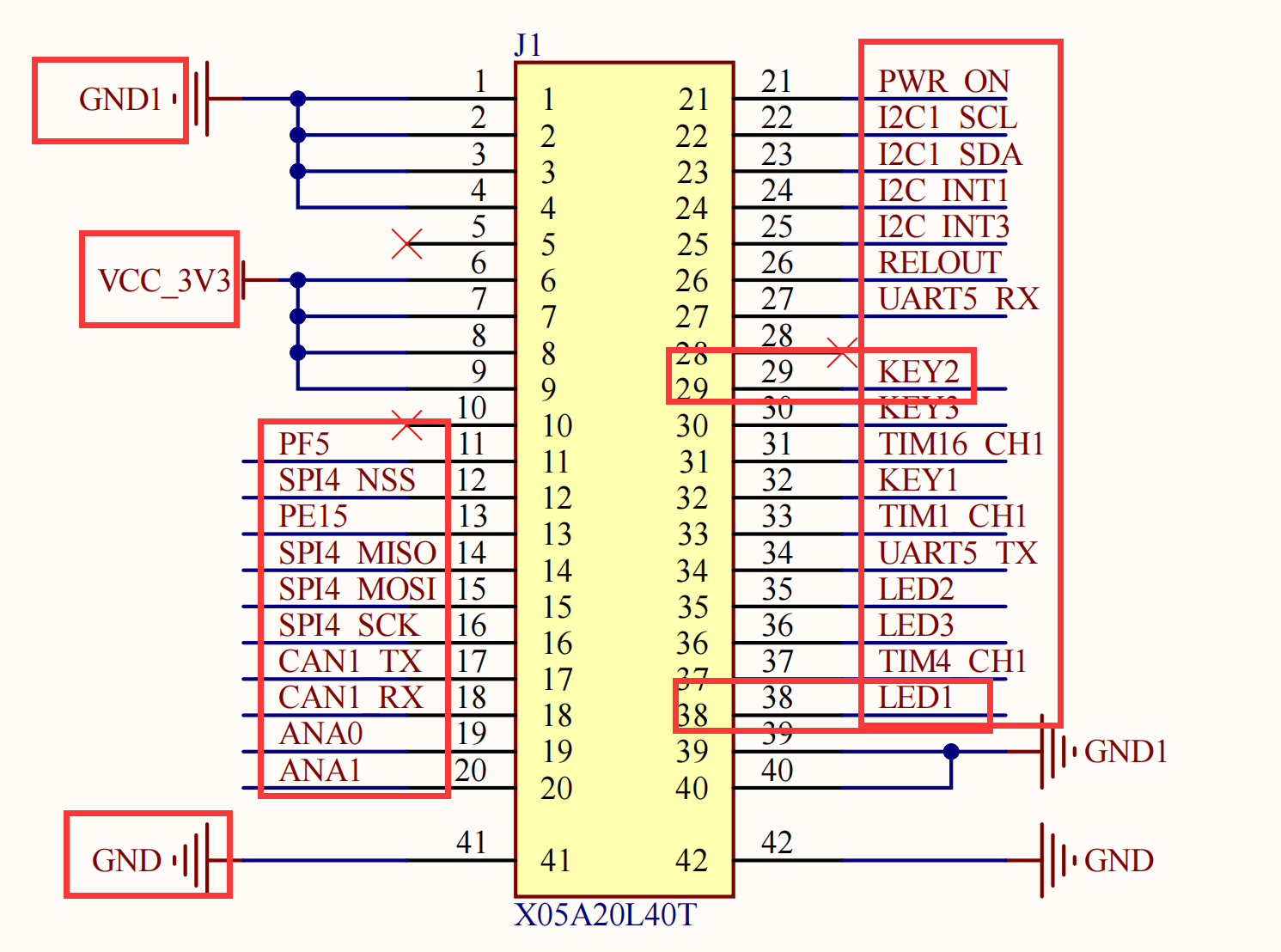

1.2 IO 拓展板

如图所示:

开发板名称(硬件平台):FS-MP1A

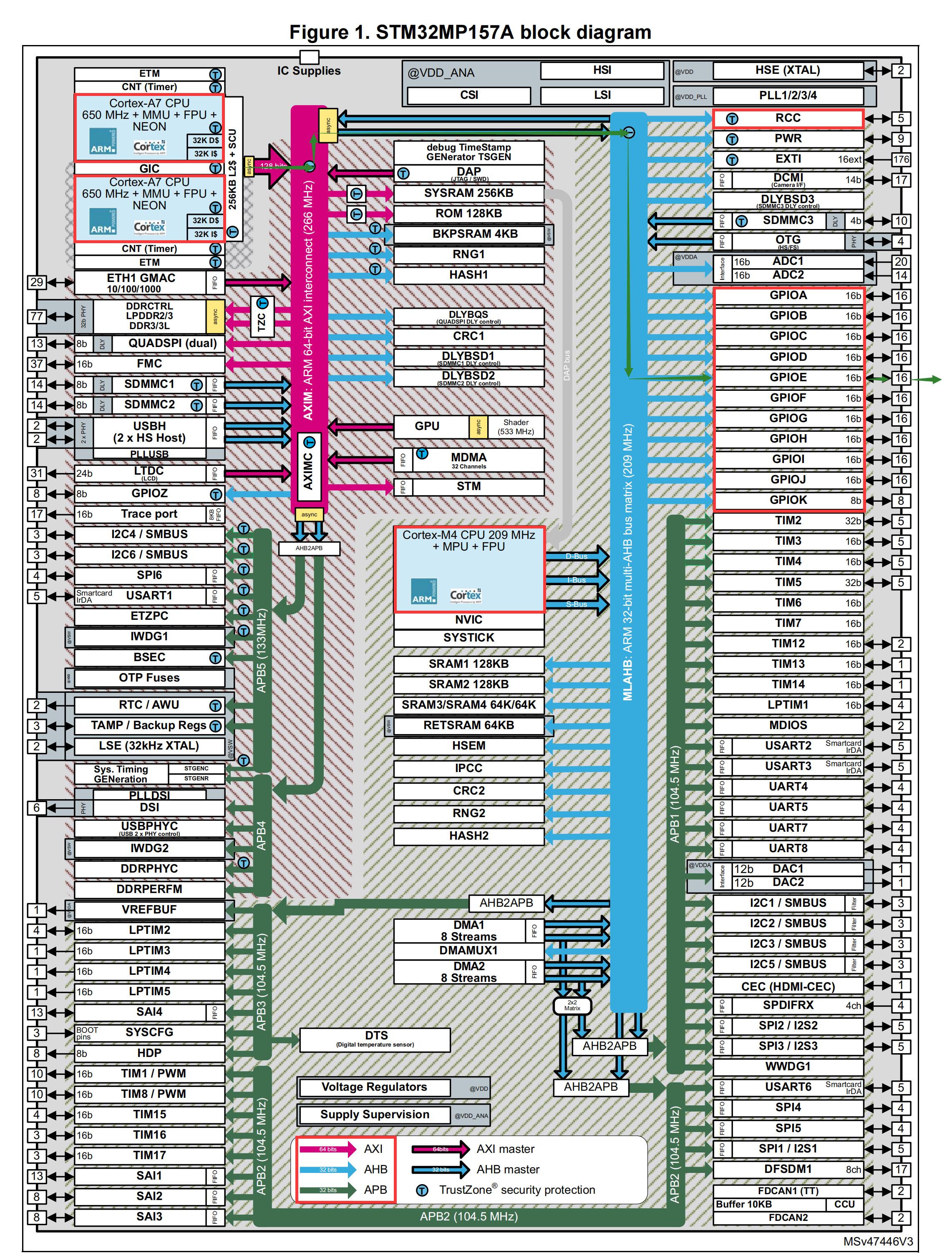

主控制器:STM32MP157AAA3 = Cortex-A7 * 2 + Cortex-M4 ------ 异构核

- 异构核:指在同一处理器(或芯片)内,集成了两种或多种架构、功能、性能不同的计算核心

CPU主频:Cortex-A7最高650MHz Cortex-M4最高209MHz

硬盘:eMMC(4G) TF卡(32G) DDR3:512MB

网卡:千兆网卡

屏幕:5寸、7寸、HDMI屏幕

摄像头:OV5640

二、硬件术语

2.1 原理图 / 电路图

原理图 / 电路图用于绘制并呈现各个电器元器件的硬件连接,是用于描述电子元器件连接关系、工作原理的核心技术图纸。

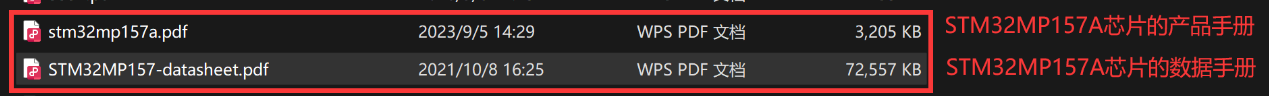

2.2 芯片手册

芯片手册中记录了当前芯片的内部结构并说明了当前芯片能够工作的流程

是官方、权威技术文档,核心作用是全面解析芯片的功能、性能、电气特性、使用规则及设计要求,是芯片选型、电路设计、编程开发和故障排查的 “说明书”。

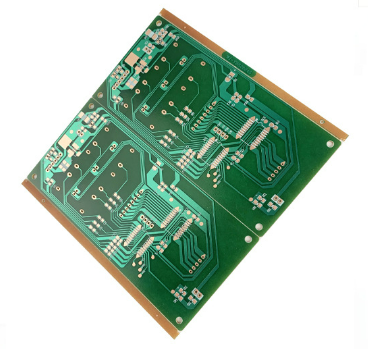

2.3 PCB 板

PCB板(Printed Circuit Board)中文名称为:印制电路板,用于集成各种硬件外设并综合连接。

它是电子设备中用于承载、固定电子元器件,并实现元器件之间电气连接的基础部件,广泛应用于手机、电脑、家电、汽车电子、工业控制设备等几乎所有电子类产品中。其核心作用是替代传统的手工焊接导线连接方式,大幅提高了电子设备的集成度、可靠性和生产效率。

2.3 丝印

丝印就是存在于 PCB 板上的白色字体,用于标志存在于 PCB 板上的各个电子元器件的唯一标识,每个电气元件的丝印都是唯一的。

电路图中的丝印是蓝色字体,与 PCB 板的白色字体是一致的。

常用电器元件丝印标识

电阻 R 电容 C 二极管 D 发光二极管 LD 三极管 Q 接插件 J 集成 IC 芯片 U

2.4 网络编号

在上面电路图中,红色字体就是网络编号,用于标志某个引脚或者某个引脚的功能

其在电路图中一般是两两对应的。

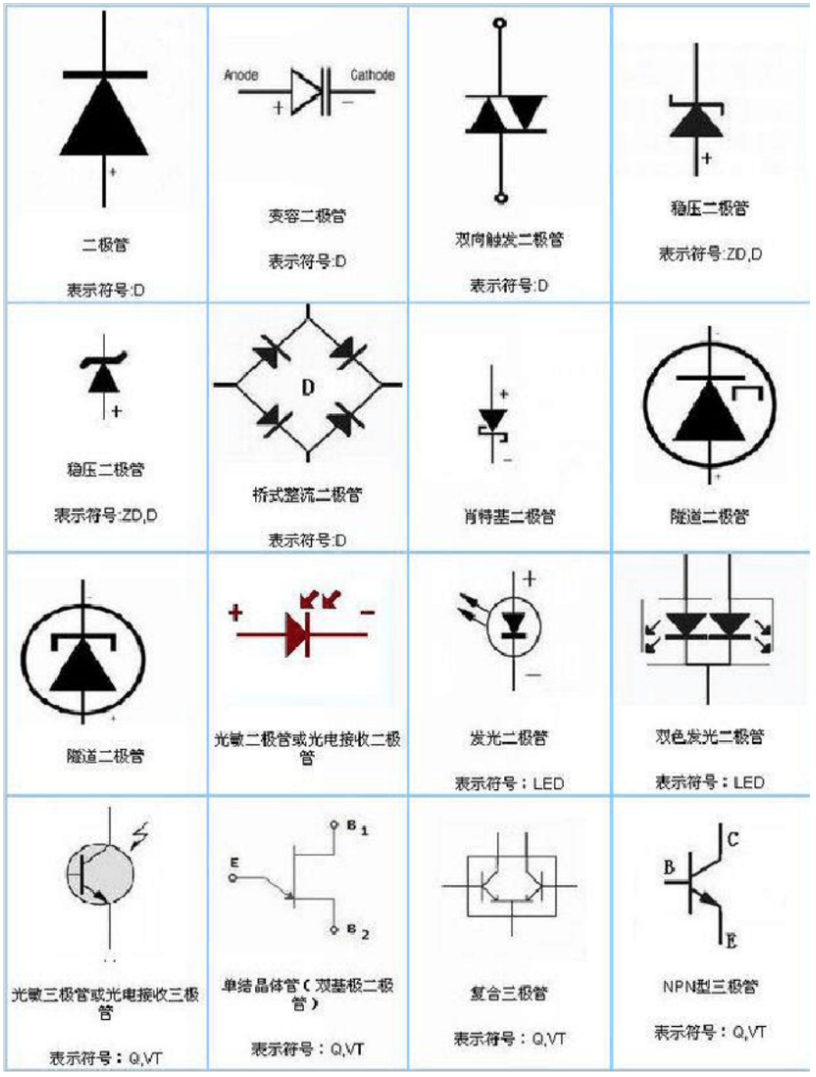

2.5 二极管

二极管特点:单向导电特性

二极管作用:保护电路,防止电流反方向击穿电路

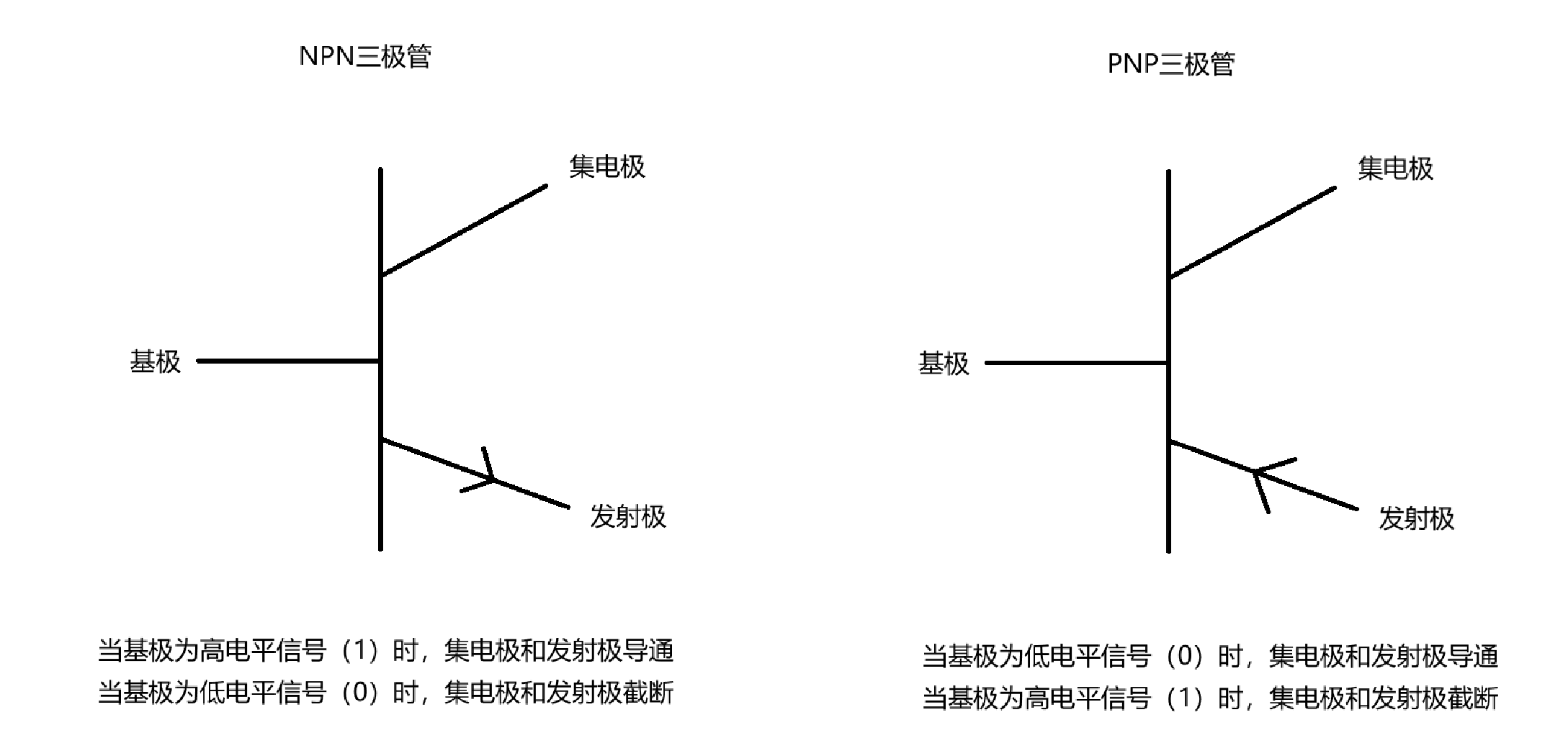

2.6 三极管

三极管:基极、集电极、发射极

三极管特性:放大特性(模拟电路)、开关特性(数字电路)

三极管分类:

- NPN 三极管

- NPN 三极管

模拟信号 ----> 连续变化的数值

数字信号 ----> 由0和1组成的电信号,0代表低电平信号,1代表高电平信号

当前FS-MP1A硬件平台是基于数字电路设计,也就是数据传输时,只能使用0和1组成的数字电信号进行数据传输。

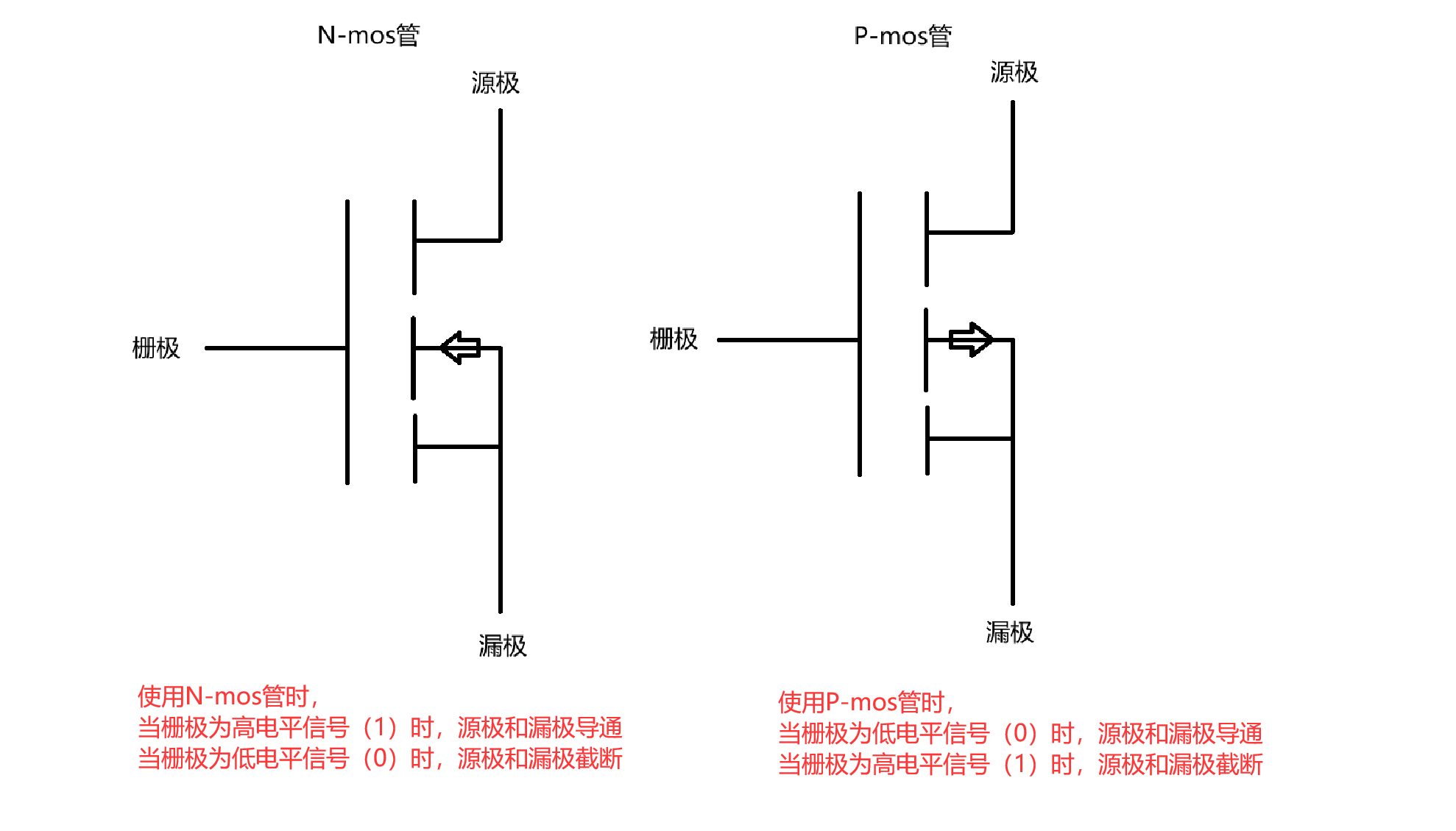

2.7 MOS 管

MOS 管的分类:

- N-MOS 管

- P-MOS 管

MOS 管的三极:

- 栅极、源极、漏极

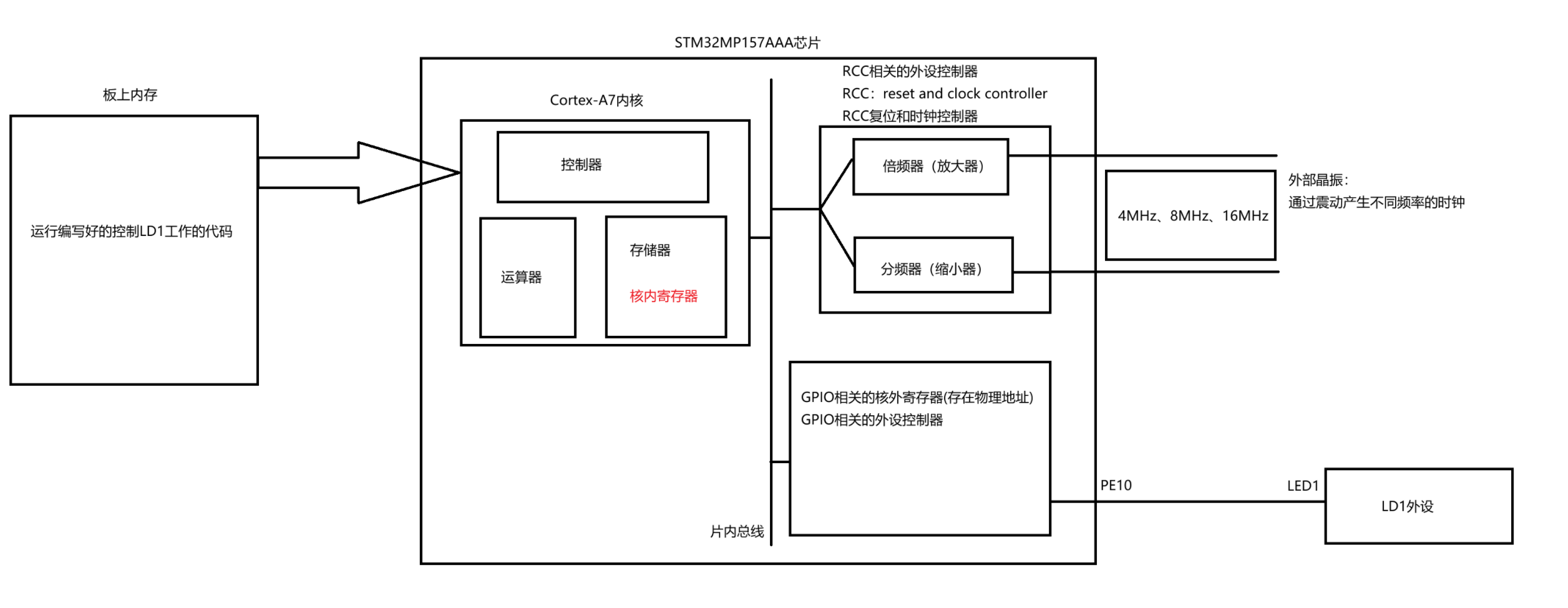

三、分析电路图

(1)主要做两件事

- 分析当前硬件的有效电路的导通和截断情况

- 找到控制当前外设的引脚

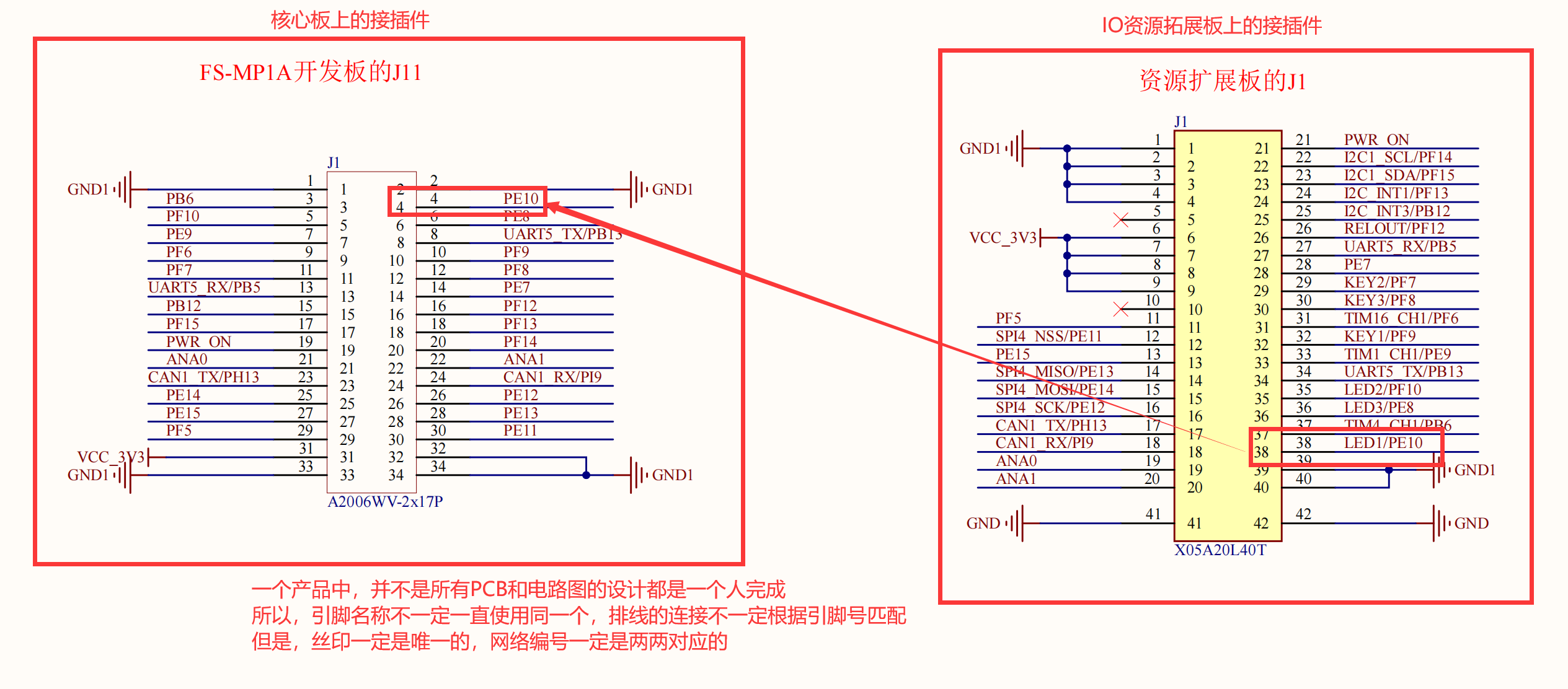

(2)查找外设引脚的步骤

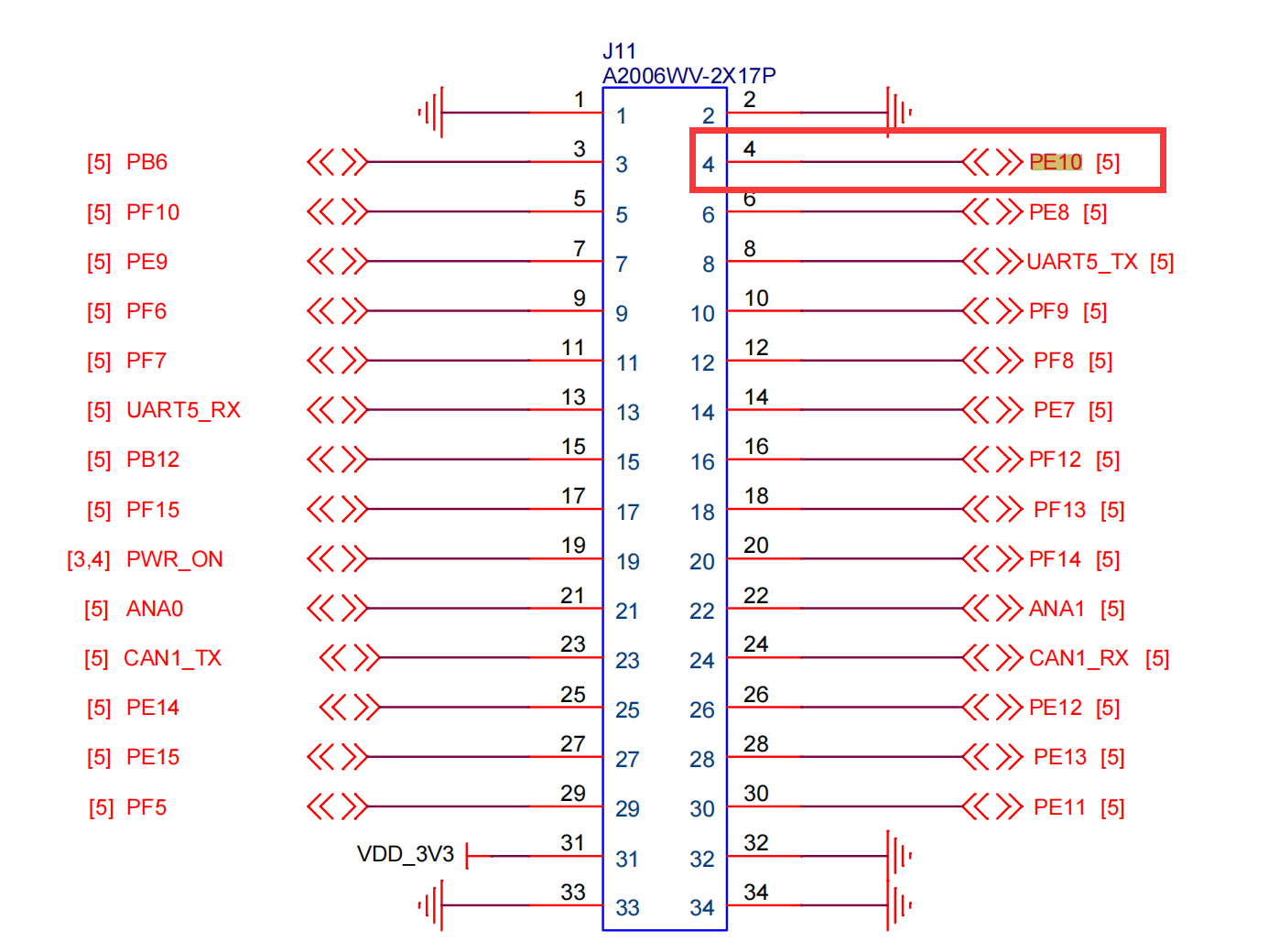

实际外设(IO拓展板) ---> 接插件(IO拓展板) ---> 排线 ---> 接插件(核心板)

---> 主控芯片(核心板)

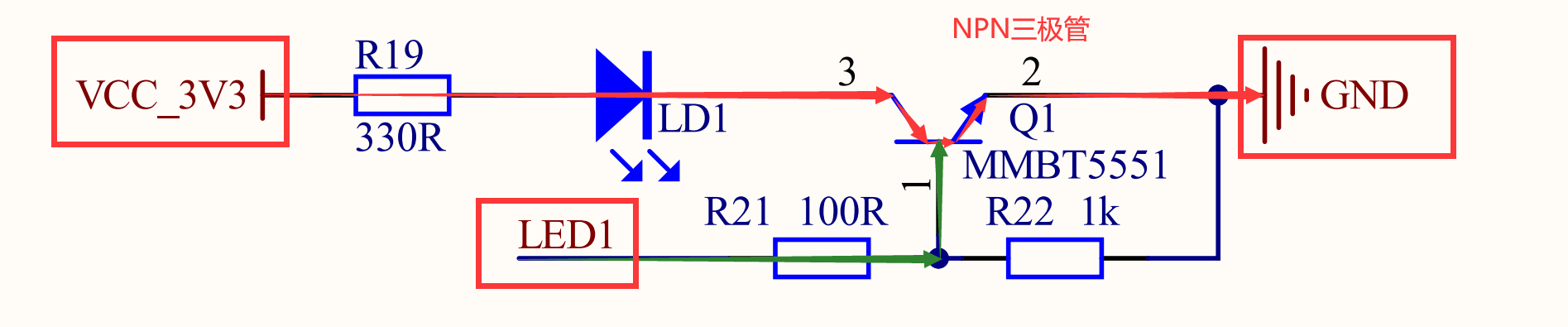

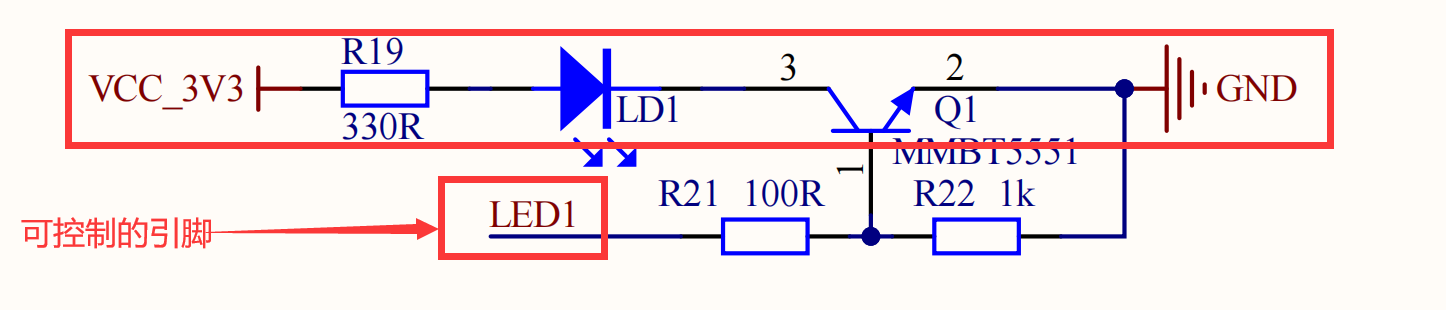

以查找LD1 ---- LED1引脚为例:

- 在PCB板上找到需要控制的实际外设的丝印:LD1

- 在IO资源拓展板原理图中找到LD1对应的电路,分析当前电路的导通/截断情况,得到人为可控制的引脚:LED1

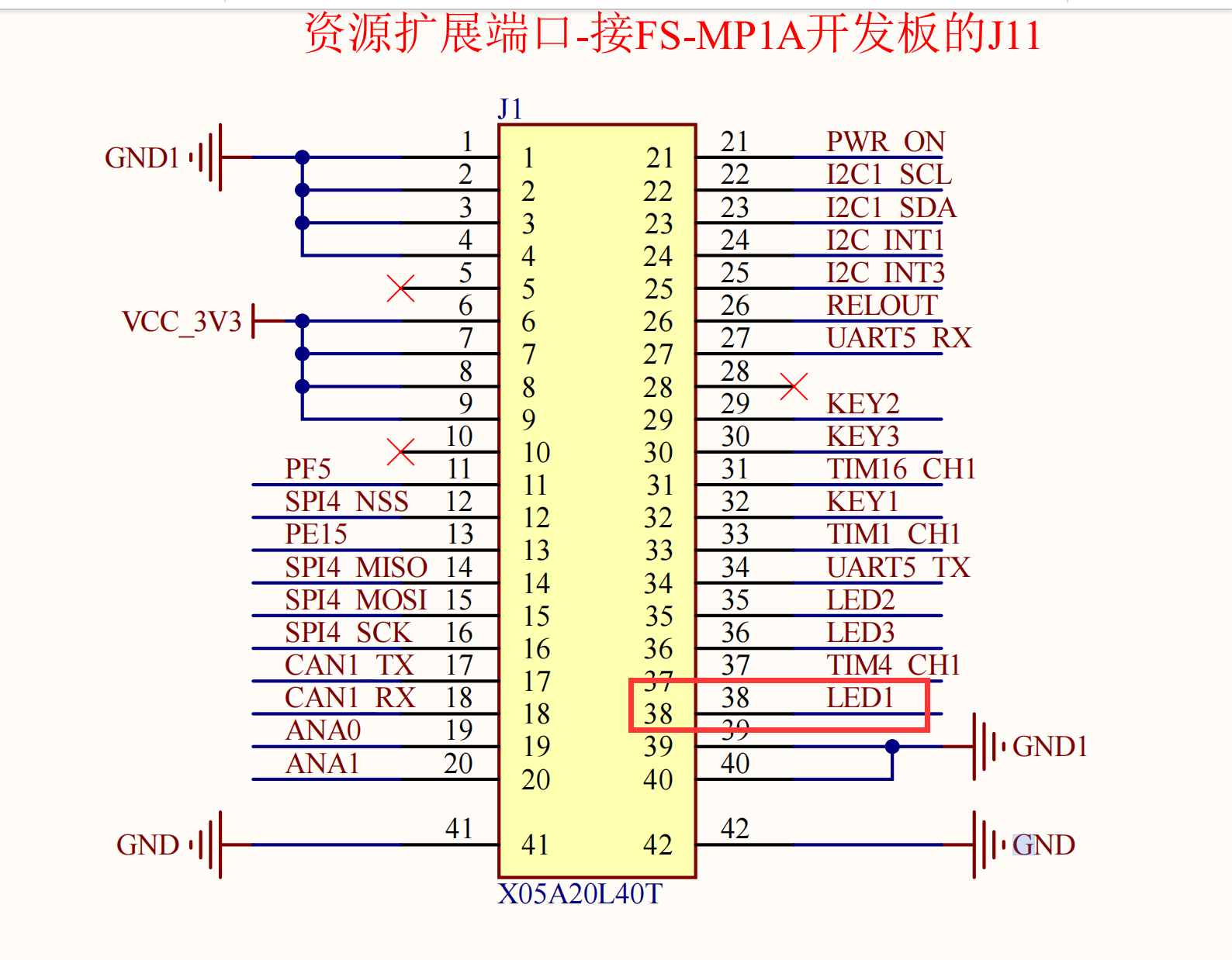

- 在IO资源拓展板原理图中的接插件上,寻找和LED1网络编号亮亮对应的引脚:接插件上的第38号引脚LED1

- 在接插件原理图中,找到拓展板接插件第38号引脚LED1/PE10,被连接到,核心板接插件上的第4号引脚PE10上

- 在核心板原理图中的第14页接插件上,可以找到:第4号引脚PE10

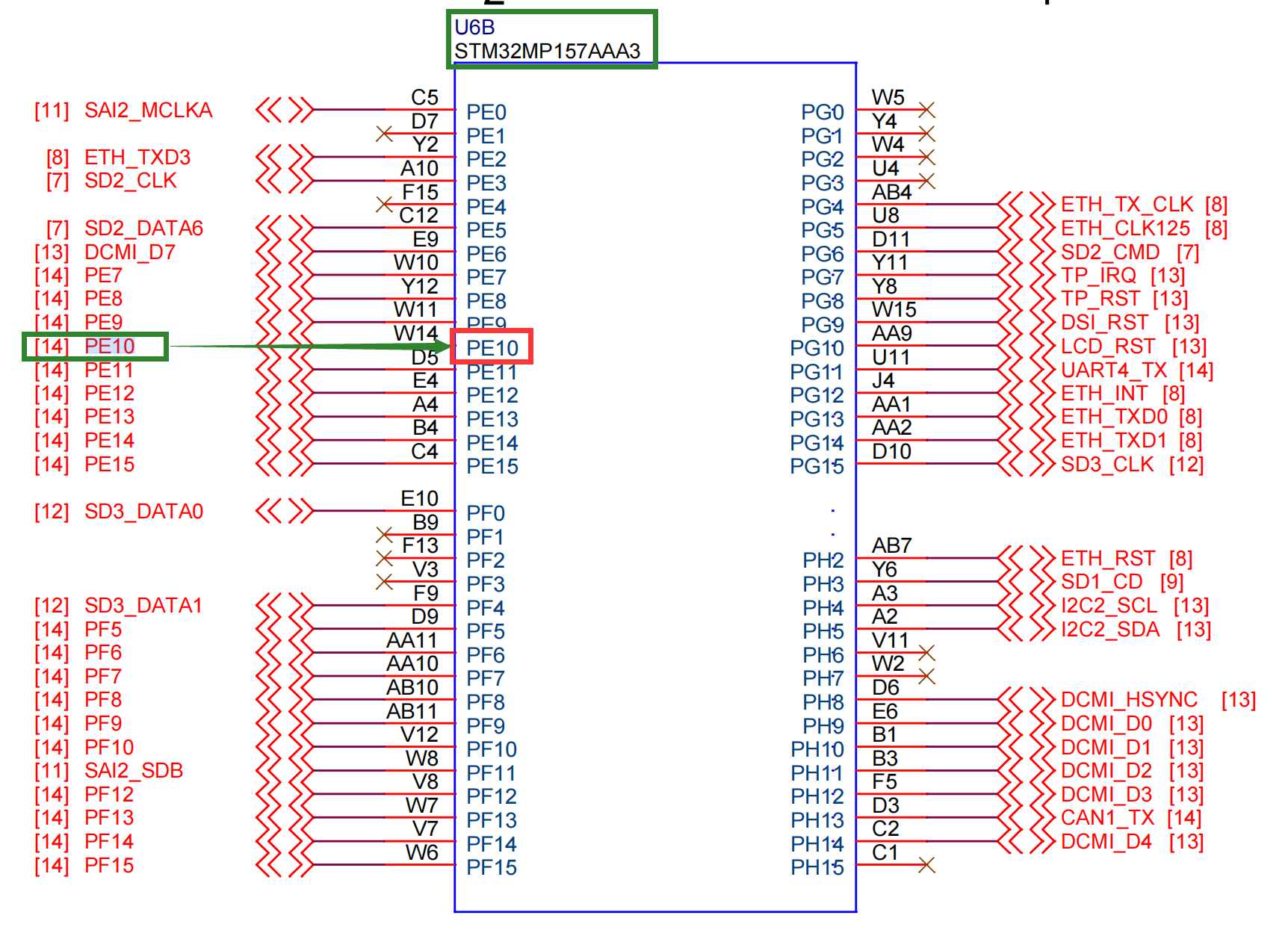

- 在核心板原理图中的第5页STM32MP157A主控芯片上,可以找到:PE10引脚

总结:PE10 ------> LED1 --------> 控制LD1的有效电路是否导通

(3)常用外设对应引脚关系

四、分析芯片手册

4.1 框图分析

4.2 STM32MP157A芯片内部图

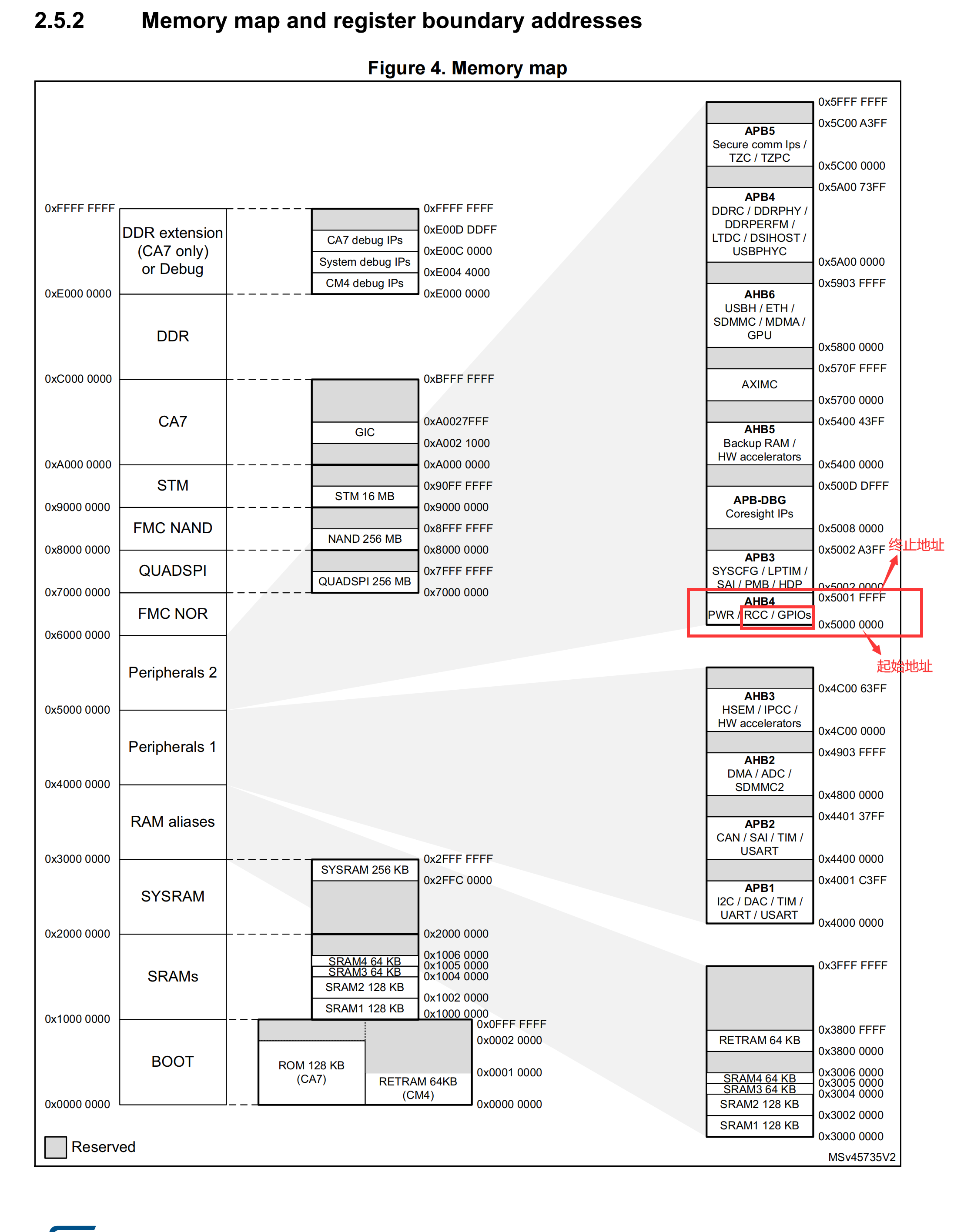

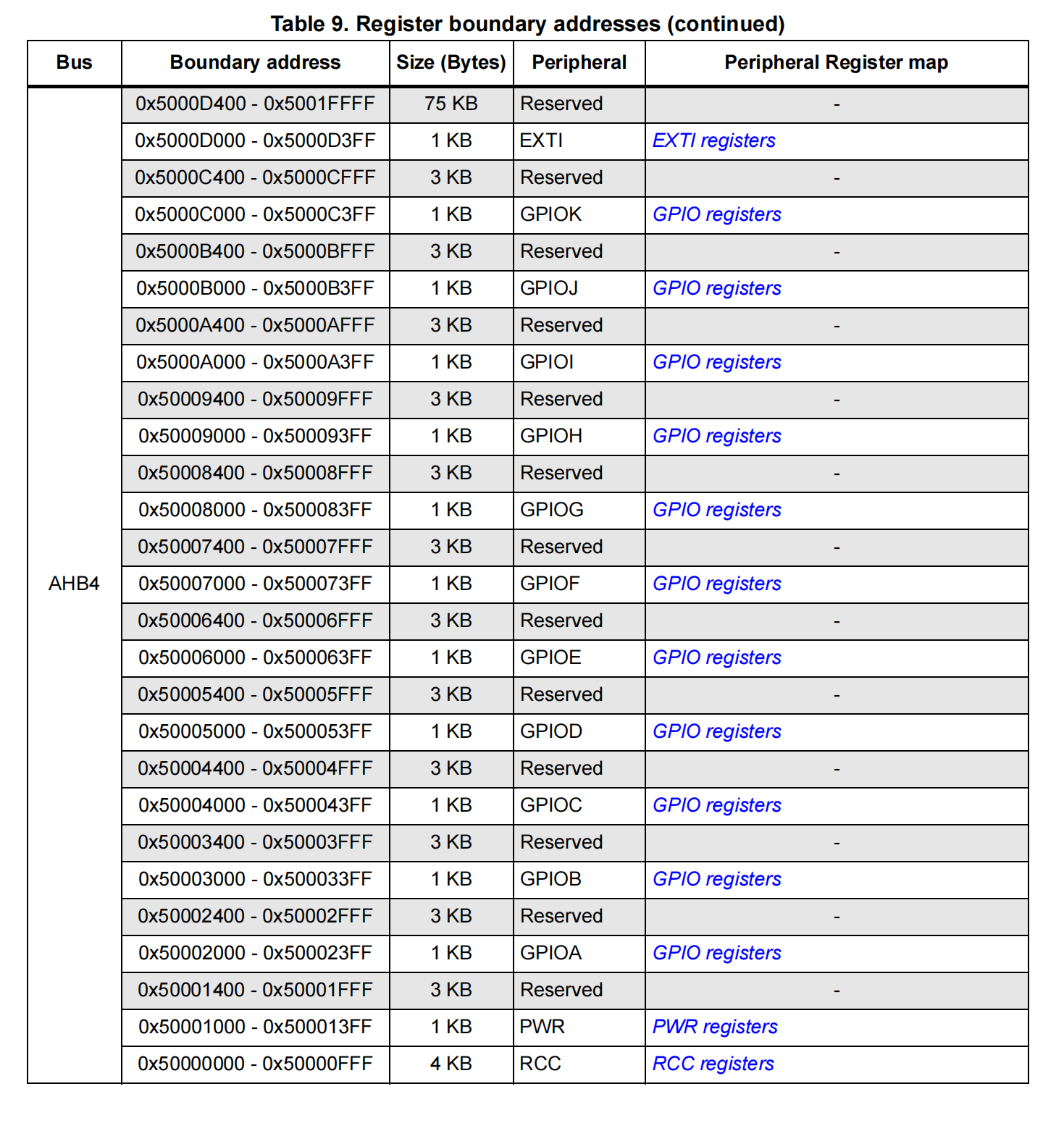

4.3 物理地址映射表

1)基本概念

物理地址映射表描述的是物理地址与硬件设备的对应关系。比如在基于 ARM 的微控制器中,会将不同的物理地址范围分配给不同的外设,像 GPIO 控制器、串口控制器、定时器等。物理地址映射表会明确指出哪个地址区间对应哪个外设,以便 CPU 通过访问特定物理地址来操作相应外设。

2)物理地址映射表

由上图可知:

- GPIOs 相关的外设控制器被连接在AHB4片内总线上

- RCC 相关的外设控制器也被连接在AHB4片内总线上

3)AHB4 总线(RCC 和 GPIOs )相关地址映射表

4.4 RCC 章节

1)RCC 概念

RCC ---- Reset and clock control ---- 复位和时钟控制器

RCC 用于时钟信号和复位信号的管理

作用:给外设控制器和内核提供时钟信号

2)查看 RCC 章节目的

★★★ 外设要工作,必须要先给它提供时钟信号 ★★★

通过 RCC 章节找到一个相关寄存器可以使能 GPIO 外设控制器,意思就是使用 RCC 中的一个寄存器使能 GPIO 外设控制器的时钟。

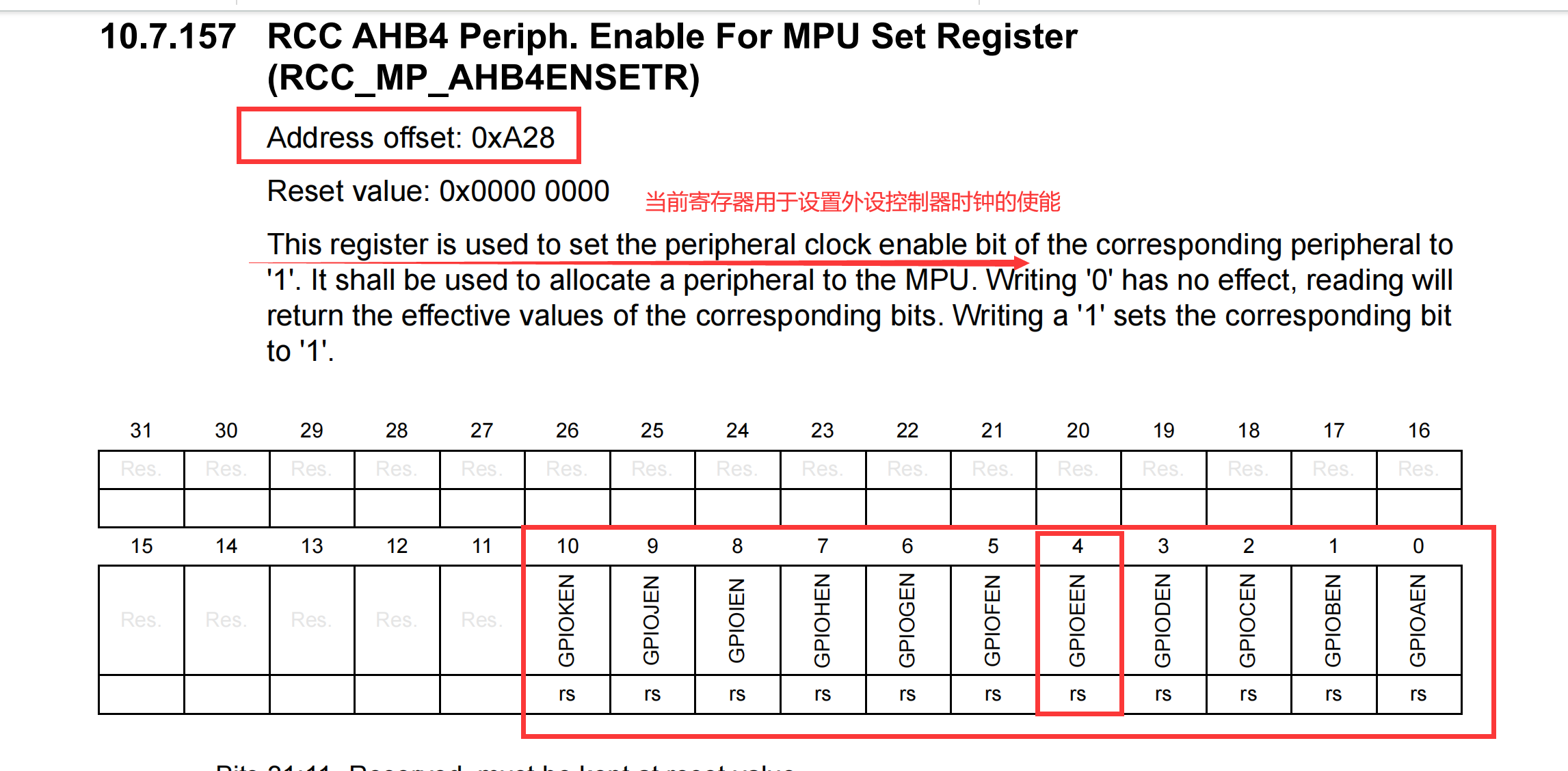

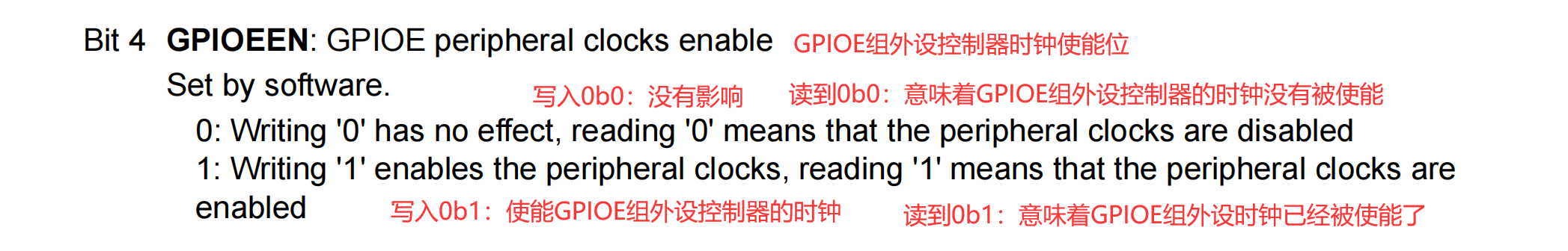

3)RCC_MP_AHB4ENSETR 寄存器

RCC AHB4 Periph. Enable For MPU Set Register

- 应用于使用 Cortex-A7 内核控制外设时

- 用于使能连接在 AHB4 这根片内总线上的外设控制器的时钟使能

4.5 GPIO 章节

1)GPIO 介绍

GPIO 是通用可编程的输入 / 输出端口,作用是输入 / 输出数字电信号

每个 GPIO 端口都有 4 个 32 位可编程的寄存器,2 个 32 位的数据寄存器,1 个 32 位的置位 / 复位寄存器

除此之外,每个 GPIO 端口还有 1 个 32 位的锁存寄存器,2 个 32 位的复用功能寄存器

GPIO 的主要特征:

- 输出状态(输出模式):推挽输出、开漏输出,是否外接上拉/下拉电阻

- 输出的数据可以来自输出数据寄存器或者芯片上的外设控制器

- 每个 GPIO 端口都有可选择的输入/输出速率

- 输入状态(输入模式):浮空输入模式、外接上拉、下拉电阻的输入模式、模拟输入模式

- 输入的数据会被存放到输入数据寄存器中或者芯片上的外设控制器中

GPIO 的八种工作模式

输入模式

- 浮空输入模式

- 外接上拉电阻的输入模式

- 外接下拉电阻的输入模式

- 模拟信号输入模式

输出模式

- 开漏输出模式

- 推挽输出模式

- 复用推挽输出模式

- 复用开漏输出模式

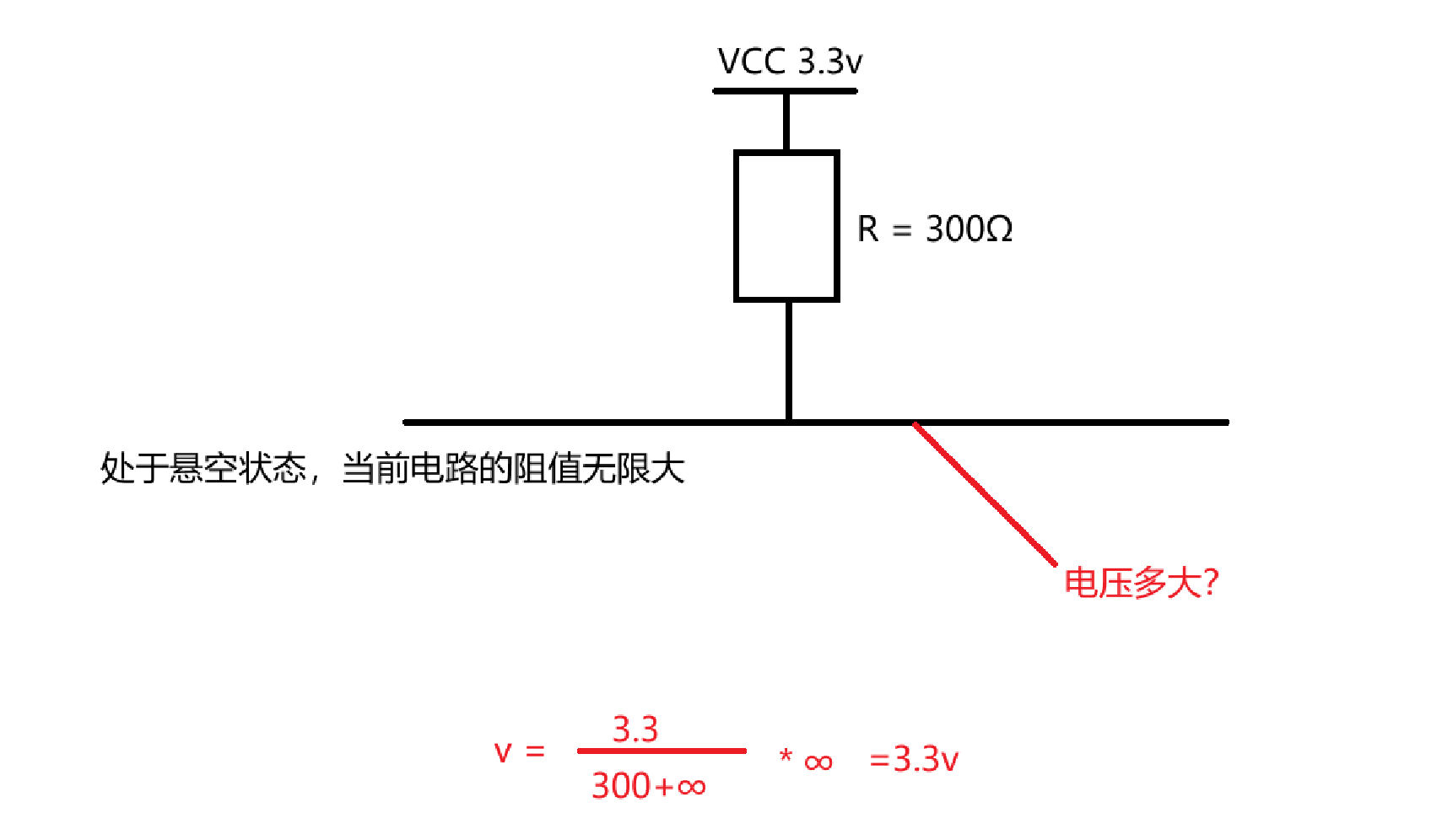

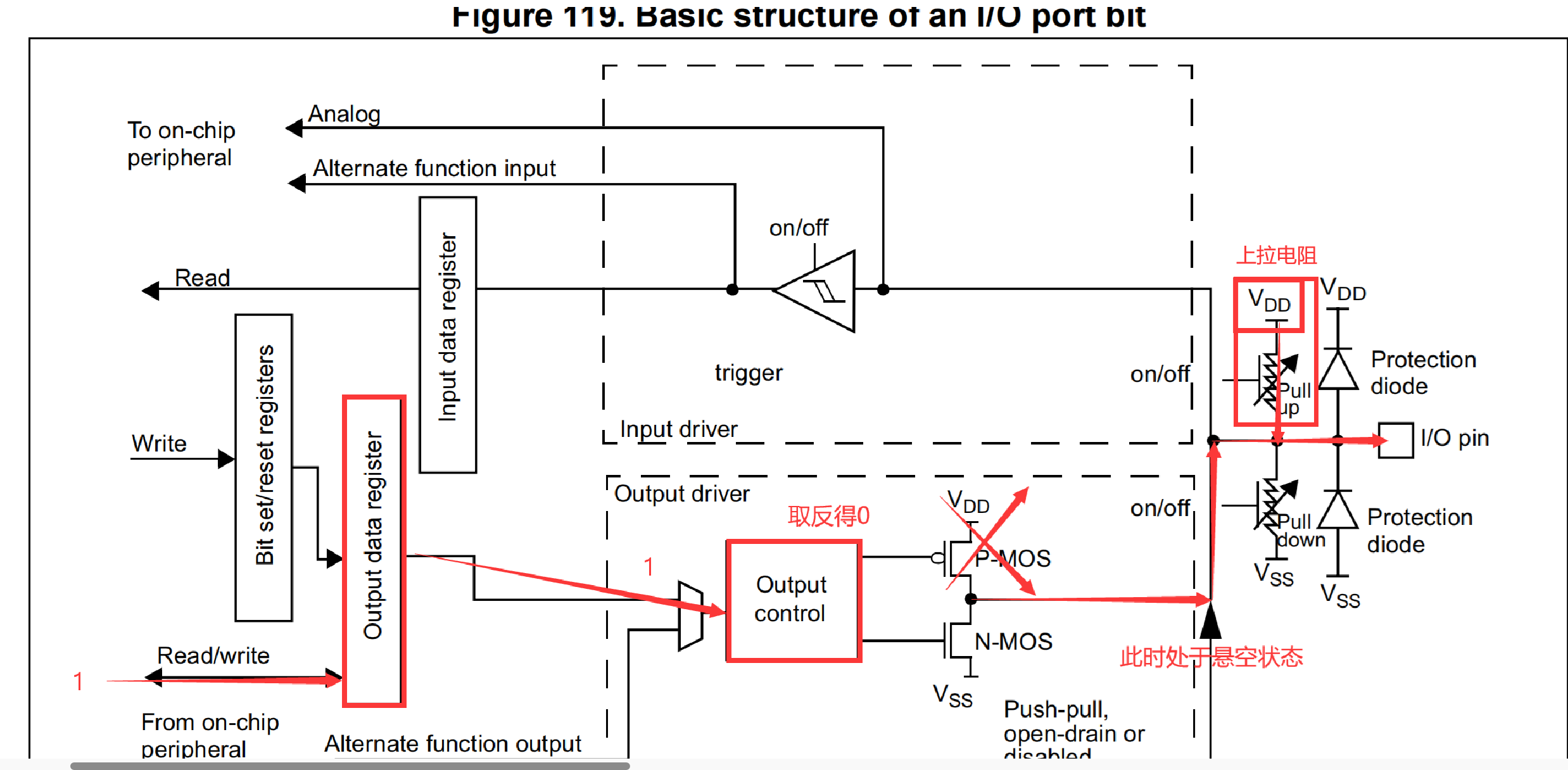

2)上拉电阻

电路的悬空状态(高阻态):当前电路的阻值无限大,并不清楚当前电路处于高电平状态还是低电平状态。

上拉电阻:一端连接到电源正极(如 VCC ),另一端连接到芯片的输入引脚或者输出引脚。

作用:悬空状态的电路,存在不清楚是高电平还是低电平状态的影响,当外接一个上拉电阻后,可以稳定当前电路处于高电平状态,用于保护电路。

接上拉电阻后引脚的电压:

3)下拉电阻

下拉电阻:一端连接到芯片引脚,另一端接地(GND)。

作用:当一个电路处于悬空状态时,外接一个下拉电阻,可以使当前电路处于稳定的低电平状态,用于保护电路。

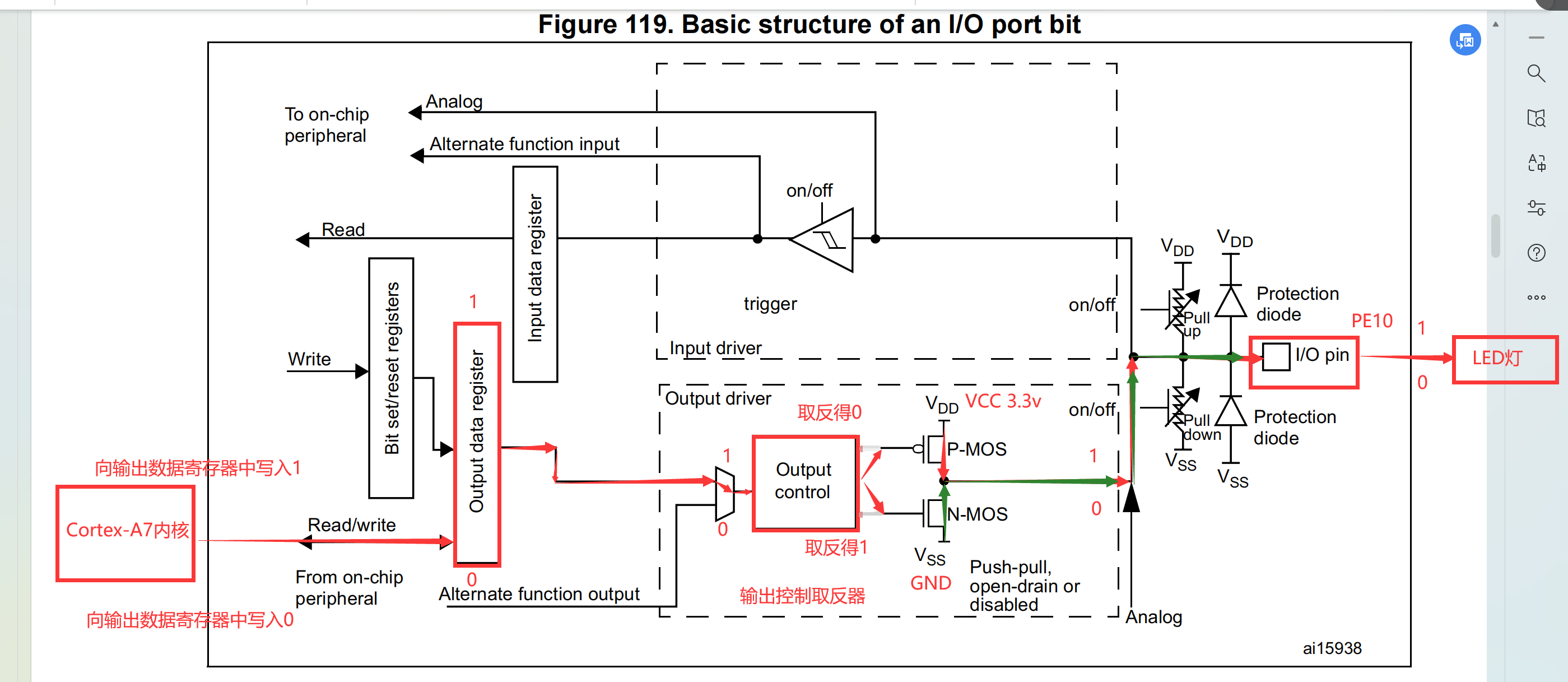

4)推挽输出

推挽输出时,GPIO外设控制器中的 N-MOS 管和 P-MOS 管都能正常工作,可以正常输出高电平信号/低电平信号

5)开漏输出

开漏输出时,GPIO 外设控制器中的 N-MOS 管正常工作,P-MOS 管不工作,只能输出低电平信号,无法输出高电平信号

问题:

使用开漏输出时,也想要输出高电平信号,需要怎么做(如何通过开漏输出输出高电平信号?)?

外接一个上拉电阻,让开漏输出也能输出高电平信号

开漏输出和推挽输出的区别?

- 电路结构:开漏输出仅含单类型晶体管(如 N 沟道 MOS 管 ),需外接上拉电阻;推挽输出由互补晶体管(如 NPN 和 PNP 型晶体管)构成。

- 电平输出:开漏输出不能直接输出高电平,靠上拉电阻拉高;推挽输出能直接输出高、低电平。

- 驱动能力:推挽输出驱动能力强,能快速驱动负载;开漏输出驱动能力弱,需依上拉电阻调整。

- 功能特性:开漏输出可实现电平转换,具备线与功能;推挽输出不便电平转换,无线与功能。

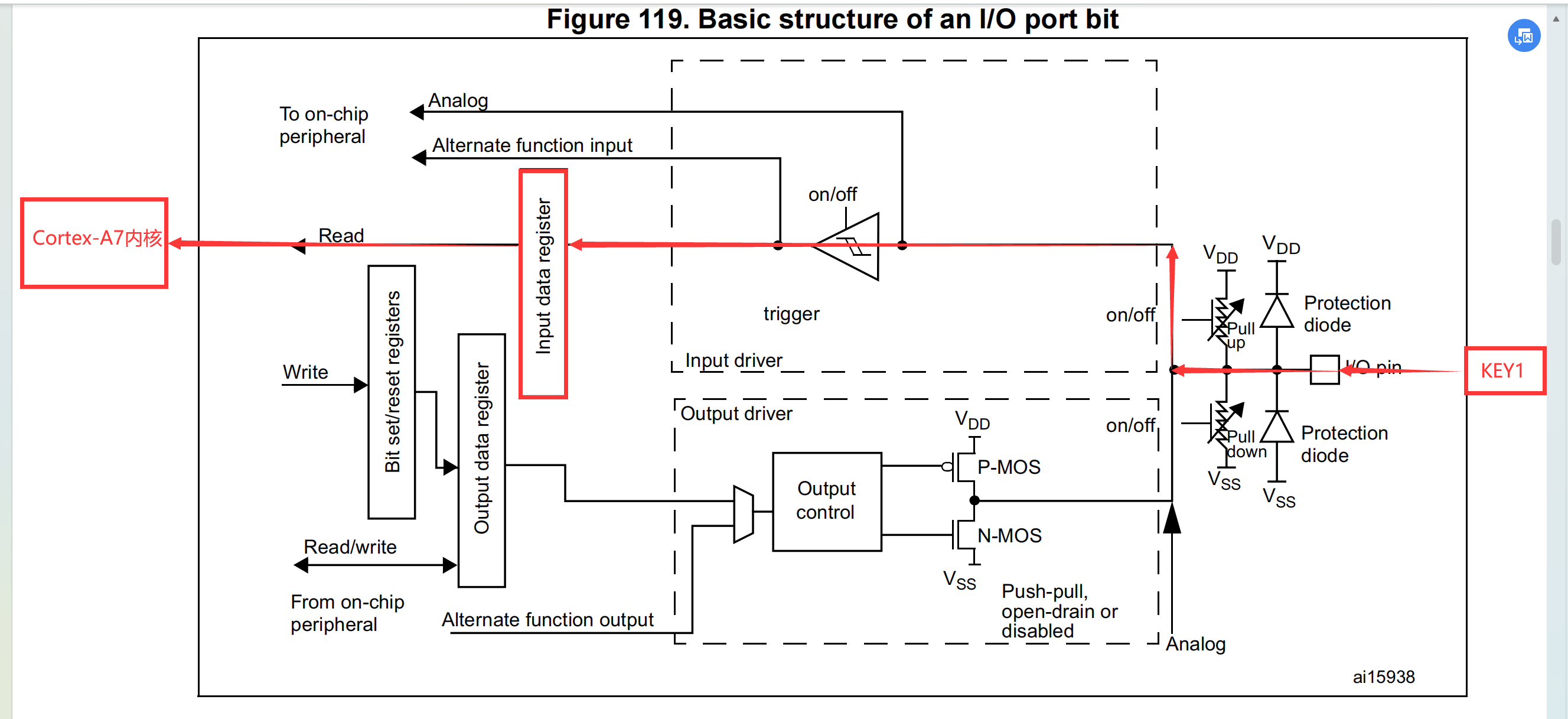

6)GPIO 内部框图分析

输出走线

输入走线

7)功能分析

GPIO 端口控制寄存器

每个 GPIO 端口都有 4 个地址映射控制寄存器用于配置 16 个 GPIO 引脚

以 PE10 为例:

P:pin

E:属于 GPIOE 端口(GPIOE 组)

10: 属于 GPIOE 下的第 10 号引脚

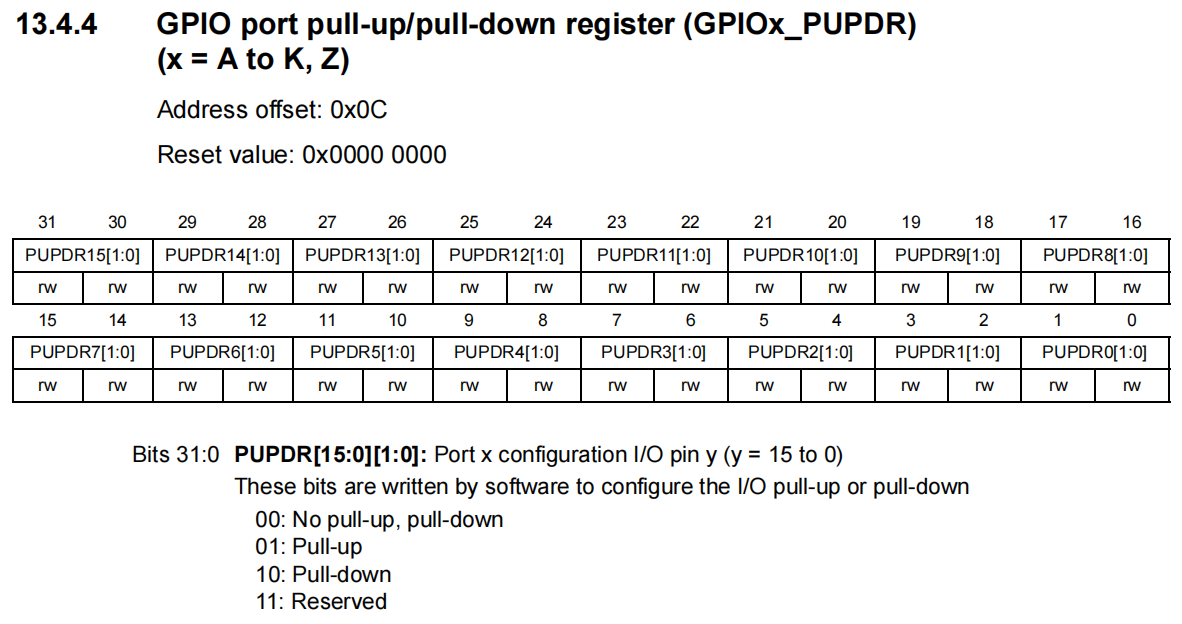

用于硬件初始化的寄存器:

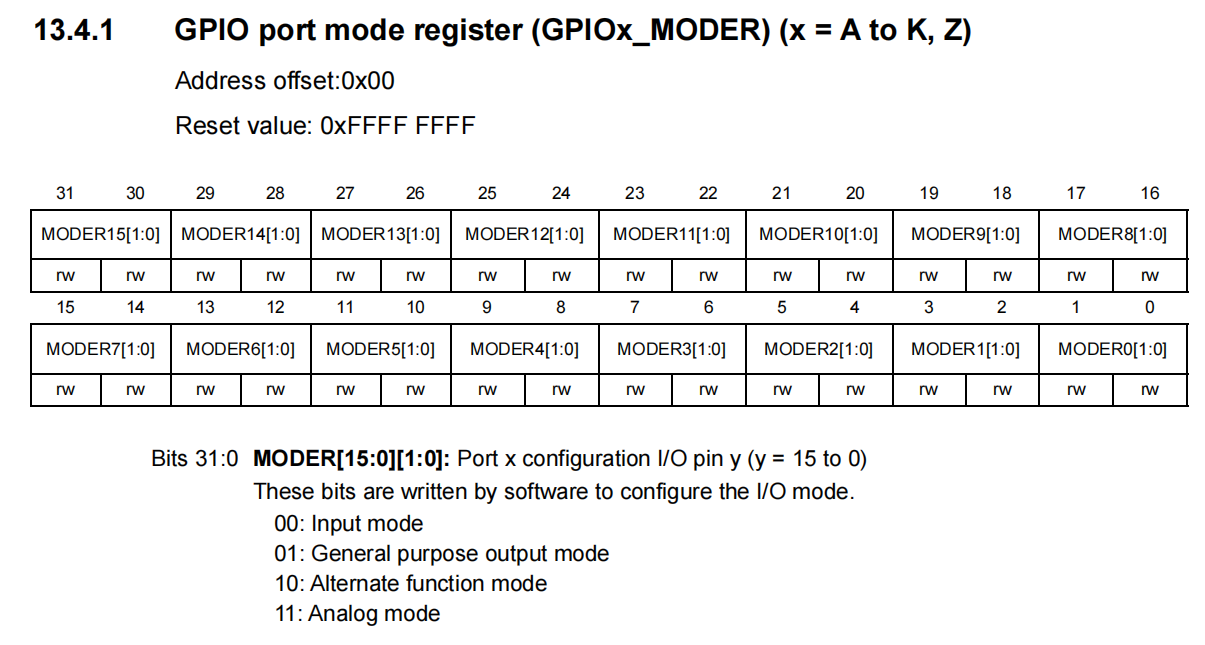

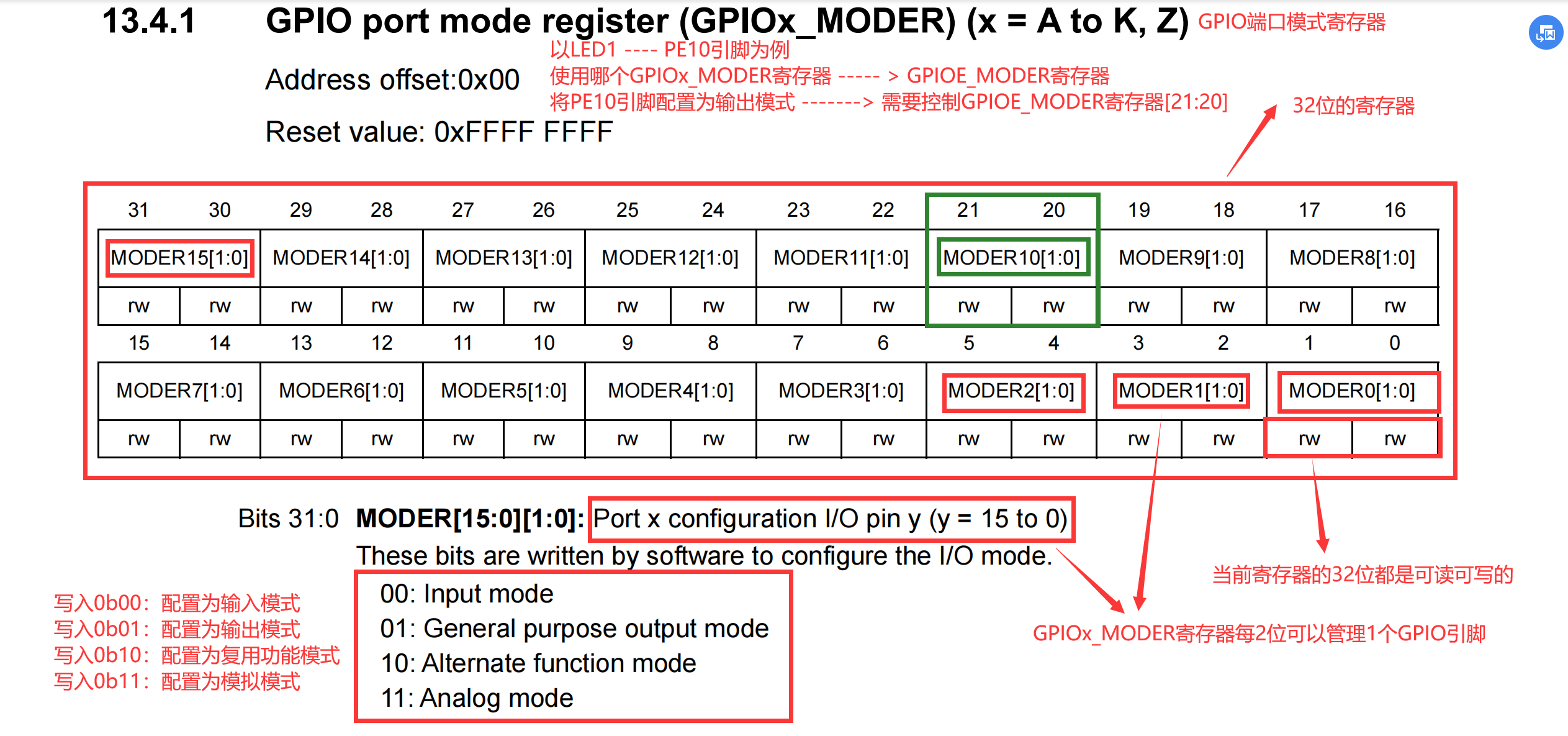

- GPIOx_MODER寄存器 用于GPIO工作模式的选择

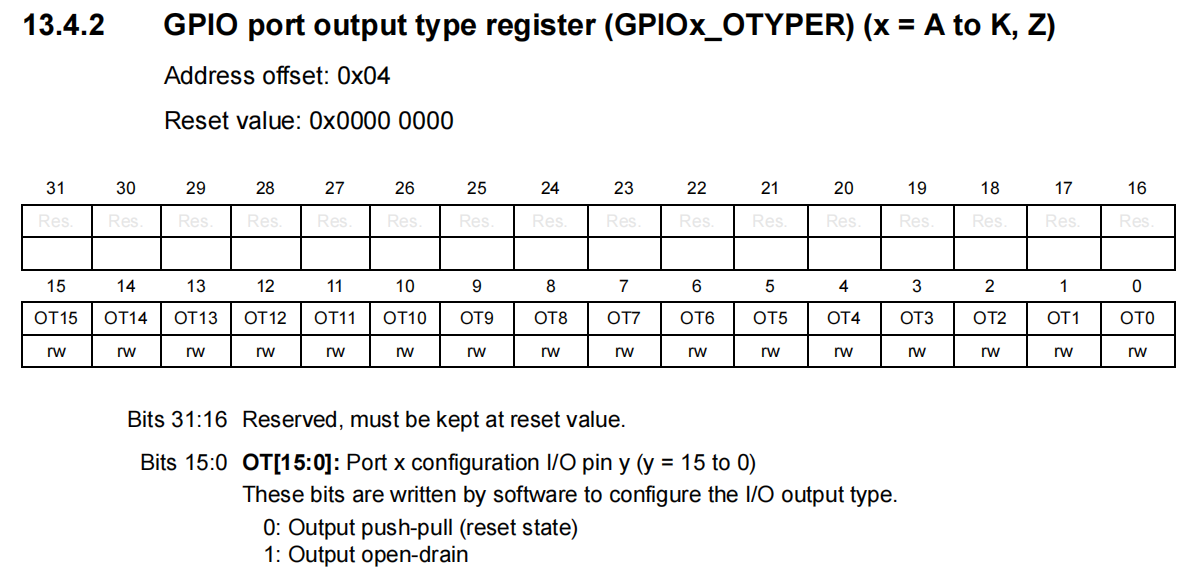

- GPIOx_OTYPER寄存器 用于GPIO输出模式的类型选择

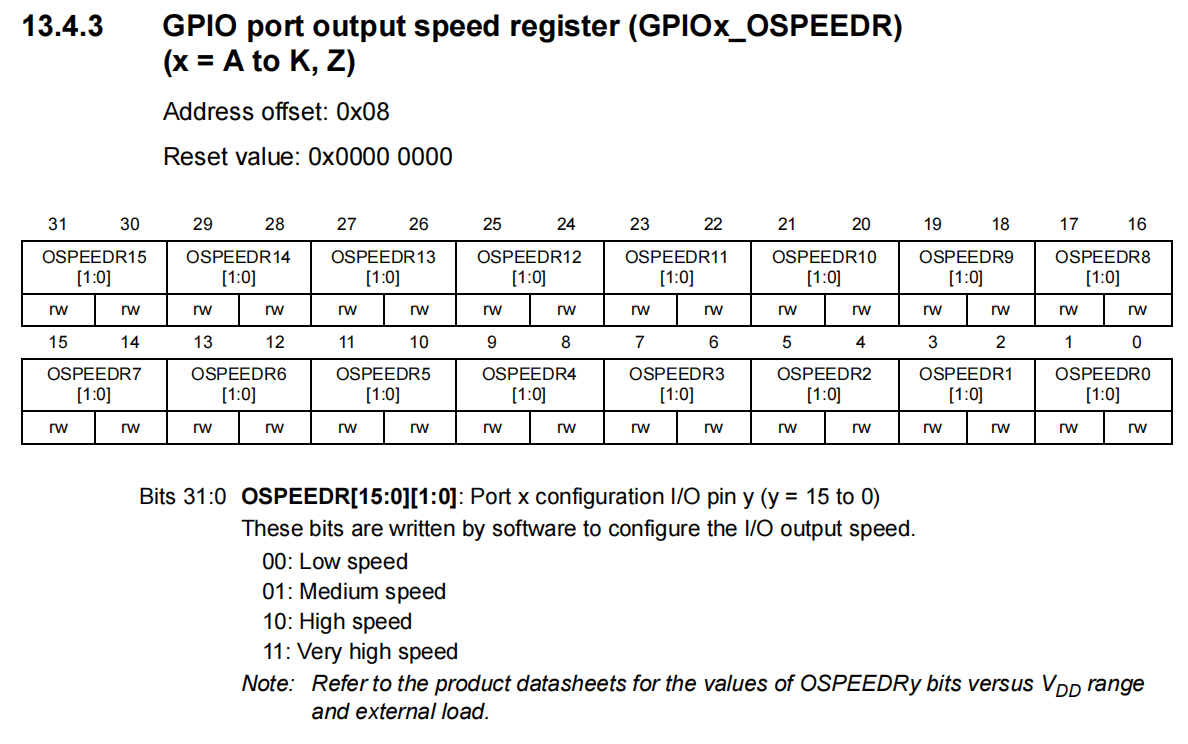

- GPIOx_OSPEEDR寄存器 用于GPIO输出模式的速率选择

- GPIOx_PUPDR寄存器 用于配置GPIO引脚是否外接上拉/下拉电阻

GPIO 端口数据存储器

GPIOx_ODR 寄存器用于存储需要被输出的数据(高低电平信号)

输入的数据先被存储到 GPIOx_IDR 寄存器中

GPIOx_ODR寄存器用于存储待输出数据,若要输出数据,将其写入该寄存器即可;

GPIOx_IDR寄存器用于存储输入数据,若要获取输入数据,从该寄存器读取即可。

控制LED1灯

目的:想要通过PE10引脚控制LED1灯工作/不工作 ---> 向PE10引脚输出高电平/低电平信号

解决:

/********************硬件初始化工作 - 只需要做1次即可*********************/

通过GPIOx_MODER寄存器配置PE10引脚为输出模式

通过GPIOx_OTYPER寄存器配置PE10引脚为推挽输出模式

通过GPIOx_OSPEEDR寄存器配置PE10引脚为低速输出模式

通过GPIOx_PUPDR寄存器配置PE10引脚为不需要外接上下拉电阻模式

/********************逻辑处理工作 - 可以写在while(1)*********************/

通过GPIOx_ODR寄存器可以输出高电平(1)/低电平信号(0)

向GPIOx_ODR寄存器中写入0b1 ------- 可以实现高电平信号的输出

向GPIOx_ODR寄存器中写入0b0 ------- 可以实现低电平信号的输出

GPIO 端口模式寄存器

如图所示,以 LED1 ---- PE10 引脚为例

使用哪个 GPIOx_MODER 寄存器 -----> GPIOE_MODER 寄存器

将 PE10 引脚配置为输出模式 -------> 需要控制 GPIOE_MODER 寄存器 [21:20]

当前寄存器的 32 位都是可读可写的

GPIOx_MODER 寄存器每 2 位可以管理 1 个 GPIO 引脚

将PE10配置为输出模式

目的:将PE10配置为输出模式

解决:

- PE10的E得到当前引脚属于 GPIOE 组,需要使用 GPIOE_MODER 寄存器

- PE10的10得到当前引脚为第 10 号引脚,需要使用 GPIOE_MODER 寄存器中的[21:20]

- 配置为输出模式 -------> 需要写入 0b01

任务

/********************硬件初始化工作 - 只需要做1次即可*********************/

通过GPIOx_MODER寄存器配置PE10引脚为输出模式

通过GPIOx_OTYPER寄存器配置PE10引脚为推挽输出模式

通过GPIOx_OSPEEDR寄存器配置PE10引脚为低速输出模式

通过GPIOx_PUPDR寄存器配置PE10引脚为不需要外接上下拉电阻模式

*

/********************逻辑处理工作 - 可以写在while(1)*********************/

通过GPIOx_ODR寄存器可以输出高电平(1)/低电平信号(0)

向GPIOx_ODR寄存器中写入0b1 ------- 可以实现高电平信号的输出

向GPIOx_ODR寄存器中写入0b0 ------- 可以实现低电平信号的输出

需要使用哪些寄存器的哪些位可以实现上述效果?

配置 PE10 引脚为输出模式 - 向 GPIOE_MODER 寄存器 [21:20] 写入 0b01

配置 PE10 引脚为推挽输出模式 - 向 GPIOE_OTYPER 寄存器 [10] 写入 0b0

配置 PE10 引脚为低速输出模式 - 向 GPIOE_SPEEDR 寄存器 [21:20] 写入 0b00

配置 PE10 引脚为不需要外接上下拉电阻模式 - 向 GPIOE_PUPDR 寄存器 [21:20] 写入 0b00