**

写在前面

**

大家好,我是司晔,从毕业以来工作一段时间了,一直想把公众号做起来也没挤出时间来搞,时间已经很久了,我想是时候动手了。首先说明的是在这里主要分享关于IC开发的一些知识和见解,小弟才疏学浅,本号对于小白以及学生党帮助更多一些,对于经验丰富的前辈和资深工程师们可能只是小秀。总之,欢迎各位好友前辈指教。好了,话不多说进入正题。

前 言

之前,在我硕士期间,主修的是FPGA方向,由于各个原因转到了IC方向,大同小异,个人认为主要是verilog编码熟悉精通就好,其他的就是工具和复杂度问题了,大家都知道,由于国内芯片问题,IC行业掀起了很大的浪潮,因此IC行业近几年还是比较热门的。其中对CPU开发有大家都看齐的一个方向,那就是它的架构,现在国际上CPU的架构很多,但大多都需要购买版权才可以使用,如ARM,X86。直到2010年,美国加州大学伯克利分校开发了RISC-V指令集架构,这是一款完全开源的架构,任何人都可以完全免费地使用它而不需要任何费用和版权问题。

但RISC-V诞生后,并不被很多人所知晓,直到2020年左右才在国内兴起,随之有很多芯片公司为它而建,又随着国内芯片短缺问题,萌芽了太多的芯片开发初创公司。

RISC-V,即精简指令集处理器,是与X86这些CISC,即复杂指令集处理器,相对的。V是罗马数字,也就是第五代RISC了,它的到来也注定是一个时代的到来了。

对RISC-V指令集,官方主要给出了两个描述文档,一个是非特权文档,一个是特权文档,这两种说明有本质的区别。非特权指令主要是用于通用计算,站在操作系统的角度来看,可以理解为用户态(低权限模式)能够运行的指令。而特权指令,是为了能够运行像 Linux/Windows 现代操作系统而设定的。现代操作系统主要强调对资源的管控,这就需要硬件上提供额外的权限管理机制,从而能够限制普通应用代码的行为。在这里主要以非特权指令为主介绍,后面有时间也会提特权指令,慢慢来。

初识RISC-V

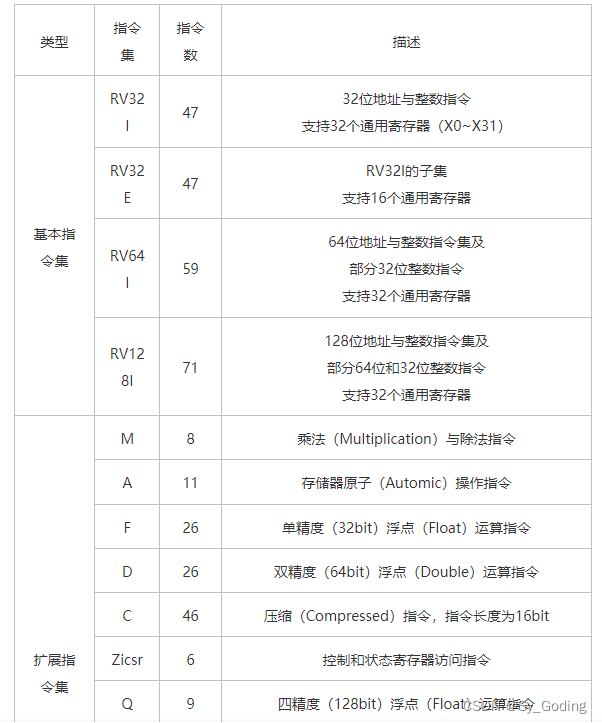

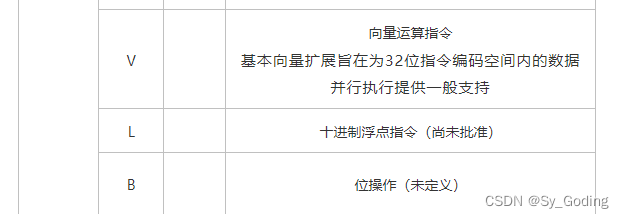

RISC-V指令集采用模块化的方式进行组织设计,由基本指令集和扩展指令集组成,每个模块用一个英文字母表示。在RISC-V中,有很多的指令集类型,如下:

其中,用**“G”表示特定组合“I”,“M”,“A”,“F”,“D”**。如用RV32G表示RV32IMAFD。

RV32I,定义了32个通用寄存器x0~x31,各为32bit宽度,其中x0为固定值,恒为0,其余为读/写寄存器。RV32I也是必须实现的指令。

基本的指令集架构定义比较简单,实现也相对容易些,都是些老生常谈的东西了,今后我们主要对"V"扩展,即向量指令集进行研究和实现,"V"扩展的标准和实现相对复杂些,会涉及到向量整型,向量定点、向量浮点、向量掩码、向量缩减等指令;还会涉及一些标准,如IEEE754标准,后面也会分章节讲到。当你把向量扩展的指令实现的很好的时候,其他基本指令也基本没啥问题了。

**

总结

**

RISC-V在国内的热度还在增长,对于IC开发,对RISC-V的研究和实现是非常必要的,从本章开始,我就RISC-V的向量扩展以及IEEE754的各部分进行讲解,并一步一步进行实现,希望感兴趣的好友前辈多多指教。

那么好,时间有限,今天只是初探,我们后续再见。