1 基础知识

ESP32-WROOM-32

ESP32-WROOM-32模块搭载的核心芯片型号为 ESP32-D0WDQ6

内置 512KB SRAM,外扩 4MB SPI Flash

ESP32:表示乐鑫公司的这一系列芯片产品,具有 Wi-Fi 和蓝牙功能,可用于物联网设备的开发等多种场景。

D0:通常表示芯片的封装形式或一些基础特性的标识。在 ESP32 系列中,不同的封装形式会有不同的代号,D0 可能代表了一种特定的封装类型,这种封装决定了芯片的引脚布局、尺寸等物理特性,以便适应不同的应用场景和电路板设计要求。

W:代表 Wi-Fi 功能,说明该芯片支持 Wi-Fi 通信协议,能够连接到无线网络,实现设备与互联网或其他网络设备之间的数据传输。

D:代表蓝牙功能,表明芯片集成了蓝牙模块,支持蓝牙通信,可用于与其他蓝牙设备进行短距离无线数据传输,比如连接手机、蓝牙传感器等。

Q6:可能是芯片的特定版本号或生产批次等相关标识,用于区分同一类型芯片在功能、性能或其他方面的细微差异,或者用于标识不同的生产批次,以便于生产管理和质量控制。

boot loader一般在0x1000开始的位置。

Flash的话,0x9000到0xD000是数据区,0xD000到0xF000是ota数据区,0xF000到0x10000是phy数据区,0x10000往后是工厂程序区和其他分区。

乐鑫芯片

ESP32-S3结构

ESP32-32资源

ESp32命名

ESP32-S3-WROOM-1功能框图

地址映射

内存

上图①: Internal ROM(384KB)是只读存储器、不可编程 ,用来放系统底层的固件。

上图②: Internal SRAM(512 KB)是易失性存储器,可以快速响应 是易失性存储器,可以快速响应 是易失性存储器。

上图④和⑥: 上图④和⑥: 上图④和⑥: RTC Memory(16 KB)RTC 存储器以静态以静态 RAM(SRAM)方式实现。

外存

CPU 借助高速缓存(Cache)来访问外部存储器。 Cache 将根据内存管理单元(MMU)中的信息把 CPU 指令总线或数据总线的地址变换为访问片外 flash与片外 RAM 的实地址。

最大支持 1 GB 的片外 flash与 1GB 的片外 RAM。

外设

GDMA

GDMA 共有 10个独立的通道,其中包括 5个接收通道和 5个发送通道。这10 个通道被支持 GDMA 功能的外设所共享。

管脚

ESP32-S3 芯片有 45 个物理通用输入输出管脚(GPIO Pin)。

- 45 个物理 GPIO 管脚的编号为 0~ 21、26~ 48

- 模组只有 36 个实际引脚的物理 GPIO 管脚

- 因为该模组的 Flash 和 PSRAM 使用了八线 SPI即 Octal SPI 模式,这些模式共占用了 12 个 GPIO 管脚。

- 该模组还将 IO35、IO36、IO37引出,所以最终的管脚数量为 45-12+3

可配置外设模块的输入信号来源于任何的 GPIO 管脚,并且外设模块的输出信号也可连接到任意 GPIO 管脚

flash和PSRAM

SRAM(ns)比PSRAM快几倍,PSRAM要远高于ROM。

复位

四种级别的复位方式,分别是CPU复位、内核复位、系统复位和芯片复位。

ESP32-S3上电复位时,它的复位源为芯片复位

ESP32-S3上电复位时,它的复位源为芯片复位

ESP-ROM:esp32s3-20210327

Build:Mar 27 2021

rst:0x1 (POWERON),boot:0xb (SPI_FAST_FLASH_BOOT)

SPIWP:0xee

mode:DIO, clock div:1

load:0x3fce3810,len:0x17c0

load:0x403c9700,len:0xd7c

load:0x403cc700,len:0x300c

entry 0x403c992c

时钟

来源于8M的和40M的低高速晶振。

主频频率是由寄存器SYSTEM_SOC_CLK_SEL决定

Boot

strapping管脚,固定配置管脚。

启动模式

BOOT0 引脚的电平状态与其他相关引脚(如 BOOT1)的电平状态组合,决定了微控制器从何处读取启动代码。

BOOT0 引脚的电平状态与其他相关引脚(如 BOOT1)的电平状态组合,决定了微控制器从何处读取启动代码。

ESP32 启动模式为“SPI BOOT”是说从SPI flash启动。

内部闪存启动:这是最常用的启动模式。一般情况下,BOOT0 引脚接地(电平为 0),微控制器会从内部闪存中读取用户编写的程序代码并开始执行,适合设备正常运行阶段。

系统存储器启动:当 BOOT0 引脚接高电平(电平为 1),且 BOOT1 引脚配置为特定状态(通常为低电平)时,微控制器会从系统存储器启动。系统存储器中存放着厂商预装的引导程序,用于实现一些特定功能,如通过串口等方式对内部闪存进行程序烧录,即通常所说的在系统编程(ISP)功能。

SRAM 启动:某些情况下,可通过设置 BOOT0 和 BOOT1 引脚的电平组合来选择从 SRAM 启动。这种模式一般用于特殊调试或实验场景,因为 SRAM 掉电后数据会丢失,所以不会作为常规的启动方式。

中断

ESP32-S3 具有 99 个外部中断源,但每个 CPU 只有32 个中断。

实际上,CPU0 和 CPU1 的外部中断只有 26 个,剩下的 6 个中断均为内部中断。

启动流程

①:一级引导程序,它被固化在 ESP32-S3 内部的 ROM 中,它会从 flash 的 0x00 处地址加载二级引导程序至 RAM中。

- 不可查看,不可修改

- 做一些前期的准备工作(复位向量代码),然后从 flash 0x00 偏移地址中读取二级引导程序文件头中的配置信息

②:二级引导程序从 flash 中加载分区表和主程序镜像至内存中,主程序中包含了 RAM 段和通过 flash 高速缓存映射的只读段。

- 可被修改和查看

- bootloader_start.c 文件

③:应用程序启动阶段运行,这时第二个 CPU 和 freeRTOS 的调度器启动,最后进入app_main函数执行用户代码。

D:\AppInstall\EspInstall\Espressif\frameworks\esp-idf-v5.3

加载到VSCode

- \components\bootloader/subproject/main/路径下找到 bootloader_start.c 文件,二级引导程序启动处。由一级引导调用。

- call_start_cpu0 函数,bootloader程序

- /components/esp_system/port/路径下的 cpu_star.c文件的call_start_cpu0 函数 ,由二级引导加载程序执行,并且从不返回。因此你看不到是哪个函数调用了它,它是从汇编的最底层直接调用的。

- components\esp_system\startup.c 文件下调用 start_cpu0系统层初始化函数,到了这里,就完成了二级程序引导

- 调用 esp_startup_start_app 函数进入三级引导程序

2 ESP-IDF

ESP - IDF(Espressif IoT Development Framework)是乐鑫为其旗下的 ESP32、ESP32 - S 系列、ESP32 - C 系列等芯片专门打造的物联网开发框架。

ESP-IDF编译系统流程

编译过程主要基于 Make 或 CMake 构建系统

esp-idf 文件夹

-

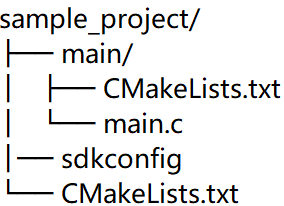

IDF工程

ESP-IDF 工程借助 CMake 的可自定义性,创新地采用了“组件”式的设计。整个工程由多个组件组成,每个组件都像是一块积木,共同构建起完整的工程结构。

- “main”组件,它包含了用户应用程序的入口函数。

- 项目配置 保存在项目根目录下名为 sdkconfig的文件中,一个项目只能包含一个项目配置。

- 应用程序是由 ESP-IDF 构建得到的可执行文件。一个项目通常包含项目应用程序和引导程序。

- 组件(Components)是模块化且独立的代码,会被编译成静态库(.a 文件)并链接到应用程序。

- ESP-IDF 并不是项目的一部分,它独立于项目,通过 IDF_PATH 环境变量(保存 esp-idf 目录的路径)链接到项目

项目工程分析

顶层项目 CMakeLists.txt 文件

- CMake 用于学习如何构建项目的主要文件。

- 这个文件中设置项目全局的 CMake 变量

- CMakeLists.txt 文件会导入 /tools/cmake/project.cmake 文件, 由它负责实现构建系统的其余部分。

如下代码所示:

/* 必须放在 CMakeLists.txt 文件的第一行,

它会告诉 CMake 构建该项目所需要的最小版本号。ESP-IDF 支持 CMake 3.16 或更高的版本 */

cmake_minimum_required(VERSION 3.16)

/* 会导入 CMake 的其余功能来完成配置项目、检索组件等任务 */

include($ENV{IDF_PATH}/tools/cmake/project.cmake)

/* 会创建项目本身,并指定项目名称 */

project(myProject)

idf_component_register(SRCS "main.c" INCLUDE_DIRS ".")

- 调用 idf_component_register 函数,开发者可以将组件添加到构建系统中。

- SRCS 代表源文件列表,其中包括 .c、.cpp、.cc、.S 等类型的文件

main 目录 main.c定义了程序入口函数 app_main()

“sdkconfig” 项目配置文件,执行 idf.py menuconfig 时会创建或更新此文件,文件中保存了项目中所有组件(包括 ESP-IDF 本身)的配置信息。

3 GPIO

ESP-IDF 提供了丰富的 GPIO 操作函数

esp-idf-v5.1.2\components\driver\gpio路径下找到相关的 gpio.c 和 gpio.h 文件

配置 GPIO 的模式、上下拉等功能,其函数原型如下所示:

esp_err_t gpio_config(const gpio_config_t *pGPIOConfig)