这是本篇文章的设计目标如下所示:

这个Counter模块是一个LED 闪烁计数器,设计目标是:

当输入时钟clk为 50 MHz 时,每 0.5 秒翻转一次 LED 灯状态。随后我们开始补充理论知识。

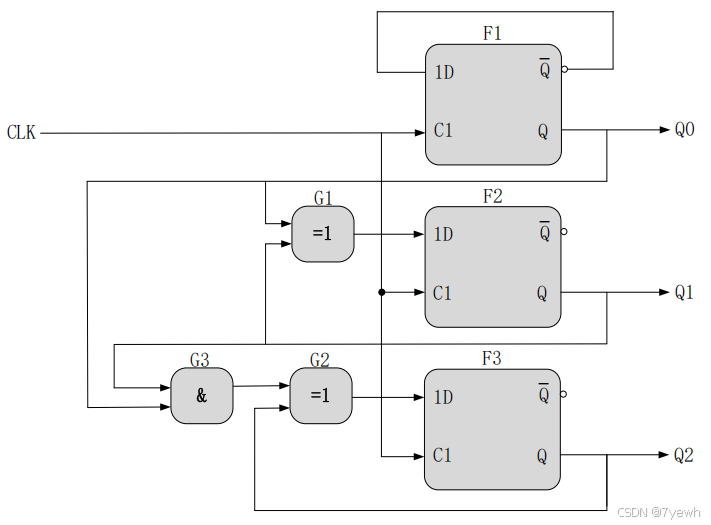

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路。下面我们以一个 3 位计数器来学习下计数器的基本组成和相关知识,首先我们画出 3 位计数器的电路结构图。

我们以 F1 、 F2 、 F3 代表 3 个 D 触发器,两个异或门 G1 、 G2 和 1 个与门 G3 来进行说明计数器是如何工作的。一般触发器是有复位信号(图中没有画出),在上电复位之后,电路上电的 Q0 Q1 Q2 初始状态是 000,下面我们来看下这三个D 触发器此时的输入信号是什么。

我们先看 F1 , F1 的输入信号 D ,是由 Q0 反馈回来的,我们已知此时的 Q 是 0 ,那么 ` Q 就是 1 ,这个 1 反馈给 F1 输入信号 D ,此时 F1 的输入信号就是 1 。

下面我们再来看 F2 , F2 的输入信号是 Q0 和 Q1 的值经过一个异或门之后得到的,我们已知此时的 Q0 是 0 , Q1 也是 0 ,那么这两个 0 经过异或门逻辑处理(异或门两个输入信号值相同输出 0 ,不同输出 1 )后就是 0 了,因此 F2 的输入信号也是 0 。

再看 F3,F3 的输入信号是由 Q0 和 Q1 经过一个与门之后的输出值,与 Q2 的值相异或得到的,我们来看,Q0 和 Q1 都是 0,两个 0 相与,输出肯定还是 0,这个输出的 0,再与 Q2 的值相异或,根据异或门的规律,两个输入现在都是 0,那么异或门的输出也是 0,F3 的输入此时就是 0。

到这里,我们已经分析出了 F1 、 F2 和 F3 这三个触发器此时的输入值了,下面我们就可以根据 D 触发器的逻辑规律知道下一刻电路的输出值了,现在我们给 CLK 端口一个上升沿,也就是 CLK 由 0 变为 1 了,那么 3 个边沿 D 触发器将会同时触发,当 CLK 这个时钟信号的上升沿到来时, D 触发器的输入值将会被锁存,根据逻辑规律,下一刻 3 个 D 触发器的输出值就分别为 1 , 0 , 0 。这里如果我们把 Q2 的值当

做二进制数的最高位,把 Q0 的值当做二进制数的最低位,那么现在计数器所输出的值,就是二进制数 001,也就是十进制的 1 。计数器接收到第一个时钟信号的上升沿后,计数器就输出二进制数 001 ,依次类推,如果第二个时钟信号的上升沿到来时,这个时候计数器将会输出二进制数 010 ,也就是十进制数 2 , 每当电路多到来一个时钟上升沿,计数器就会作加 1 运算。当电路计到第 8 个脉冲时,电路状态将由 111 又变为 000 ,完成一个循环周期,所以该电路也称为模 8 同步加法计数器。所谓同步就是指该电路中的四个边沿型 D 触发器共用一个时钟脉冲 CLK ,当时钟上升沿到来时,它们能够同时触发。

| 时钟沿数 | Q2 | Q1 | Q0 | 二进制值 | F3_D输入 | F2_D输入 | F1_D输入 |

|---|---|---|---|---|---|---|---|

| 初始 | 0 | 0 | 0 | 000 | 0 | 0 | 1 |

| ↑1 | 0 | 0 | 1 | 001 | 0 | 1 | 0 |

| ↑2 | 0 | 1 | 0 | 010 | 0 | 1 | 1 |

| ↑3 | 0 | 1 | 1 | 011 | 1 | 0 | 0 |

| ↑4 | 1 | 0 | 0 | 100 | 0 | 1 | 1 |

| ↑5 | 1 | 0 | 1 | 101 | 1 | 1 | 0 |

| ↑6 | 1 | 1 | 0 | 110 | 1 | 0 | 1 |

| ↑7 | 1 | 1 | 1 | 111 | 0 | 0 | 0 |

| ↑8 | 0 | 0 | 0 | 000 | 0 | 0 | 1 |

| ... | … | … | … | … | … | … | … |

Q0, Q1, Q2 分别是 F1, F2, F3 的输出;

F1_D输入 = ~Q0,即直接来自 Q0 的反向;

F2_D输入 = Q0 ^ Q1;

F3_D输入 = (Q0 & Q1) ^ Q2。

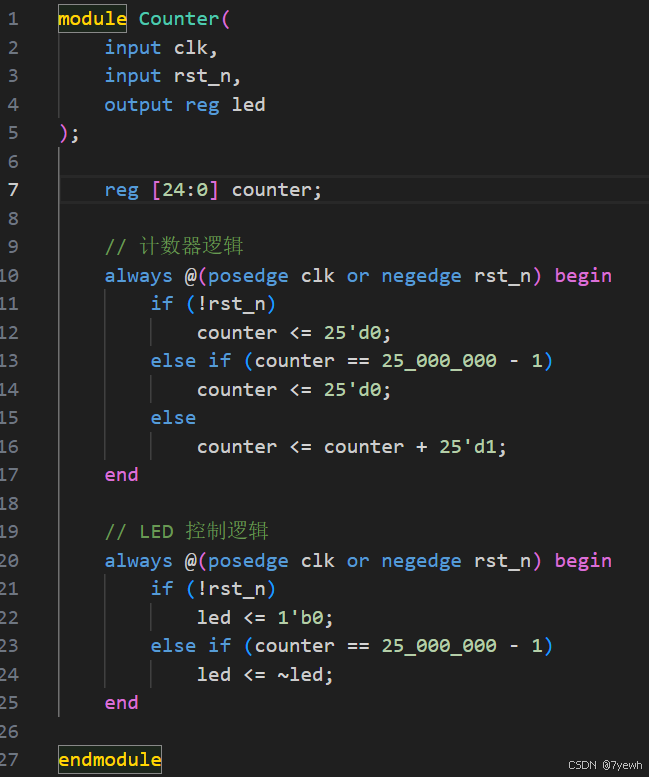

接下来就是程序设计了,如下所示:

| 信号名 | 类型 | 说明 |

|---|---|---|

clk |

input |

时钟信号(假设为50 MHz) |

rst_n |

input |

异步低电平复位信号 |

led |

output reg |

控制LED状态,高亮或熄灭 |

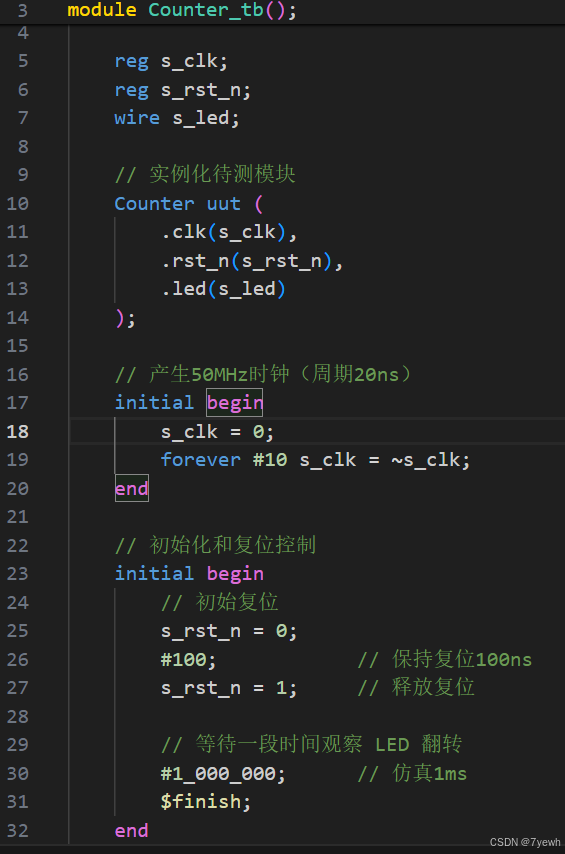

这个 Testbench 的目标是:

给 Counter 模块提供时钟和复位信号;

观察 LED 信号是否按照设计(每经过一定计数周期翻转)工作;

进行一次完整的仿真,并在仿真 1ms 后结束。

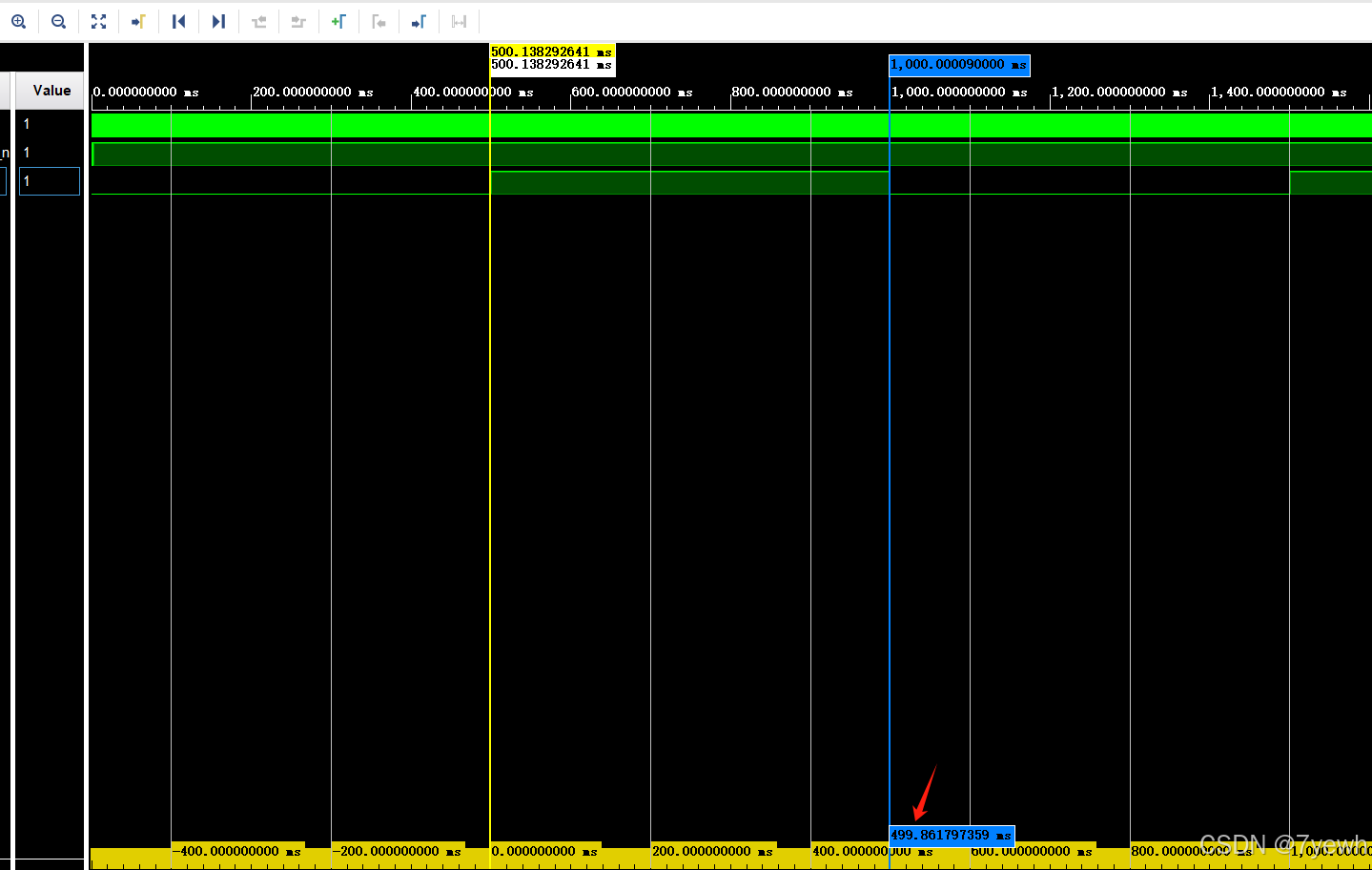

接着我们回到Vivado,如下所示仿真效果可见。