S IP物理层讲解

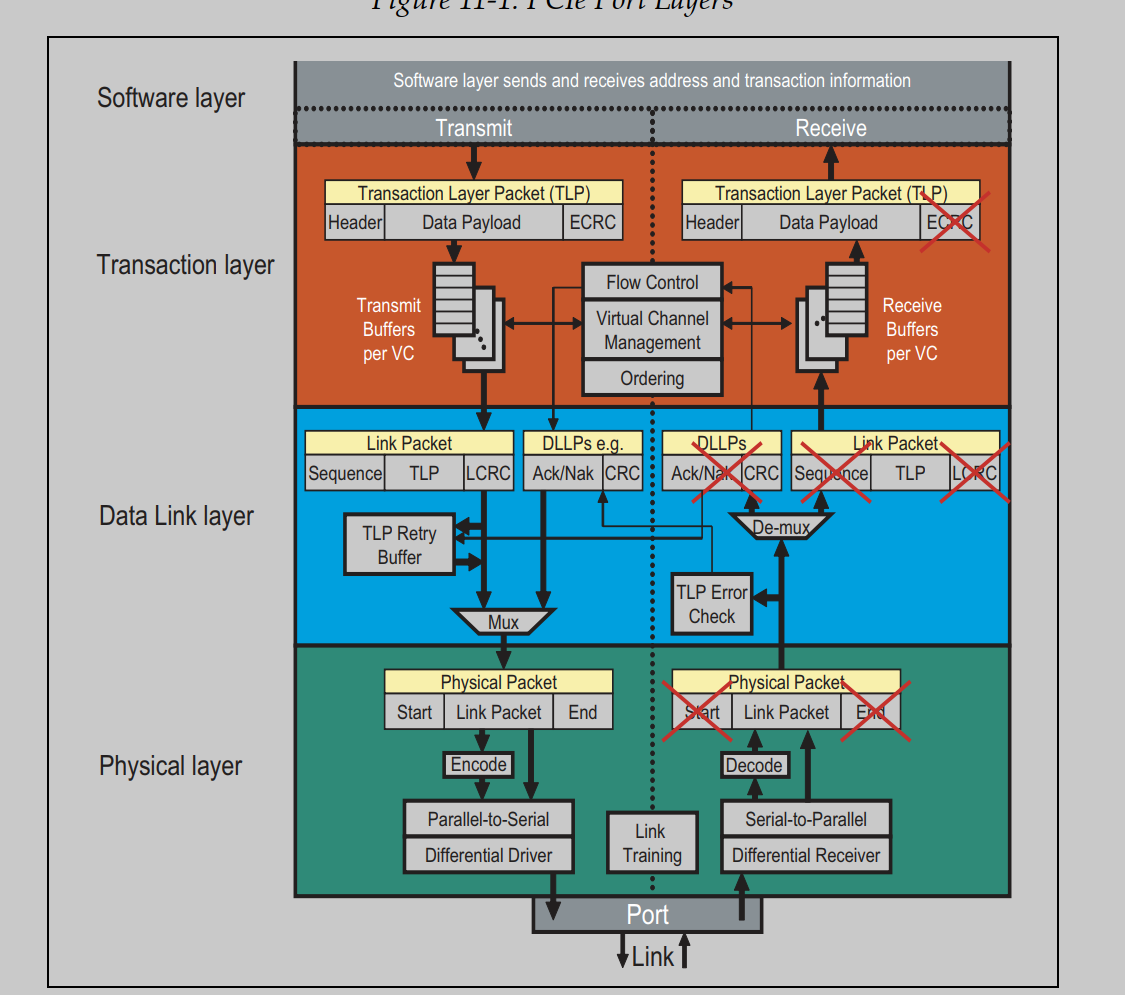

在synopsys IP中对于phy层的内容分离的比较多:

cxpl中:

u_cx_phy_logical:包含ts序列的解析(smlh); pipe层协议的转换(rmlh,xmlh);pipe转dllp包(rplh,xplh);

upcs:package(mac_phy,phy_mac) 以及phy status转pipe协议;pclk_rst;

pcs: digital: pipe转 pcie phy data; aon: mplla+mpllb,分频倍频; ropll;

pma:mplla,b; ropll; lane analog;

tx: 3-tap FFE(course -1,+1,0); feed-forward equalization; post-emphasis;

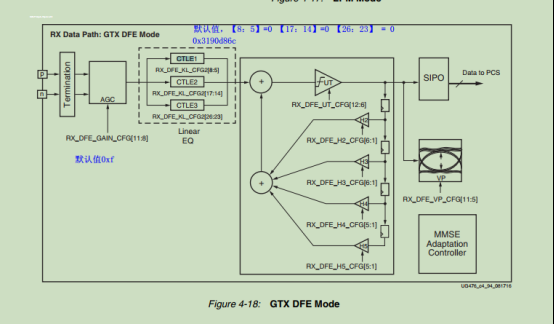

RX: ctle,VGAs, 12-tap DFE,(判决反馈均衡);

xilinx phy RX:

fpga TX结构整体比较简单。

原因:xilinx fpga pcie只支持gen3 以下的速率; 所以没有TX FFE;且RX DFE 抽头系数也不一样。

pcie 结构图;

总的来说spec只是介绍了原理单并未介绍如何实现;下文中实现内容源于Mindshare_pcie文档;以及S IP内容;

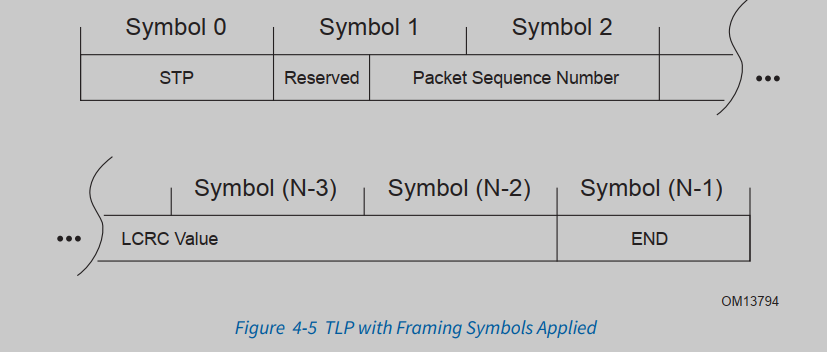

在gen1,2;中是8/10b编码;会在物理层插入STP和END包;

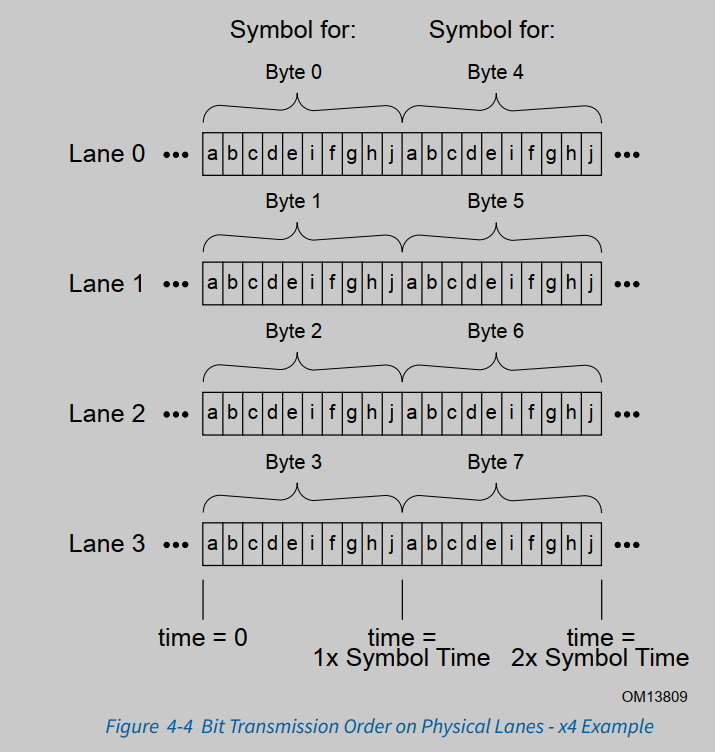

x4 lane传输示意图;在一个time周期内,4条lane会同时依次传输1Byte包(10bit);K/D 码说明;K为control 码(Kontrol),D为data 码;

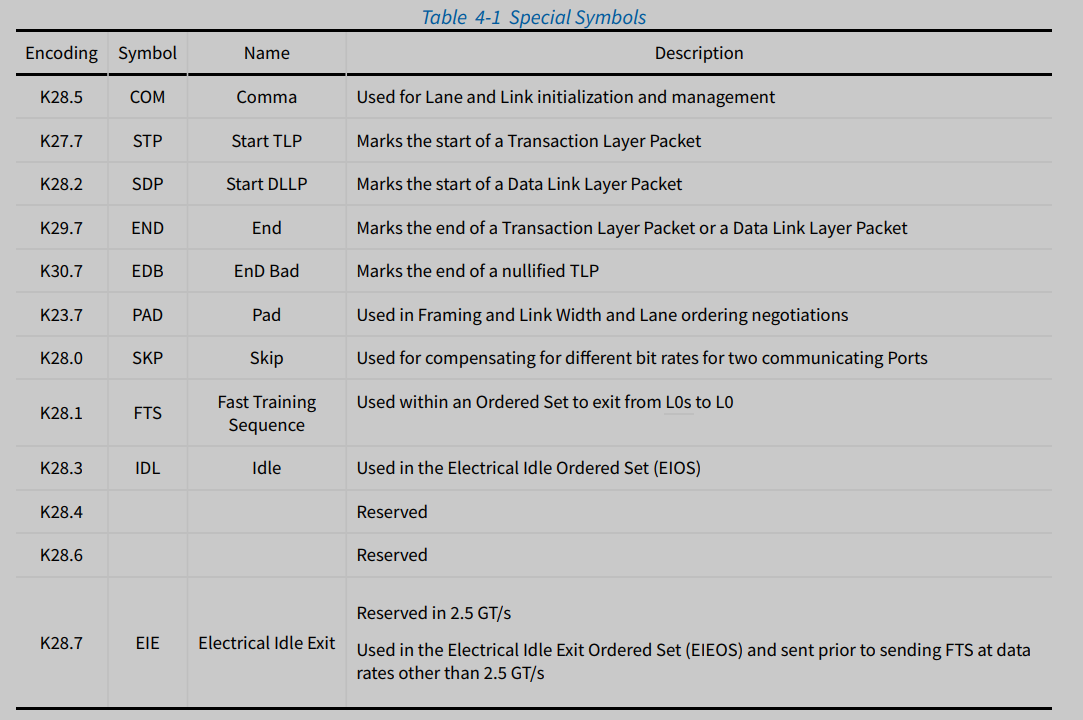

常用的K码规则:

1. S IP中K码的解码是在controller中处理的,如rdlh中提出SDP包用于分离DLLP相关内容。

D码详见附录B;分为+和-两种情况。极性需要再退出EIOS时就确认。

4.2.1.2 symbols to lanes

共有两类编码格式,order set或者 tlp ,dllp数据包。每条lane上的TS包都是串行的,所以一个完整的TS集会出现在所有lane上。STP,SDP,END三种特殊的K码用于指示pcie包。

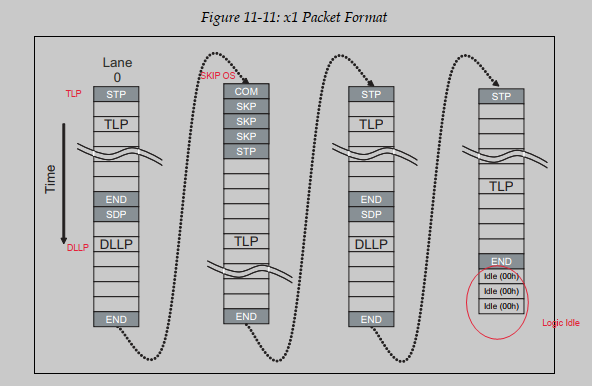

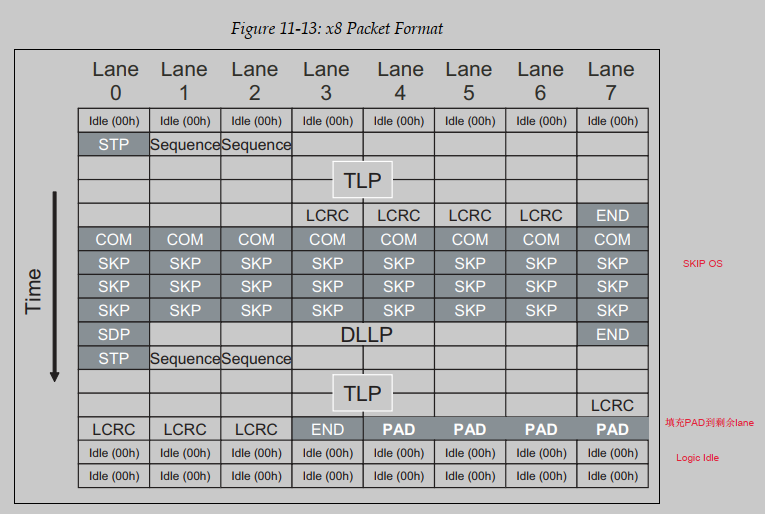

当no package info或者TS序列传输时,tx处于 logical idle state。发送idle data为全0(不同于electrical idle:一个COM+IDL),且该包应该被加入scramble;接收器接收该空闲包。SKP OS会被连续发送。

tlp编码为顺序的(在lane中传输时是并行的);

一个STP到END中至少有18个symbol,如果少于18个被认为是错包。包含sequence num,Lcrc;

For example, for x8, STP and SDP Symbols can be placed in Lanes 0 and 4; and for x16, STP and SDP Symbols can be placed in Lanes 0, 4, 8, or 12.STP只会出现在lane4*n通道上。

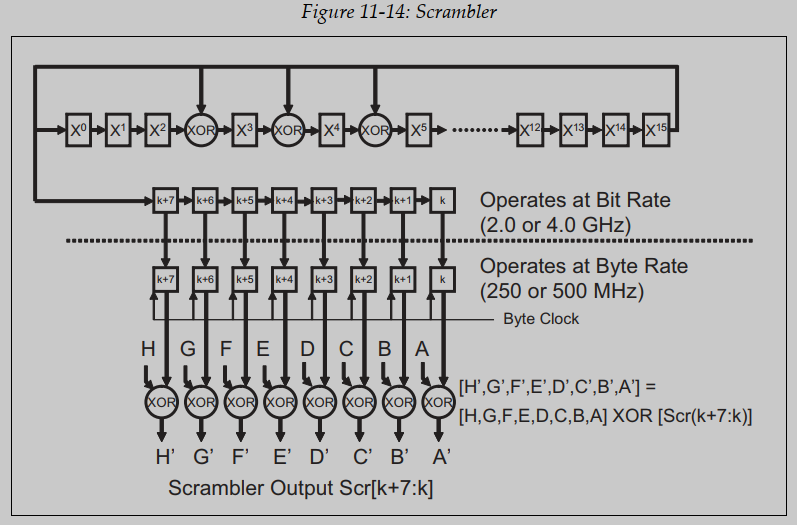

4.2.1.4 data scrambing

这一过程涉及将数据流与线性反馈移位寄存器(LFSR)生成的伪随机序列进行异或运算。在发送端,加扰操作应用于8b/10b编码之前的字符;在接收端,解扰操作则在8b/10b解码之后对字符实施。the Disable Scrambling bit in the TS1 and TS2 Ordered Sets is provided for these purposes.

x1 package 格式;

x4 格式;其中Tx中所有lane都插入SKP是为了在RX端做时钟补偿,利用elastic buffer。STP总在lane0上,END总在Lane3上。

x8 TX lane 格式。

8b/10b 编码

gen1,2支持8b/10b编码;

优势:

1. 在data中嵌入时钟:确保数据流中有足够的边沿,用于rx端时钟的恢复。编码方式会避免连续的5个bit为0或1.

2. 控制直流平衡。pice 差分信号中用一个电容进行ac耦合。在长距离传输允许tx和rx端出现共模电压不同的情况。为了避免直流漂移(DC wander),会在最后一个码发送之后记录disparity。disparity:1和0的数量差。在下一个码流中会校验这个disparity。

3.增强RX错误检测。

劣势:增加了百分之20的额外开销。

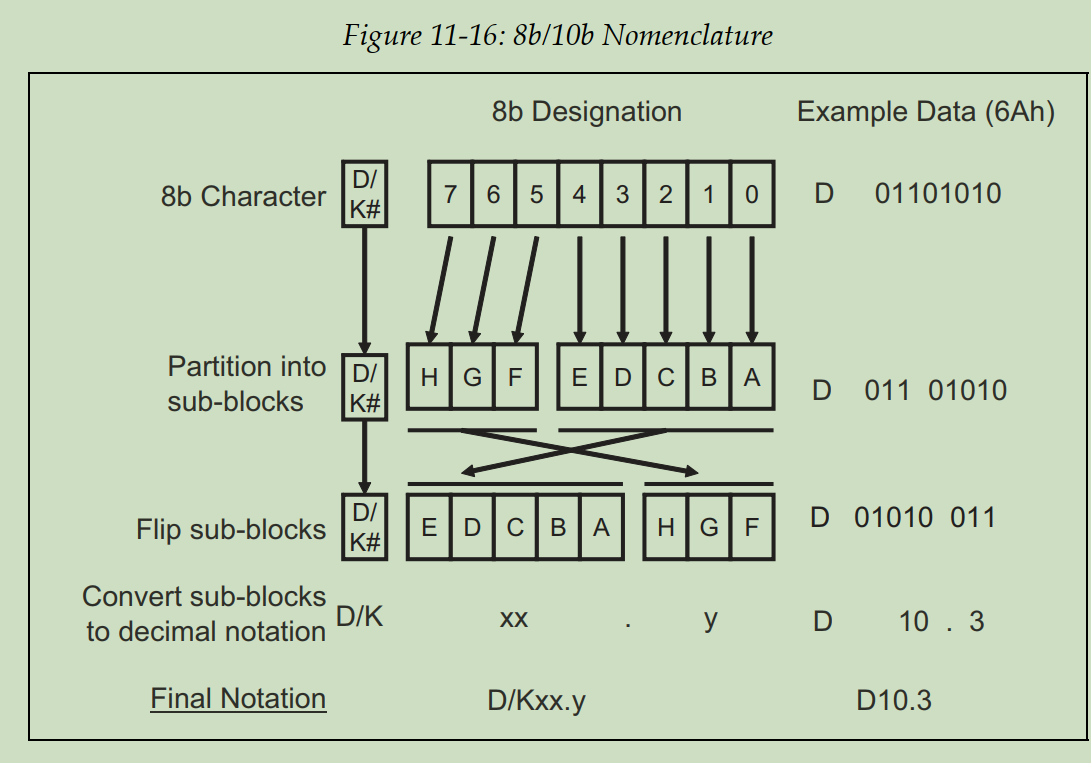

字符表示法:本质就是掉个个。用10进制方式表示。

CRD (Current Running Disparity).

CRD(Current Running Disparity) 是一个 1-bit 状态位,用来追踪当前的符号电平偏移方向(正或负);

每次编码时,8b/10b 编码器会查看当前 CRD 值,并选择一个合适的 10b 码(正或负),以保持电平平衡;

如果当前 CRD 已经是“正”(+),再发送一个“正不平衡度”的码字(带更多 1),那就违反了规则,因为:

CRD 是 1-bit 状态(只有“正”或“负”两个状态),无法表示“更正”的状态;

会导致直流漂移和非法编码状态;

这将被视为编码错误或协议违例

所以在cdr编码时就已经插入了时钟相关的信息。

8b/10b 编码方式:1. 查找表;2. 在decode是加入解码逻辑。

但是K码是一些特殊的码流,不使用解码逻辑。

特殊K码说明

COM:在物理层中的第一个symbol,用于指示order set 的起始位置。

PAD:见传输图,两种用途:1)意思是在一个包结束时,另一个包开始时,除了STP/ENDlane上会出现pad码。之后接着为idle。2) 在link training。polling状态时,对应的lane发送pad码用于确定lane number。之后会进入到configuration状态。

使用NRZ编码来传输差分信号。

logic idle和IDLE K码并不一个概念。

TX skew 允许的最大值:(在spec中为找到出处,有知道的大佬可以指正)

Gen1:500ps+2UI; UI unit interval;单位间隔,在链路中1bit传输时间;gen1 为例2.5Gbps,400ps;在官方spec中 : data rate dependent transmitter parameters 也有对TX UI的详细说明;

Gen2: 500ps+4 UI;

Gen3: 500ps+6UI;

时钟补偿

tx和rx时钟异步;一个com 码+3个SKP码,构成一个SKIP order set。在RX端有elestic buffer可以选择丢弃SKP码或者补充SKP码来动态调整buffer深度消除lane间的skew。