一、eMMC 技术深度解析

1.定义与背景

eMMC(Embedded Multi Media Card)是一种专为嵌入式系统设计的非易失性存储解决方案,它将 NAND 闪存、主控芯片和接口协议封装在一个 BGA(Ball Grid Array)封装中。其核心目标是简化系统设计、提升数据传输效率、降低功耗,并满足移动设备对存储容量和性能的不断增长需求。eMMC 由 JEDEC(固态技术协会)制定标准,目前最新版本为 eMMC 5.1,传输速率可达 400MB/s,广泛应用于智能手机、平板电脑、工控系統、電力儲能、车载系统、物联网设备等场景。

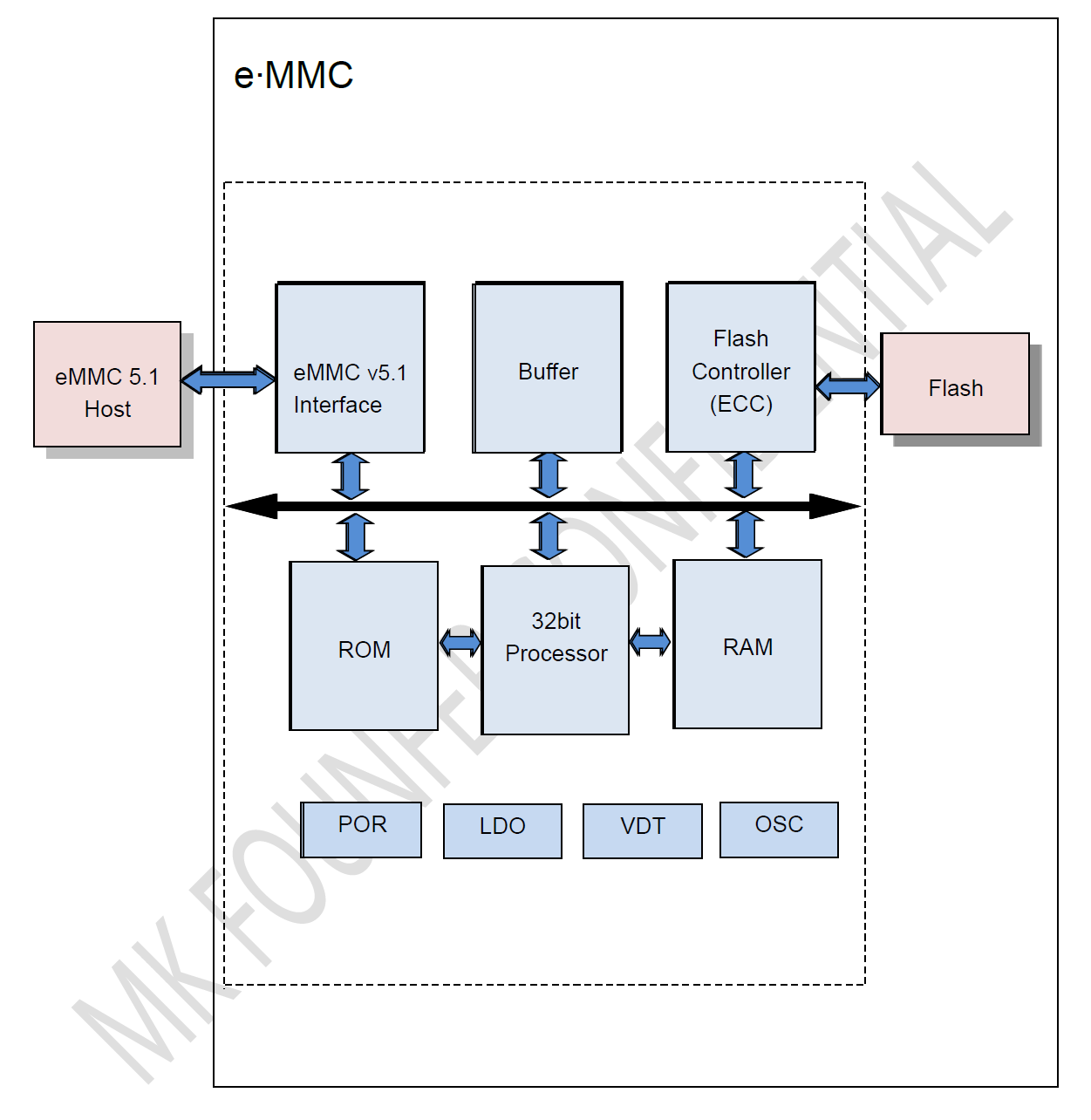

2.MK-米客方德内部架构与工作原理

(1)核心组件

- NAND 闪存阵列:存储数据核心,采用 pSLC/SLC/MLC/TLC 等制程,提供不同容量与性能选择。

- 主控芯片:管理闪存读写、坏块管理、磨损均衡(ECC 纠错、GC 垃圾回收)、协议转换(将外部命令转换为闪存操作指令)。

- 接口逻辑:兼容 MMC/SD 协议,支持 HS400、HS200 等高速模式,通过并行数据线(DAT0~DAT7)实现数据并行传输。

(2)关键技术

- 坏块管理:出厂时通过扫描标记不可用块,运行时动态监测新增坏块并更新映射表,确保数据不写入失效区域,通过映射表记录坏块位置,避免数据写入失效区域,延长闪存寿命。

- 磨损均衡算法:分为动态均衡(如基于空闲块选择)和静态均衡(如数据迁移),通过算法优化延长闪存整体寿命避免特定区块频繁擦写导致寿命提前耗尽。

- ECC 纠错机制:采用 BCH/LDPC 算法,自动纠正数据读写过程中的比特错误。

- BCH:适用于 SLC/MLC,纠错能力强但开销高。

- LDPC:适用于 TLC/QLC,纠错效率更高,支持更大容量纠错码。

数据读写流程:

- 主机发送读写命令至 eMMC 主控。

- 主控解析命令并执行地址映射,将逻辑地址转换为物理地址。

- 通过 ECC 生成校验码,并写入/读取闪存数据。

- 返回数据及状态信息至主机。

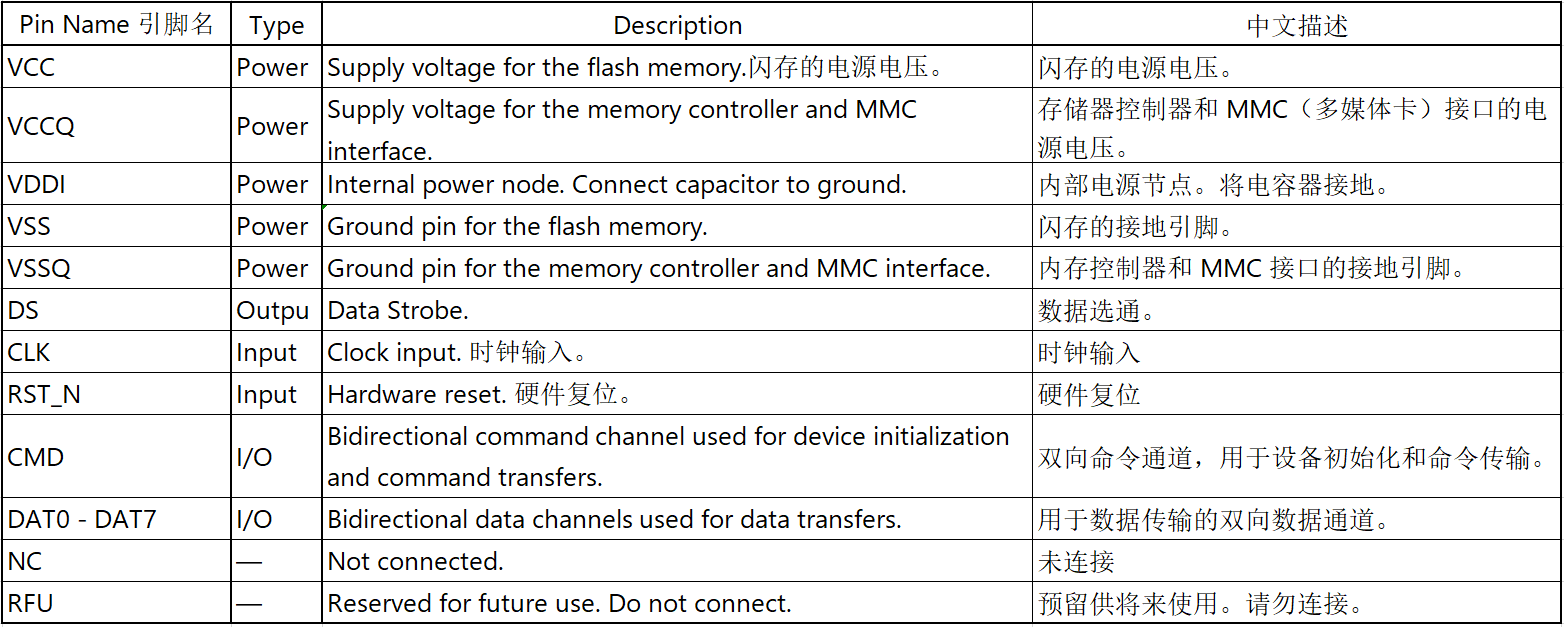

(3)通信协议-引腳介紹

米客方德 eMMC 采用基于命令/响应的异步通信机制,通过以下信号线实现数据传输:

- CLK:时钟信号,决定数据传输速率(最高支持 200MHz)。

- CMD:命令信号线,用于发送指令(如读/写、初始化、配置等)。

- DAT[0:7]:数据信号线,支持并行传输,提升带宽。

- RST_N:复位信号,低电平有效。

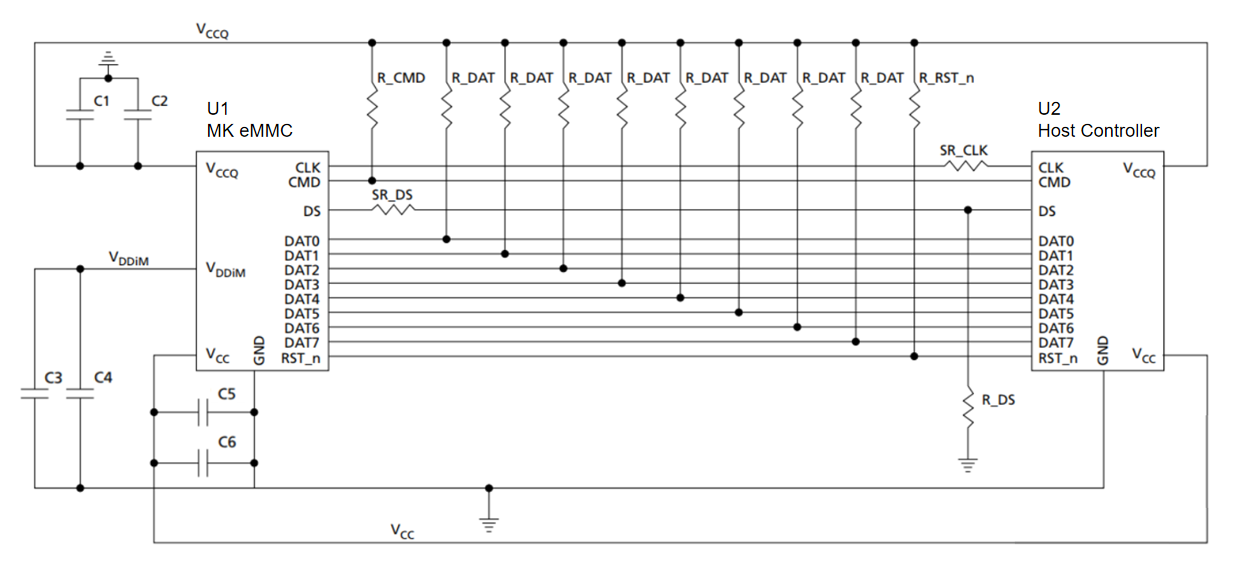

eMMC 框图

3.eMMC 版本演进与性能对比

| 版本 | 发布年份 | 最大速率 | 关键特性 |

|---|---|---|---|

| eMMC 4.3 | 2009 | 52MB/s | 支持 HS200 模式,满足早期移动设备需求。 |

| eMMC 4.5 | 2011 | 200MB/s | 引入 HS400 高速模式,支持 LPDDR 接口。 |

| eMMC 5.0 | 2013 | 400MB/s | 增强功耗管理,支持硬件加密(eMMC Security)。 |

| eMMC 5.1 | 2016 | 400MB/s | 优化随机读写性能,提升温度适应性。 |

二、MK-米客方德 eMMC 硬件电路设计详解

(一)电路设计基础

1.典型应用电路

eMMC 电路设计需关注电源、信号连接及保护,以下为典型电路示意:

eMMC 典型应用电路示意图,包含 VCC、VCCQ、VDDi、CLK、CMD、D[0:7]、RST_N 等信号,标注滤波电容、上拉电阻等。

2.电源设计

VCC(供电电源):通常为 3.3V 或 1.8V,需通过 LC 滤波电路(如 10uF+0.1uF 电容并联)抑制高频噪声。

VCCQ(IO 电源):与 VCC 相同或独立,需确保电平匹配以避免逻辑冲突。

VDDi(内部核心电源):用于主控芯片供电,需单独滤波(如 2.2uF 电容),并避免与 IO 电源共线。

3. 信号线处理

CLK 信号:需 50Ω 阻抗匹配,避免反射导致时序错误。

数据线(D0~D7):采用并行传输,需等长布线(误差<50mil),并预留上拉电阻(10KΩ)以增强信号驱动能力。

CMD 信号:需上拉至 VCCQ,确保空闲状态为高电平。

(二)关键设计要素

1.滤波与去耦电容布局

- 电源引脚附近放置多个不同容值电容(0.1uF~10uF),形成“金字塔”滤波结构,吸收不同频段噪声。

- VCC 与 VCCQ 通过 0Ω 电阻隔离,确保电平一致性。

- 电容尽量靠近芯片引脚,缩短走线长度,减少寄生电感。

- 采用 PMIC(电源管理芯片)为 eMMC 提供独立 3.3V 供电,减少系统电源干扰。

2.PCB 布线规则

- 分层设计:推荐使用 4 层及以上 PCB,信号层与地层相邻,降低信号辐射。

- 信号隔离:eMMC 信号与其他高速信号(如 USB、射频)保持间距(≥3W),数据线组间添加地线隔离,避免串扰。

- CLK 走线:采用蛇形走线补偿长度差异,确保与数据线同步到达。

- 热设计考虑:eMMC 芯片下方铺铜散热,通过过孔连接至地层,增强散热效率。

- 地平面分割:若存在多个电源域,需在分割区通过 0Ω 电阻或磁珠连接,确保信号回流路径最短。

3.ESD 与浪涌保护

- 信号线可添加 TVS 二极管或 ESD 保护芯片,防止静电或瞬态高压损坏接口。

- RST_N 信号线需串联限流电阻(如 1KΩ)并上拉,避免误触发复位。

三、eMMC 性能优化与调试

1.时序参数优化

- CLK 频率与数据建立/保持时间:根据 eMMC 规格调整 CLK 频率,确保数据在窗口期内稳定传输。

- 信号延迟匹配:通过仿真工具(如 HyperLynx)验证 CLK 与数据线延迟差,调整 PCB 布线长度。

2.功耗管理

- 利用 eMMC 的 Deep Power Down 模式(DPD)降低待机功耗,通过软件控制进入/退出 DPD 状态。

- 动态调整读写电压(如 1.8V→1.2V),平衡性能与功耗。

3.调试工具与测试方法

- 使用示波器抓取 CLK、数据波形,分析时序违规问题。

- 通过压力测试(如连续读写、高温老化)验证 eMMC 可靠性。