DDS compiler IP核配置与使用教程

DDS compiler IP核的功能

产生高精度、可编程的正弦/余弦波形.

DDS通过查找表(LUT)和相位累加器,能够在FPGA内部直接合成高精度的正弦波、余弦波等周期信号。输出的波形频率、相位、幅度都可以通过输入参数灵活控制。频率、相位、幅度可动态调节

可以实时改变输出信号的频率(通过频率控制字)、相位(通过相位偏移)、幅度(通过幅度控制字)。适合做频率扫描、跳频、调制等应用。典型应用场景

数字下变频(DDC)/上变频(DUC);软件无线电(SDR);通信系统中的本振信号(LO)产生;任意波形发生器;调制/解调器。

DDS compiler IP核工作原理

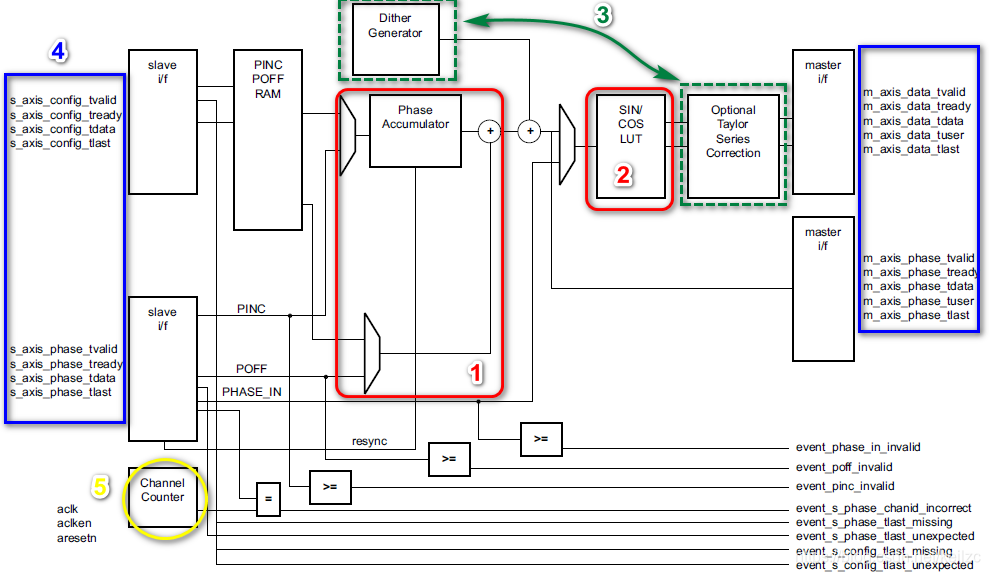

DDS compiler IP核port

- s_axis_phase_tdata: AXI-Stream接口上的相位输入;

①DDS Compiler有两种可以输入PHASE(相位)的配置方式,但这两种方式不能同时启用(互斥)。

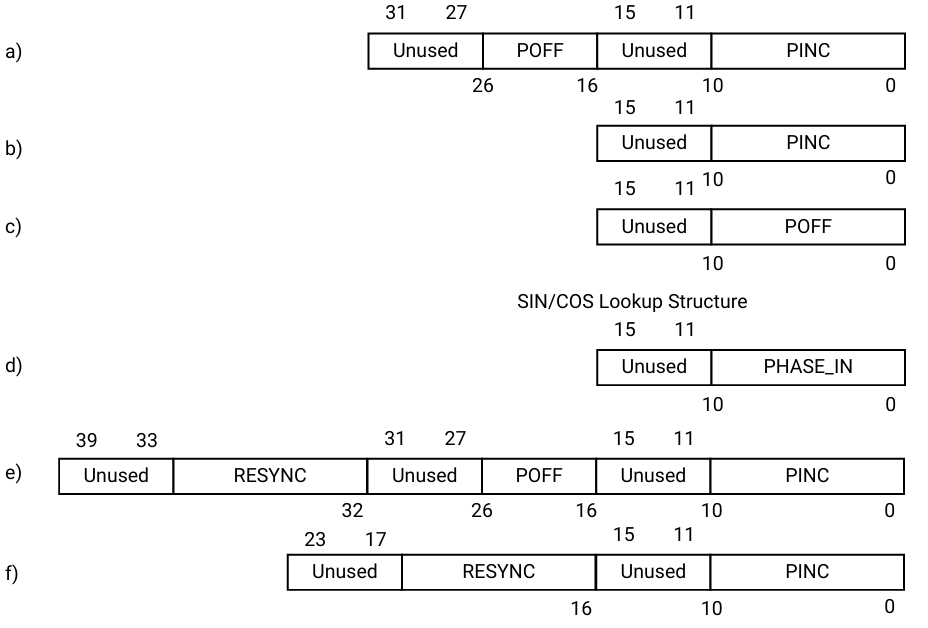

②TDATA总线最多有四个字段(PINC、POFF、PHASE_IN、AMP),但这四个字段不可能同时全部出现。

③当DDS配置为SIN/COS LUT only模式时,PHASE_IN字段会映射到 s_axis_phase_tdata 这个输入端口。

④你可以通过 s_axis_phase_tdata 端口直接输入相位数据,DDS会用这个相位去查LUT,输出对应的正弦/余弦值。

⑤HASE_IN字段在总线的最低有效位(LSB)部分,占用的位宽是8的整数倍(即1字节、2字节、3字节……)。

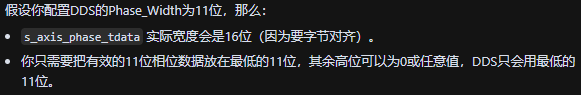

⑥如果你的PHASE_IN不是8的整数倍,比如说11位,那么s_axis_phase_tdata会自动扩展到16位(2字节),多出来的高位会被忽略,不影响功能,综合时会被优化掉。

⑦管是PINC、POFF都设置为Streaming,还是只有PINC或POFF为Streaming,或者是SIN/COS LUT only模式,只要Phase_Width=11,s_axis_phase_tdata的宽度就是16位,最低11位为有效相位数据,高5位无效。

实际应用举例:

s_axis_phase_tdata数据结构

DDS compiler IP核基础概念

DDS的原理并不复杂,但其中涉及一些正弦波的基础概念的理解。下面对这些概念进行梳理。

一个通用的正弦波函数如下所示:

f ( t ) = s i n ( θ ) = s i n ( ω ⋅ t + φ ) = s i n ( 2 π f ⋅ t + φ ) f(t)=sin(θ)=sin(ω⋅t+φ)=sin(2πf⋅t+φ) f(t)=sin(θ)=sin(ω