0 引 言

近年来,随着海洋工程技术的发展,水下无人

航行器 (underwater unmanned vehicle, UUV)) 因其

灵活性、低风险性以及多功能性的优点,在维护国

家海洋权益以及海洋安全发挥着日益重要的作用 [1-3] 。

UUV 在完成目标搜索、跟踪、参数估计以及机动

等一系列任务时,一般需要主动声呐系统提供目标

准确的距离、方位与速度等参数 [4-5] ,因此在

UUV 研制过程中,需要经过水池测试以及实航测

试来对主动声呐系统进行调试,以保证其性能的可

靠性。主动声呐系统一般采用裸机或者实时操作系

统,无法方便地对主动声呐采集的数据以及信号处

理结果进行直观的绘图查看和分析处理。对于

UUV 主动声呐系统的测试,一般需要在不破坏水

密结构的情况下完成其程序更新,而传统的联合测

试工作组 (joint test action group, JTAG) 接口更新方

式需要对设备开盖,且接线复杂,因而不再适用 [6-7] 。

因此,研制适配于 UUV 主动声呐工作要求的数据

采集系统,将采集数据完整、准确地存储并传输到

上位机,并开发适应 UUV 特殊工作环境的在线更

新系统,对主动声呐系统当前的运行状态进行准确

评估,以及后期对主动声呐的性能优化和改良,加

速设备调试进程,降低开发成本,具有非常重要的

意义。

目前对于声呐数据采集系统的研制,一般选择

微处理器或微控制器、现场可编程门阵列 (field

programmable gate array, FPGA) 或者是数字信号处

理器 (digital signal processing, DSP) 等芯片作为主

控芯片。王敏等 [8] 采用 DSP 运行 Vxworks 操作系

统实现传输控制协议 (transmission control protocol/

internet protocol, TCP/IP) 网络协议栈,可以实时将

声呐系统采集的数据以及计算结果回传到计算机。

张严品 [9] 基于 OMAP-L138 芯片设计的水声信号采

集与处理平台,实现了对水声信号的连续采集、处

理、存储和传输等功能,通过 LwIP 协议栈实现安

全数字卡中存储水声数据的上传功能。荣致远 [10] 结

合 FPGA 的高速并行处理能力以及 ARM 灵活的进

程控制能力,设计了一种基于 FPGA+ARM 的声呐

数据采集传输系统,满足采集系统高精度和实时性

的要求。荆博原等 [11] 采用 Artix-7 系列 FPGA 芯片

控制数据的采集与存储来完成多通道数据采集,通

过通用串行总线 2.0 接口将矢量水听器数据传输至

上位机。史鹏腾 [12] 使用以太网知识产权 (intellectual

property, IP) 核实现用户数据报协议来进行多通道

声呐采集数据的高速传输,并在应用层制定了与上

位机交互及丢包处理的通信协议,克服了用户数据

报协议这类不可靠的、面向无连接的协议带来的数

据错误和缺失等问题。

在上述文献中,对声呐数据采集系统的设计主

要集中于使用 DSP 或 FPGA 等单一架构芯片,无

法兼顾利用微处理器以及 DSP 等串行处理器可方

便实现网络协议栈等复杂控制逻辑,以及 FPGA

具有的强大并行处理的优势。但使用 DSP+FPGA

架构也存在一系列问题 [13-14] :首先是布线工作相对

比较复杂,需要完成更多的硬件设计工作。其次,

集成度较低,占用面积较大,成本较高。在能耗和

散热方面,这种方案在计算密集任务下会产生较高

的能耗,需要更好的散热以及供电解决方案。目

前,声呐数据采集系统的设计中鲜见水密条件下的

在线程序更新功能,以及使用 TCP 传输协议进行

数据传输时对数据封帧的考虑。

针对 UUV 前置主动声呐小型化、高集成、低

功耗设计,以及水下封闭空间工作条件下程序更新

的需求,本文选择 Xilinx 推出的 Zynq7020 芯片构

建主动声呐数据采集平台,该芯片采用先进的双核

异构架构 [15-17] ,将可编程逻辑单元 (programmable

logic, PL) 和处理系统单元 (processing system, PS)

集成到一个芯片内,兼顾了 FPGA 的并行计算优

势以及处理器系统软件开发的灵活性,克服了传统

双芯片架构中片间互联通信带宽和处理速度瓶颈限

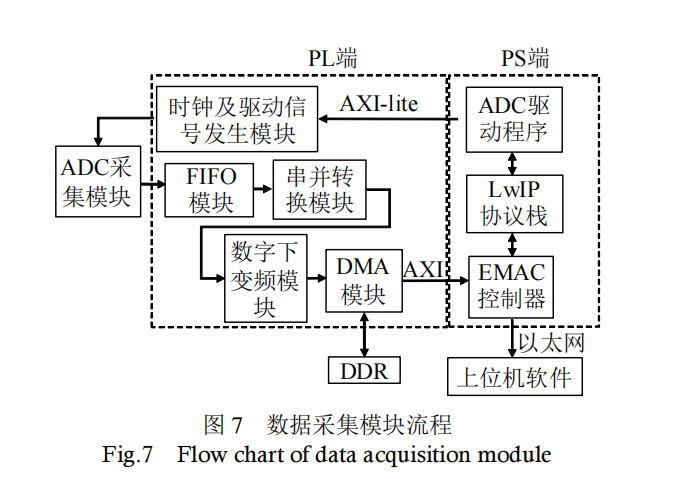

制,集成度高,功耗低。在 PL 端完成数据采集控

制与数字下变频等信号预处理任务,以满足系统实

时性要求。并配合开发的上位机软件,在 PS 端的

ARM 处理器上运行 LwIP 网络协议栈实时处理

TCP 数据流,从而可以充分发挥 Zynq7020 异构架

构优势。对于采集数据传输方案的选择,考虑实时

传输速度、带宽与可靠性要求,系统采用以太网实

现主动声呐与上位机软件的数据交互,同时为保证

数据传输的可靠性,本系统采用 TCP/IP 协议作为

数据传输协议,并结合自定义的应用层帧协议,通

过以太网建立下位机与上位机的连接 [18] 。对于数据

存储介质的选择,选用了容量大、读写速度快的嵌

入式多媒体卡 (embeded multimedia card, eMMC) [19-20]

芯片,确保数据记录的完整性和可靠性。对于

FPGA 程序更新方式的选择,使用 TCP 以太网实

现程序的在线更新,并开发对应的上位机软件,可

以在保证 UUV 水密结构完整的同时避免复杂的接

线操作,方便可控地实现系统 FPGA 程序的更新。

1 系统硬件设计

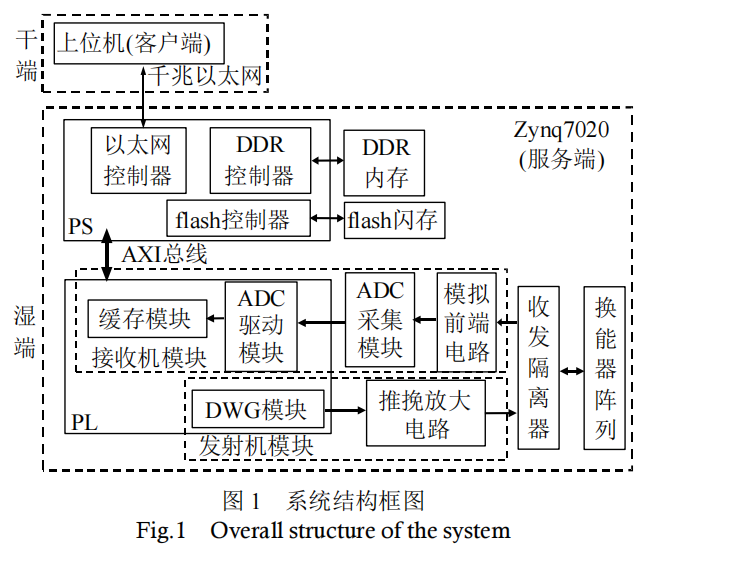

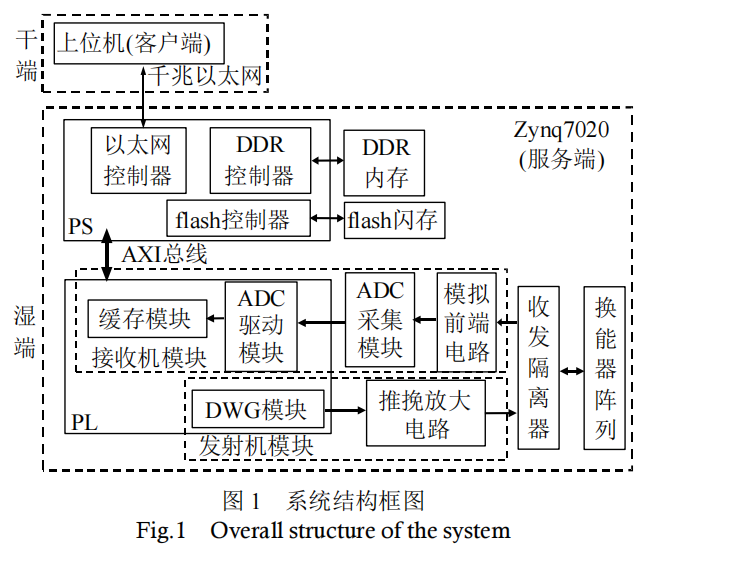

本文系统主要由位于电脑 (PC) 端的上位机软

件以及位于 UUV 内部 ( 湿端 ) 的主动声呐发射、接

收电路组成,系统的总体结构如图 1 所示。

系统采用模块化设计方法,由以下部分组成:

(1) 发射机模块,由数字波形发生模块 (digital

waveform generator, DWG)、推挽放大电路和收发

隔离板组成,其中 DWG 模块位于 Zynq7020 的

PL 端,由 PS 端负责配置,用于产生发射波形信

号;推挽放大电路用于放大发射信号,使其能够驱

动发射换能器阵列;收发隔离板用于声呐发射与接

收信号的切换,避免发射信号时高电压信号直接窜

入数据采集模块从而损坏模数转换芯片。 (2) 接收

机模块,主要由 Zynq7020 核心板、模拟前端电路

与模数转换器 (analog-to-digital converter, ADC) 模

块组成。当声呐处于接收模式时, Zynq7020 控制

收发隔离板使阵元接入到模拟前端电路,然后通

过 ADC 数据采集模块,以 200 kHz 的采样率,对

64 路输入模拟信号进行采样,随后通过位于 PL 端

的 ADC 驱动模块输入到核心板上进行存储和传

输。 (3) 位于干端的上位机模块,上位机通过以太

网与位于湿端的主动声呐设备进行通信,下发控制

指令将采集的数据通过以太网上传至上位机进行保

存,同时可以将更新镜像传输给下位机,控制其进

行程序更新。

2 网口通信协议实现

2.1 LwIP 网口通信协议简介

LwIP 是一种开源的轻量化网络通信协议栈,

可以为嵌入式设备提供高效的 TCP/IP 协议栈,具

有占用资源少、易于移植、可裁剪性高等特点,广

泛应用于嵌入式系统中 [21] 。 LwIP 提供了两套应用

编程接口 (application programming interface, API) :

基于回调函数的内部回调接口 (API) 和套接字应用

程序接口 (Socket API) 。其中 RAW API 可以在没

有操作系统支持的裸机环境中运行,而且传输效率

相较于 Socket API 更加高效,因此本文设计采用

LwIP 的 RAW API 模式实现网络通信协议。

基于软硬件协同开发的思想,为充分发挥

Zynq7020 异构架构的优势,本文系统设计在 Zynq

PS 端运行 LwIP 网络协议栈作为 Zynq7020 与上位

机通信的协议,并利用 PS 端集成的硬核以太网媒

体访问控制器,在高效实现 TCP 协议的同时,可

以有效减少对可编程逻辑资源的占用。考虑到上位

机与主动声呐控制指令的交互,声呐采集数据的回

传以及 FPGA 更新镜像数据传输的需求,对数据

完整性、准确性要求较高,必须确保无丢帧、误码

等异常发生,因此选用具有高可靠性的 TCP/IP 协

议作为以太网传输协议。 TCP 协议是一种面向连

接的、基于字节流的传输层通信协议,通过三次握

手建立客户端以及服务端的连接,可以保证数据传

输的可靠性 [22] 。系统设计采用 TCP/IP 传输数据,

上位机作为客户端,下位机 (Zynq7020) 作为服务

器处于监听状态,当上位机发起连接请求时,下位

机与上位机建立起连接进行数据交互来完成一系列

任务。

2.2 TCP/IP 自定义帧格式设计

在本系统中,上位机与主动声呐设备的交互存

在以下几种数据类型: (1) 按照通道顺序进行排列

的 ADC 采集数据; (2) 程序更新上位机发送给

Zynq 的更新镜像文件; (3) 上位机与主动声呐下位

机交互指令等数据。因此需要合理设计数据帧结

构,使其能够满足上位机与主动声呐之间通过

TCP 进行数据交互的需求。 TCP/IP 协议是位于传

输层的一种基于字节流的传输协议,如图 2 所示,

尽管在应用层上用户的数据是按照确定的边界进行

收发的,但是在物理层上用户数据被分成若干个数

据包并通过二进制字节流形式进行传输,各个消息

之间没有明显的边界。