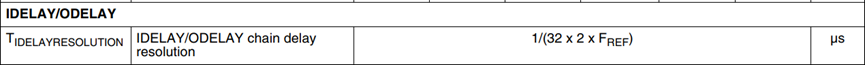

7系列可编程输出延迟原语ODELAYE2,仅在HP bank有该原语,原语可以连接到OLOGICE2/OSERDESE2块。与IDELAYE2相同,是一个32抽头(0~31),环绕式原语,抽头分辨率有校准功能,

延迟值延迟精度与同系的输入延迟相同,

IDELAYCTRL使用200M参考时钟tap精度78ps,使用300M参考时钟tap精度52ps;

原语可以用于组合输出路径或寄存器输出路径,可以从FPGA逻辑直接访问,也可以对输出信号进行单独延迟;

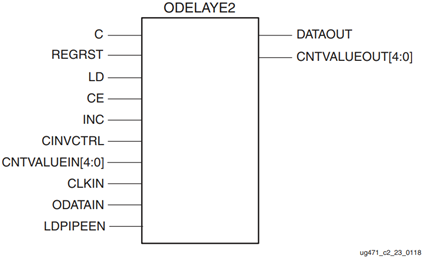

ODELAYE2原语介绍:

框图:

例化模板:

ODELAYE2 #(

.CINVCTRL_SEL(“FALSE”), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC(“ODATAIN”), // Delay input (ODATAIN, CLKIN)

.HIGH_PERFORMANCE_MODE(“FALSE”), // Reduced jitter (“TRUE”), Reduced power (“FALSE”)

.ODELAY_TYPE(“FIXED”), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.ODELAY_VALUE(0), // Output delay tap setting (0-31)

.PIPE_SEL(“FALSE”), // Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0).

.SIGNAL_PATTERN(“DATA”) // DATA, CLOCK input signal

)

ODELAYE2_inst (

.CNTVALUEOUT(CNTVALUEOUT), // 5-bit output: Counter value output

.DATAOUT(DATAOUT), // 1-bit output: Delayed data/clock output

.C©, // 1-bit input: Clock input

.CE(CE), // 1-bit input: Active high enable increment/decrement input

.CINVCTRL(CINVCTRL), // 1-bit input: Dynamic clock inversion input

.CLKIN(CLKIN), // 1-bit input: Clock delay input

.CNTVALUEIN(CNTVALUEIN), // 5-bit input: Counter value input

.INC(INC), // 1-bit input: Increment / Decrement tap delay input

.LD(LD), // 1-bit input: Loads ODELAY_VALUE tap delay in VARIABLE mode, in VAR_LOAD or

// VAR_LOAD_PIPE mode, loads the value of CNTVALUEIN

.LDPIPEEN(LDPIPEEN), // 1-bit input: Enables the pipeline register to load data

.ODATAIN(ODATAIN), // 1-bit input: Output delay data input

.REGRST(REGRST) // 1-bit input: Active-high reset tap-delay input

);

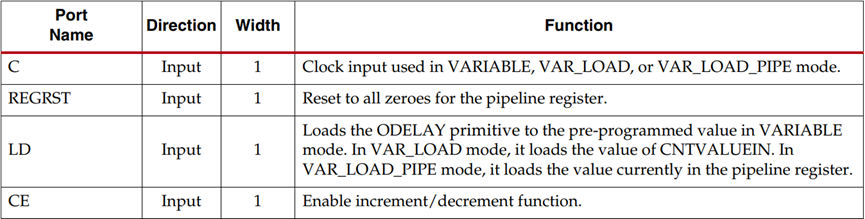

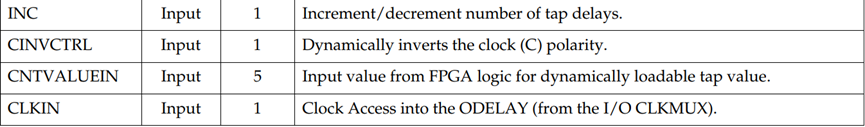

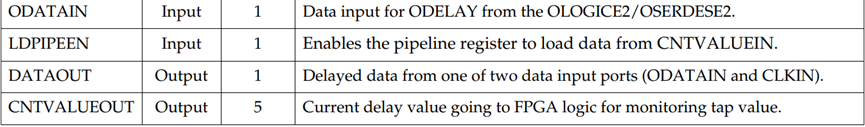

端口:

C:原语所有控制信号使用的时钟输入,LD/INC/CE等控制信号与之同步;该时钟需要连接到

SelectIO逻辑资源使用的相同时钟;例如,使用并转串的OSERDESE2时,C与CLKDIV使

用同一个时钟,如果IDELAYE2和ODELAYE2两个在同一个IO bank上被使用,那么两个

原语的控制输入时钟C需为同一个时钟;

REGRST:流水线寄存器复位,该端口置1将流水线寄存器重置为0;

LD:VARIABLE模式下,置1加载DELAY_VALUE延时值,VAR_LOAD模式下,置1加载CNTVALUEIN

的抽头值,VAR_LOAD_PIPE模式下,置1加载流水线寄存器中的抽头值,与IDELAYE2的

对应端口功能相同;

CE、INC:可变延时模式下联合起来使用,CE=1&INC=0抽头递减,CE=1&INC=1抽头递增;

CINVCTRL:置1将反转C端口时钟极性;

CNTVALUEIN:动态加载抽头值模式下的抽头值输入总线;

CLKIN:要延迟的时钟输入,必须来自时钟缓冲器(如BUFG、BUFO、BUFR),由DELAY_SRC

参数决定是否延迟时钟,延迟后通过DATAOUT端口输出;

ODATAIN:要延时的数据输入,数据输入由OLOGICE2/OSERDESE2驱动,延迟后由DATAOUT

端口输出,DATAOUT端口连接到IOB;

LDPIPEEN:将CNTVALUEIN值加载到流水线寄存器的使能;

DATAOUT:来自两个数据输入端口之一的延迟数据,连接到IOB;

CNTVALUEOUT:报告正在使用的延迟抽头值;

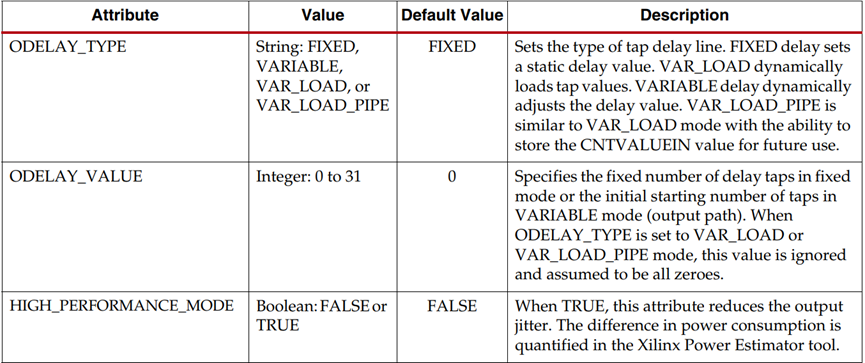

参数:

ODELAY_TYPE:共4种模式,工作模式与IDELAYE2的4种模式基本相同,

ODELAY_VALUE:抽头延迟,范围0-31;

HIGH_PERFORMANCE_MODE:高性能模式,开启后抖动降低但功耗略微增加;

SIGNAL_PATTERN:输入信号的类型,时钟或数据,该参数会根据信号类型做对应优化;

REFCLK_FREQUENCY:参考时钟频率,范围在200,300,400MHz上下波动10;

CINVCTRL_SEL:时钟极性反转选择,该参数设置为true后将CINVCTRL端口置1才可以反转

时钟端口C的极性;

PIPE_SEL:流水线选择,只在VAR_LOAD_PIPE模式下设置为true;

DELAY_SRC:延时源选择,选择CLKIN和ODATAIN分别对应选择延迟时钟或数据信号;

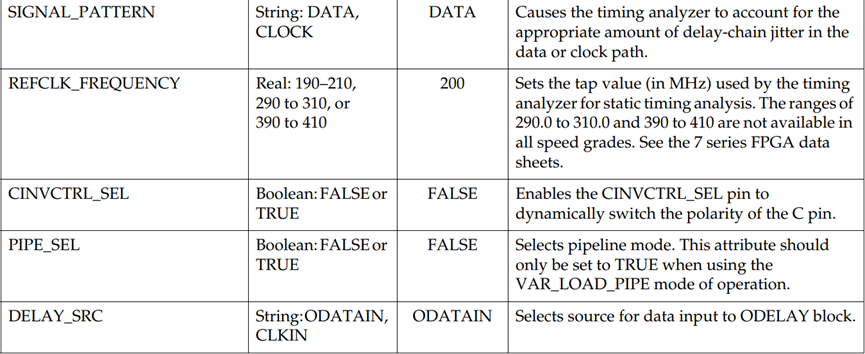

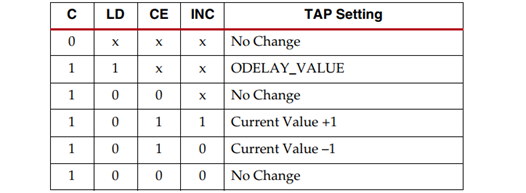

ODELAYE2模式:

ODELAYE2共4种操作模式,与IDELAYE2对应,使用时必须例化IDELAYCTRL,因为保持tap精度需要校准补偿等操作;

FIXED模式:

固定延迟模式(ODELAY_TYPE =FIXED),延迟值在配置时预设为由属性ODELAY_VALUE确定的抽头数。

一旦配置完成,该值将无法更改;

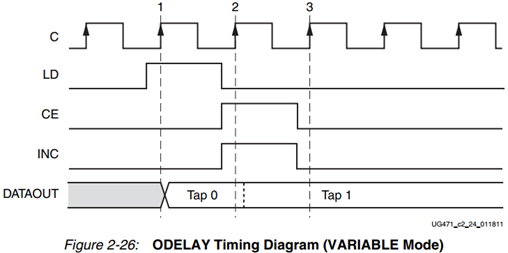

VARIABLE模式:

可变延迟模式(ODELAY_TYPE = VARIABLE)

在可变延迟模式下,延迟值可以通过操作控制信号CE和INC在配置后进行更改。

CE=1&INC=0递减一个抽头,CE=1&INC=1递增一个抽头,CE=0时不生效;

在该模式下拉高LD端口,将会把ODELAY_VALUE的值加载为正在使用的抽头值;

可以看到时序LD拉高加载默认为0的ODELAY_VALUE值tap0,INC=1&CE=1就将抽头值递增为tap1;

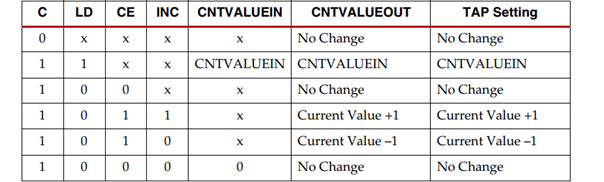

VAR_LOAD模式:

动态加载延迟模式(ODELAY_TYPE = VAR_LOAD),除了可以使用INC&CE修改延迟,还可以使用CNTVALUEIN输入新抽头值,拉高LD直接将CNTVALUEIN值作为新抽头值使用。

从时序可以看到INC和CE起作用,LD拉高加载CNTVALUEIN总线的值;

VAR_LOAD_PIPE模式:

动态流水线加载延迟模式(ODELAY_TYPE = VAR_LOAD_PIPE),VAR_LOAD模式添加流水线的版本,除了可以使用INC&CE修改延迟,拉高LDPIPEEN先将CNTVALUEIN线上的值存入原语内部寄存器,后续将LD拉高,才会将流水线寄存器中的值作为新抽头值使用;

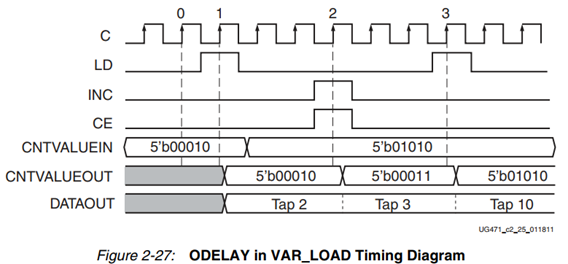

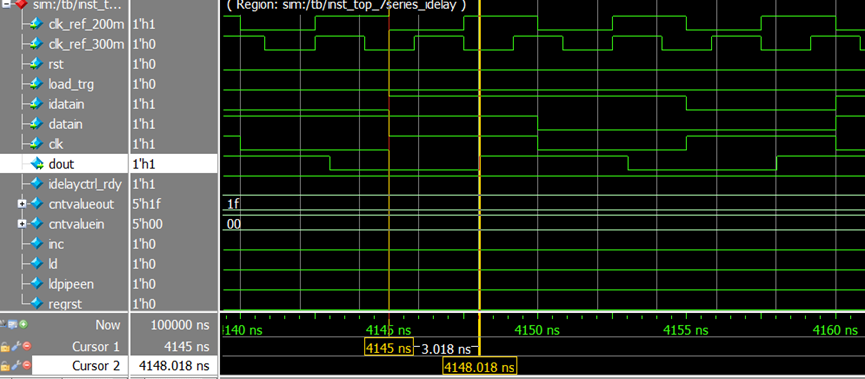

由于ODELAYE2的端口乃至操作逻辑与IDELAYE2基本一致,这里只简单仿真下FIXED模式下对CLKIN的延时,在200M参考时钟情况下:

FIXED模式下延时CLKIN 0抽头值,可以看到还是跟IDELAYE2一样的固定600ps固有延时:

FIXED模式下延时CLKIN 31抽头值,延时3.018ns=600ps + 78ps*31,也与IDELAYE2一致;

可以看到IDELAYE2和ODELAYE2的延时逻辑基本一致,但两者在支持的I/O bank类型,信号路径和应用场景等还是有区别;

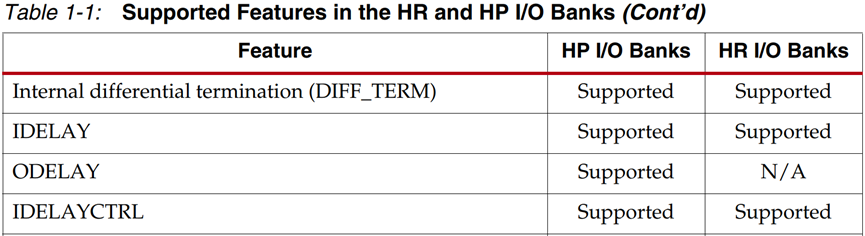

支持的I/O bank类型:

7系列提供了两种I/O bank,分别是高性能HP bank,高范围HR bank,HP bank主要用于高速存储器或是芯片间高速互联,bank电压最高1.8V,HR bank主要用于支持更大范围的IO标准,电压最高3.3V

从下图可以看到,IDELAY在HP bank和HR bank都受支持,ODELAY在HP bank支持,HR bank不支持;

信号路径:

IDELAYE2用于输入路径,调整外部引脚进入FPGA内部的延迟,可以从IOB也就是FPGA外

部接收信号,延迟后输出到FPGA内部逻辑;

ODELAYE2用于输出路径,调整FPGA逻辑到外部引脚的信号延迟或是时序,可以从FPGA内

部逻辑接收信号,延迟后输出到IOB也就是FPGA外部;

输入源:

IDELAYE2输入源可以是来自IOB的IDATAIN或是来自FPGA内部逻辑的DATAIN;

ODELAYE2输入源可以是来自FPGA内部逻辑的ODATAIN或是来自FPGA内部时钟缓冲器驱

动的时钟信号CLKIN;

应用场景:

IDELAYE2常用于源同步的时序校准,如常见的ADC的LVDS接口的数据和时钟的对齐;

ODELAYE2常用于输出信号的多线同步或是调整输出线的时序调整;

本文章由威三学社出品

对课程感兴趣可以私信联系