🔥 创作专栏:《史上最强算法分析》 | 《无味生》 |《史上最强C语言讲解》 | 《史上最强C练习解析》|《史上最强C++讲解》|《史上最强计组》|《史上最强数据结构》

🏆我的格言:一切只是时间问题。

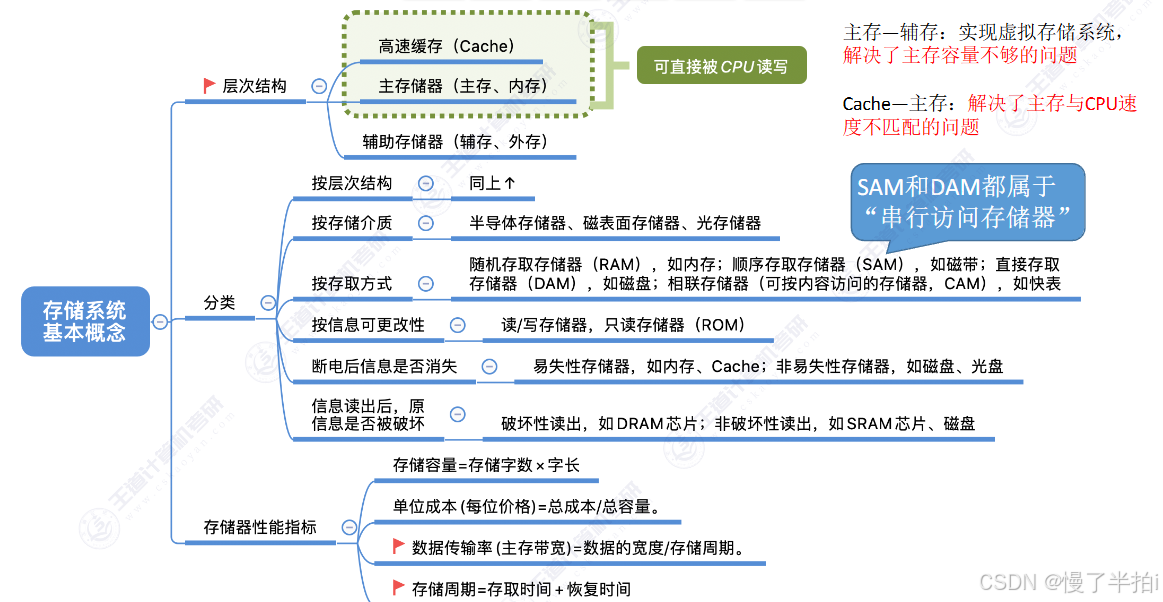

一、存储器概念

1.1 存储器的分类

可按照不同分类方式进行分类

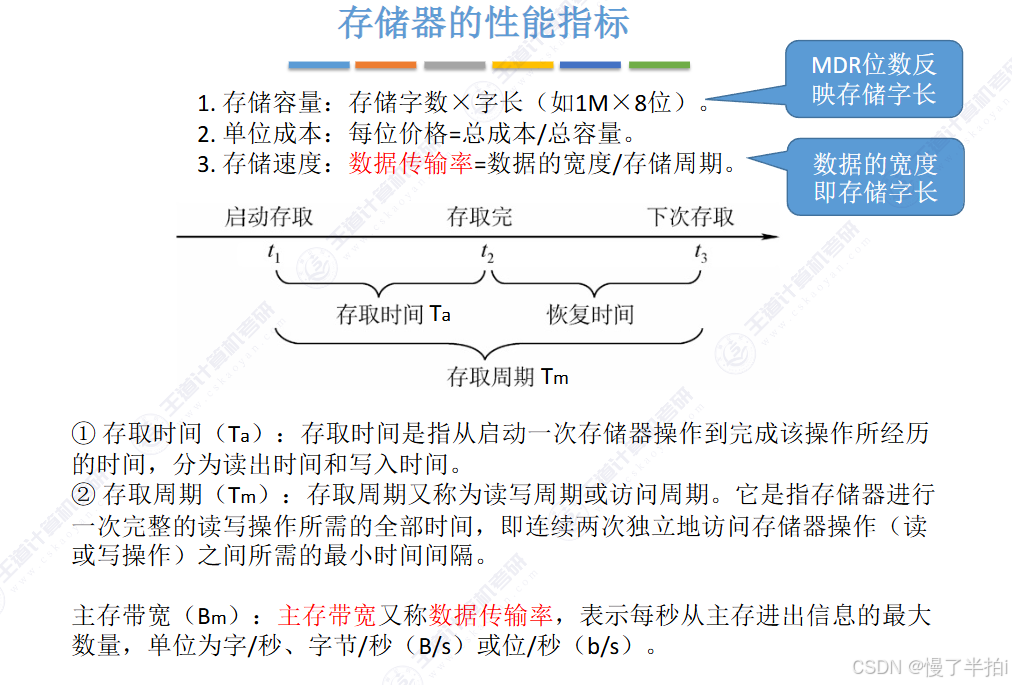

1.2 存储器的性能指标

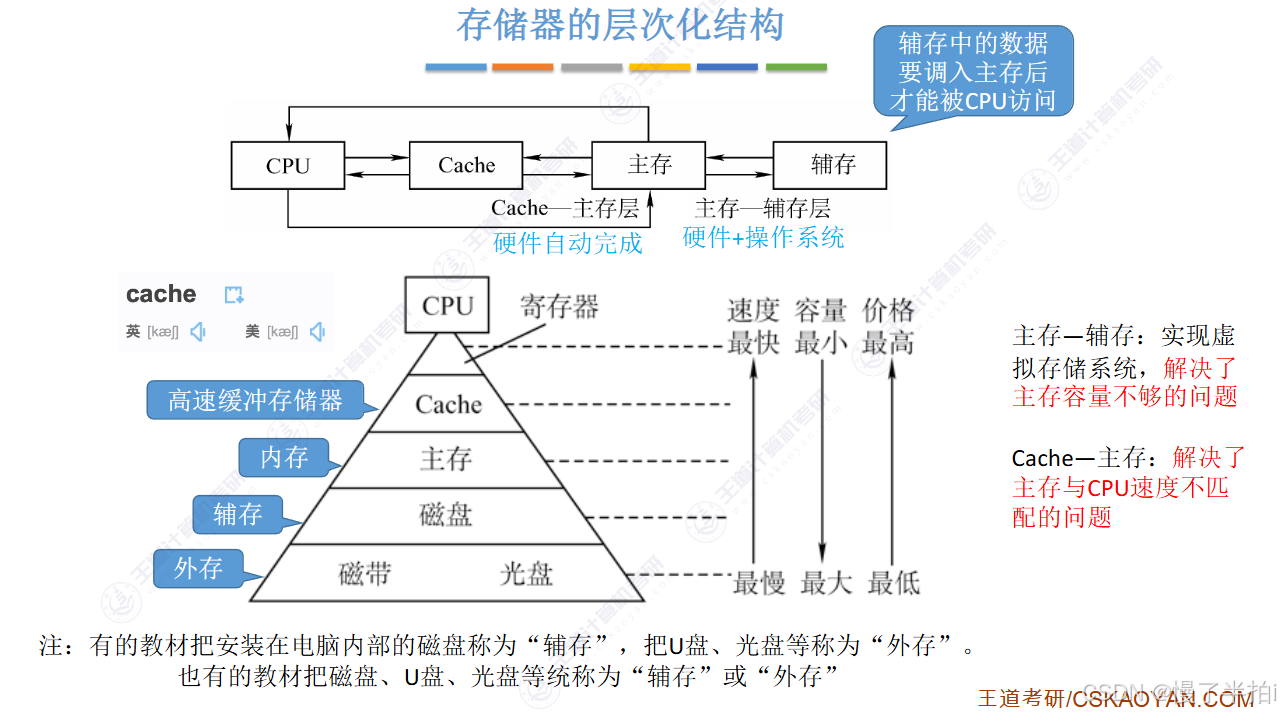

1.3 多级层次的存储系统

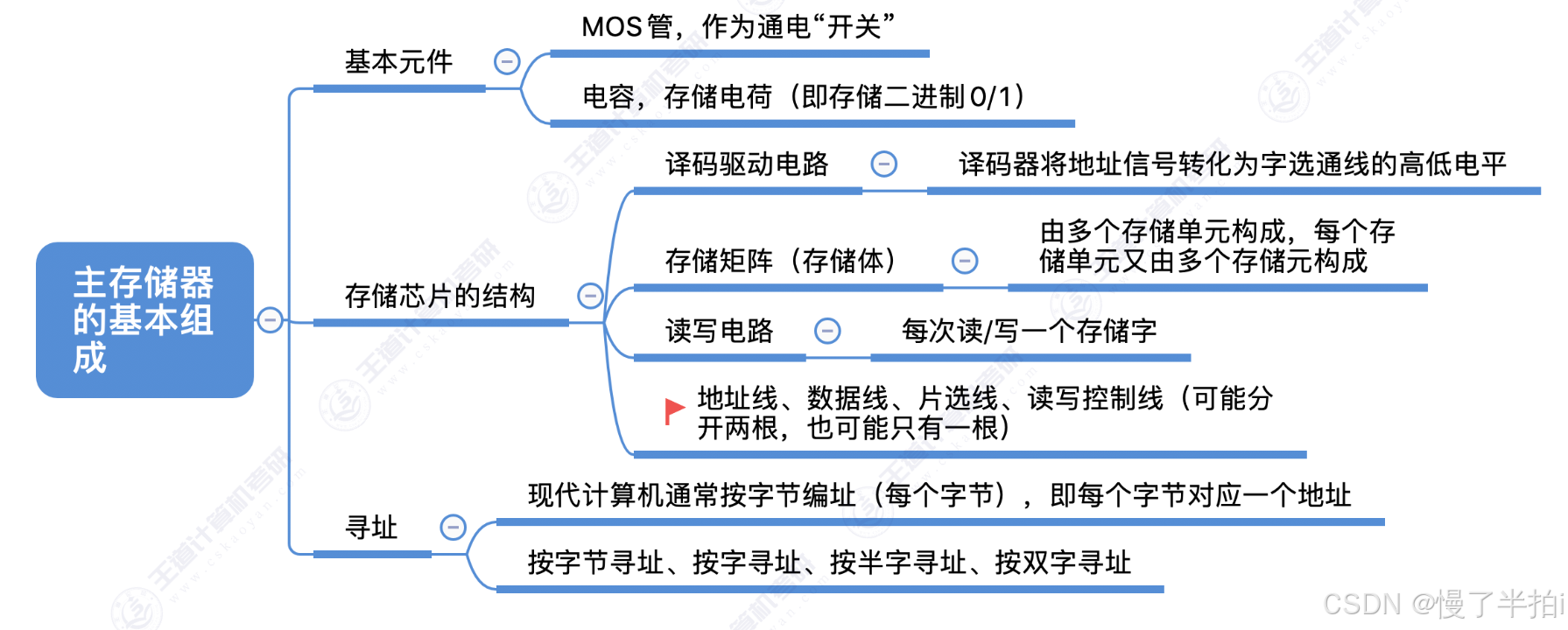

二、主存储器

2.1 主存储器的基本组成

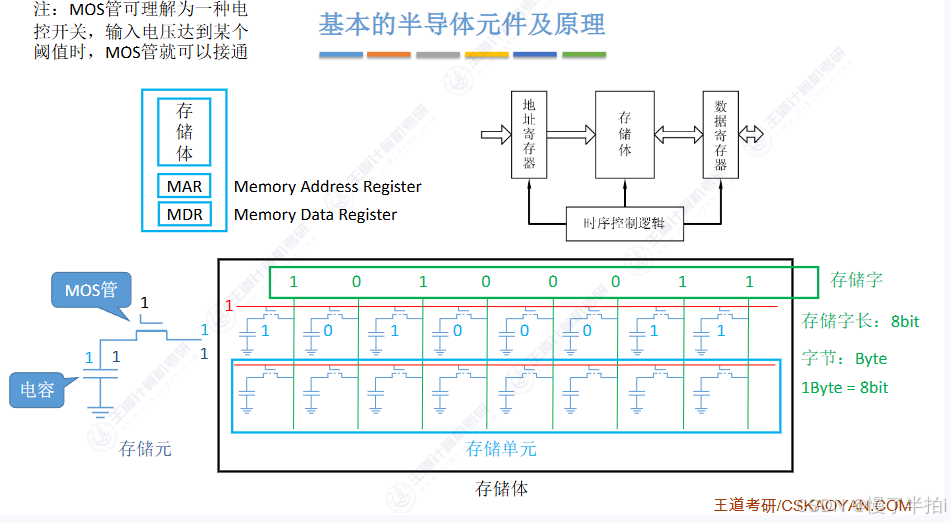

1.半导体基本原理

1)存储体的构成

- 三大部分: 主存储器逻辑上可分为存储体、MAR(地址寄存器)和MDR(数据寄存器)三大部分

- 层级关系: 存储体由多个存储单元构成,每个存储单元又由多个存储元(存储元件)构成

- 最小单位: 一个存储元件可存放一位二进制数据(0或1)

2)半导体元件介绍:MOS管

- 工作原理: 用电控制的开关,当控制端电压达到阈值(如5V)时导通,否则绝缘

- 半导体特性: 既不是导体也不是绝缘体,电压条件满足时变为导体

- 图示说明: 控制端加高电平画实线表示导通,低电平画虚线表示绝缘

3)半导体元件介绍:电容

- 结构组成: 由两块金属板和中间绝缘体构成,下板接地(0V)

- 充电原理: 上板加高电平(如5V)时产生电压差,电荷移动形成充电

- 数据表示: 充电状态表示二进制1,未充电表示二进制0

4)二进制数据的读取原理

- 读取过程:

- 给MOS管控制端加高电平使其导通

- 若电容有电荷(表示1),电荷流出产生可检测电流

- 若电容无电荷(表示0),无电流输出

检测方式: 通过监测输出线是否有电流判断存储的是0还是1

5)二进制数据的写入原理

- 写入1:

- 数据线加高电平(5V)

- MOS管控制端加高电平使其导通

- 电容上板电压5V,下板0V,产生充电

- MOS管断开后电荷保留

- 写入0: 数据线加低电平(0V或1V),电压差不足不充电

6)存储单元与存储体的概念

- 存储单元: 一行连接的存储元件构成一个存储单元(存储字)

- 存储体: 多个存储单元构成存储体(存储矩阵)

- 字长说明: 存储字长取决于每行存储元件数量(如8个存储元件=8位字长)

- 重要区别: 字节固定8位,存储字长由具体存储体结构决定

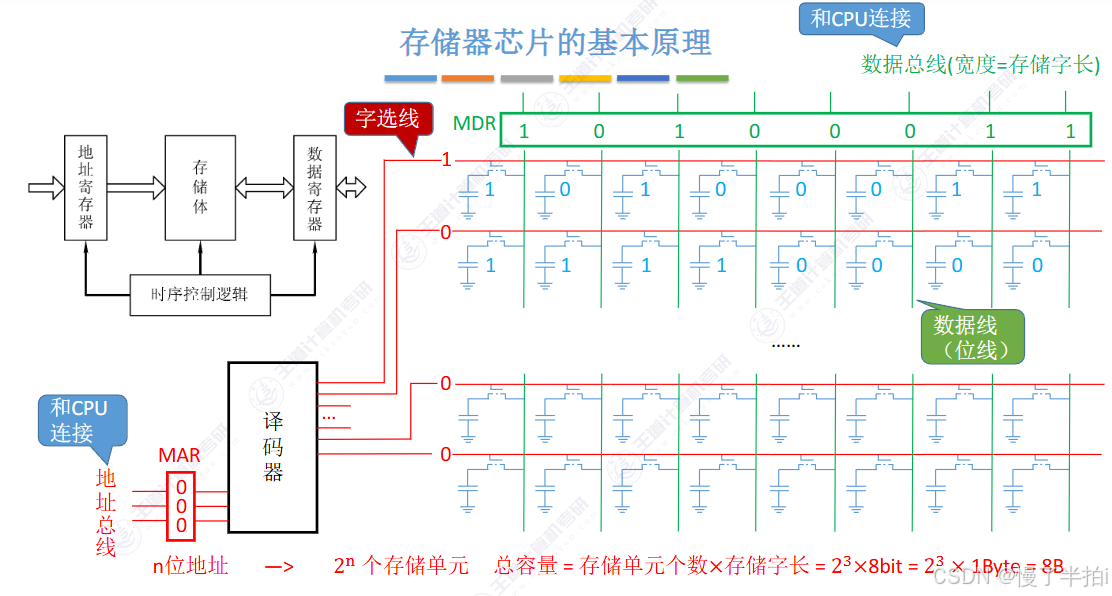

2.存储芯片的基本原理

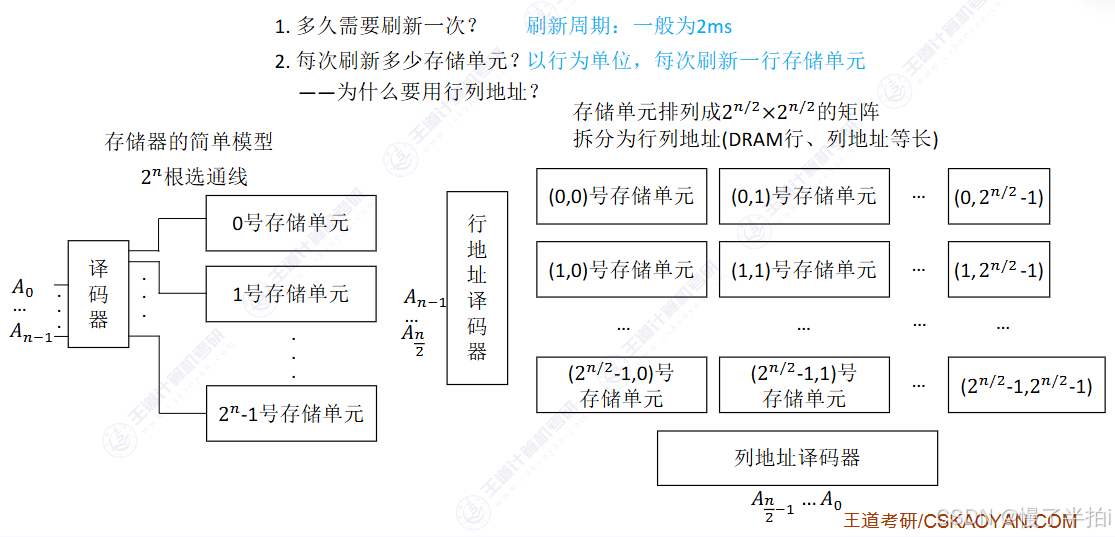

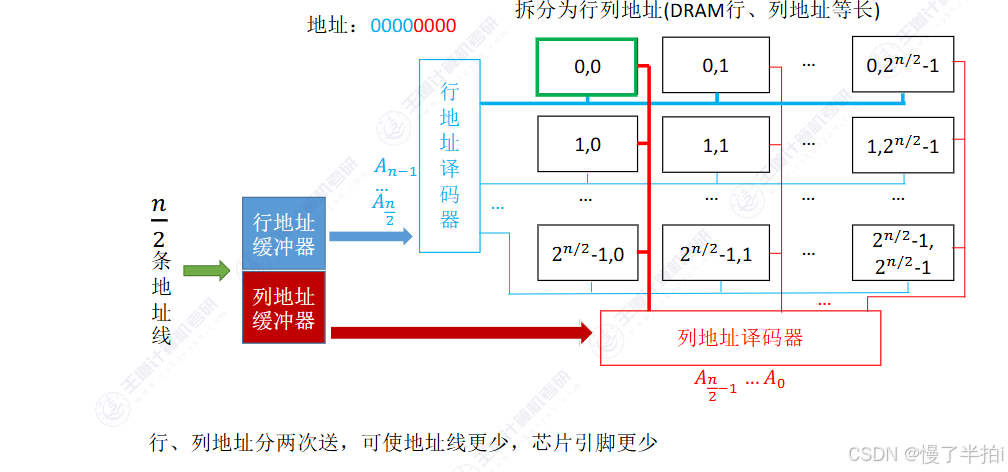

- 地址译码: n位地址对应 2^n 个存储单元,译码器将地址转换为某条选通线的高电平

- 读取过程示例: 地址000对应第0根选择线,选中第一个存储字的所有存储元件

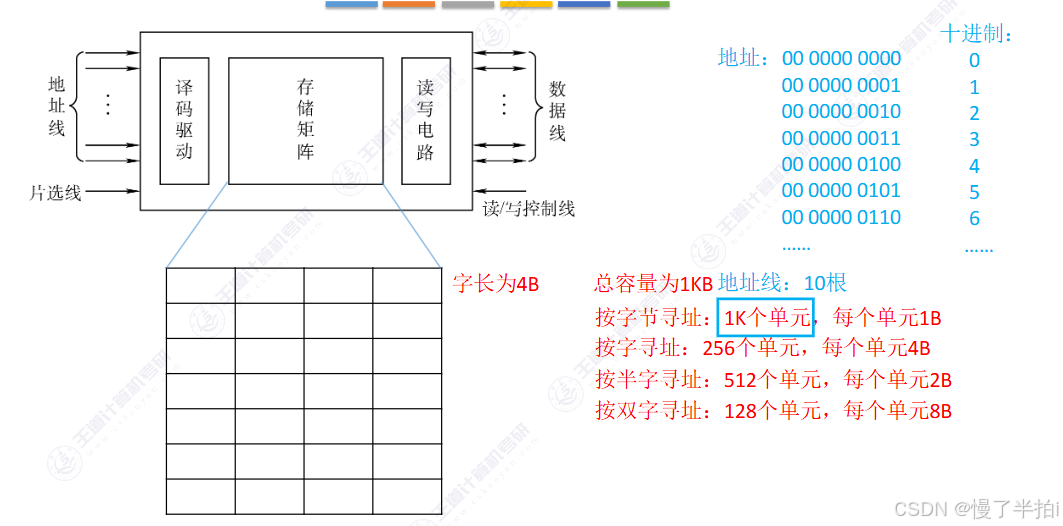

1)存储芯片的逻辑构成

- 核心部件:

- 存储矩阵(存储体)

- 译码驱动电路(含译码器和驱动器)

- 读写电路(含控制电路)

- 外部接口:

- 地址线(接收CPU地址)

- 数据线(传输数据)

- 片选线(确定芯片是否可用)

- 读写控制线(控制读写操作)

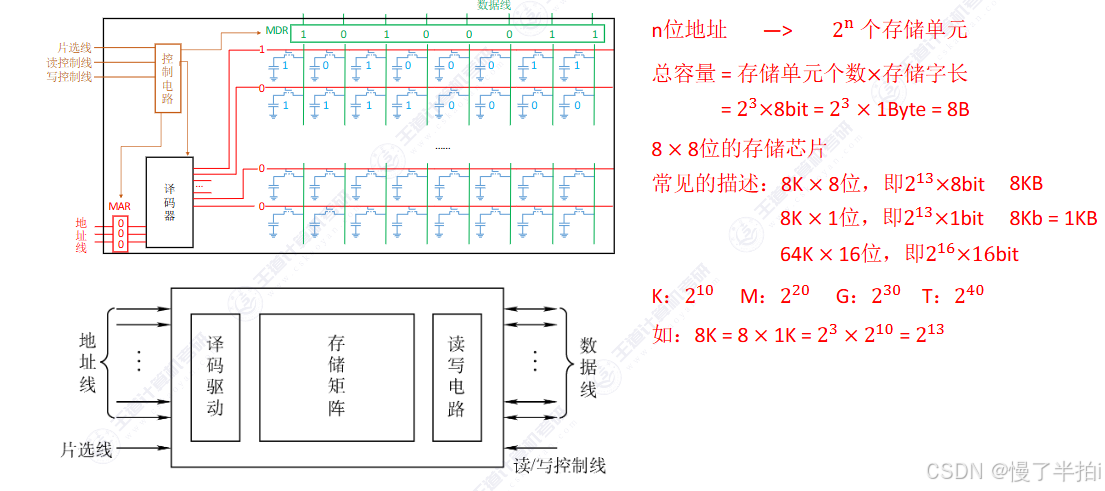

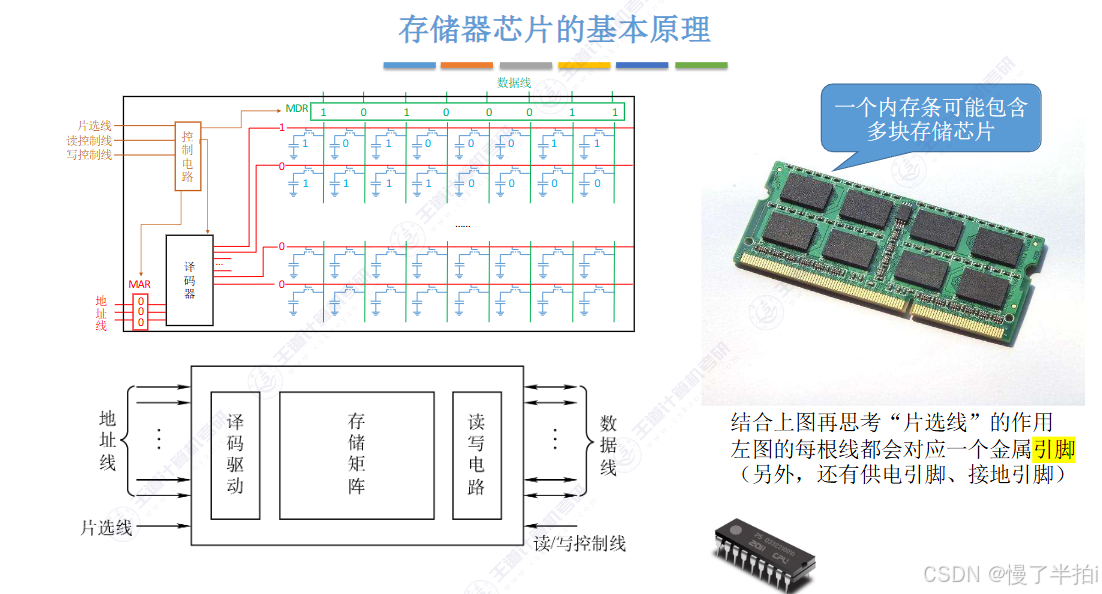

2)存储芯片的物理构成

- 片选信号作用: 在多芯片系统中选择特定芯片工作(低电平有效)

- 引脚计算:

- 地址线数量=地址位数

- 数据线数量=存储字长位数

- 必选引脚: 片选线+读写控制线(1或2根)

- 容量表示: 采用"存储单元数×存储字长"格式(如8K×8位表示8K单元,每单元8位)

- 实际应用: 内存条由多块存储芯片组成,总容量为各芯片容量之和

3.如何实现不同的寻址方式

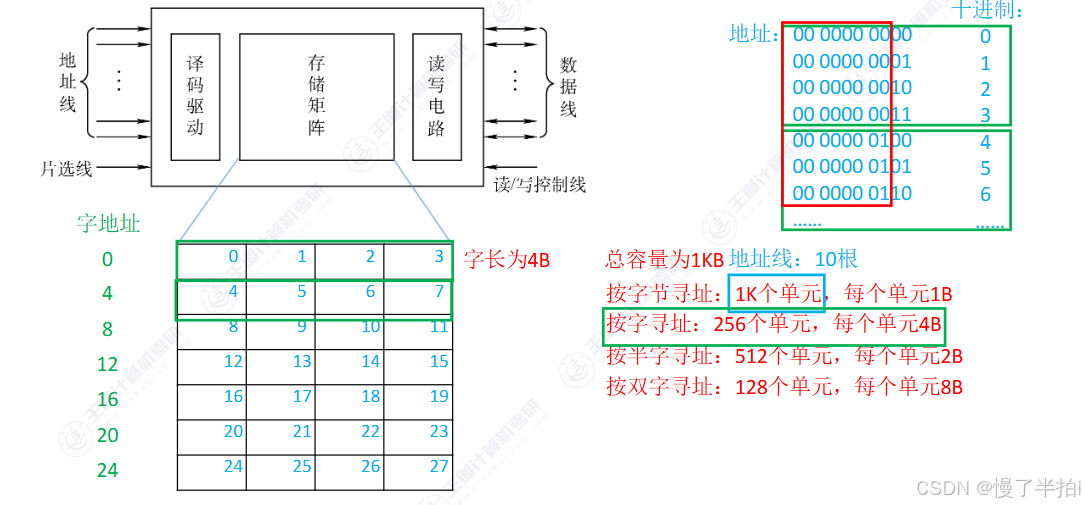

1)存储芯片的基本结构

- 核心组件:由地址线、译码驱动电路、存储矩阵、读写电路、数据线、片选线和读/写控制线组成

- 存储单元:图示中的小方格表示1个字节(8比特),一整行表示1个存储字(示例中字长为4字节)

- 容量计算:示例芯片总容量为1KB(256个字×4字节),对应需要10根地址线(210=10242^{10}=1024210=1024)

2)编址方式

- 字节编址

- 基本规则:现代计算机按字节编址,每个字节对应唯一地址(示例中地址范围0-1023)

- 地址分配:连续分配地址,如0号字节、1号字节...1023号字节

- 其他编址方式

- 字寻址:1个字=4字节,字地址左移2位得起始字节地址(如1号字→二进制1左移2位=4)

- 半字寻址:1个半字=2字节,地址转换需左移1位

- 双字寻址:1个双字=8字节,地址转换需左移3位

- 单元数量:1KB存储器的寻址单元数分别为:字节寻址1024个、字寻址256个、半字寻址512个、双字寻址128个

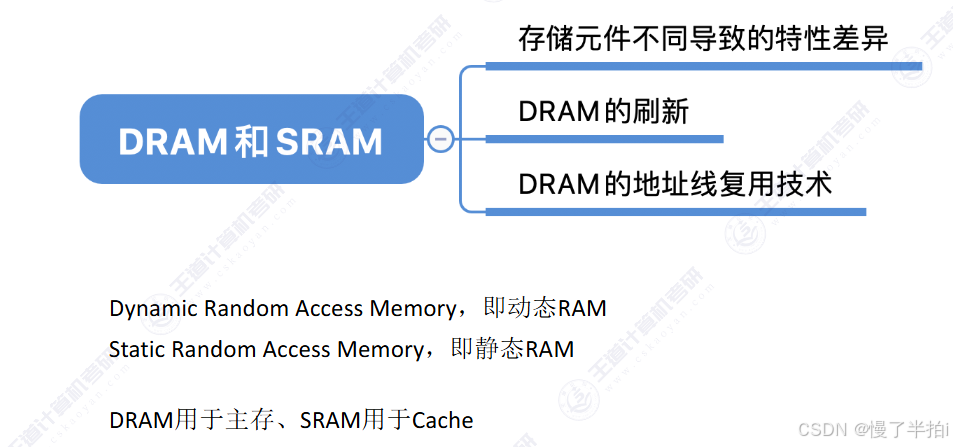

2.2 SRAM 芯片和 DRAM 芯片

1.SRAM与DRAM基本概念

- RAM定义: 随机访问存储器(Random Access Memory)的特点是存储单元读取速度不随物理位置改变

- DRAM全称: Dynamic Random Access Memory(动态随机存取存储器)

- SRAM全称: Static Random Access Memory(静态随机存取存储器)

- 典型应用:

- DRAM用于制造主存

- SRAM用于制造Cache(高速缓冲存储器)

- 高频考点: 两种存储芯片的特性对比是考试重点

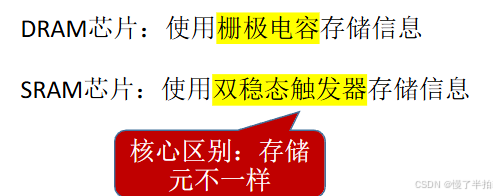

2.存储元件差异

- DRAM存储原理: 使用电容的充放电来存储信息 需要定期刷新保持数据

- SRAM存储原理: 使用双稳态触发器存储信息 不需要刷新操作

- 核心区别: 两种芯片的存储元件物理特性不同导致其他特性差异

3.DRAM与SRAM对比

- DRAM存储原理

- 存储机制:通过栅极电容存储电荷表示二进制信息,

1对应电容存储电荷(5V高电平),0对应无电荷(0V低电平)

- 写入操作:字选择线加5V高电平使MOS管导通,数据线输入5V(写1)或0V(写0)决定电容是否存储电荷

- 电荷分布:写1时上金属板聚集正电荷(5V),下金属板接地(0V)形成压差;写0时两极板无压差

- 存储机制:通过栅极电容存储电荷表示二进制信息,

- SRAM存储原理

- 存储机制:采用6个MOS管构成双稳态触发器,1对应A点高电平/B点低电平,0对应A点低电平/B点高电平

- 读出操作:

- 读1时BLX输出低电平 读0时BL输出低电平

- 写入操作:

- 写0:BL加低电平,BLX加高电平 写1:BL加高电平,BLX加低电平

- 存储元件特性对比

- 物理结构:

- DRAM:1个电容+1个MOS管

- SRAM:6个MOS管构成触发器

- 制造成本:DRAM单元成本显著低于SRAM

- 集成度:DRAM体积小集成度高,SRAM体积大集成度低

- 功耗差异:DRAM电路简单功耗低,SRAM电路复杂功耗高

- 物理结构:

- DRAM与SRAM芯片特性

- 易失性:两者均为断电信息消失的易失性存储器

- DRAM刷新机制

刷新频率:由于电容最多只能保持两毫秒的电荷,所以必须在两毫秒之内给电容重新充电刷新

刷新单位:以行为单位进行刷新,每次刷新一行存储单元(每个存储单元由多个存储元构成)

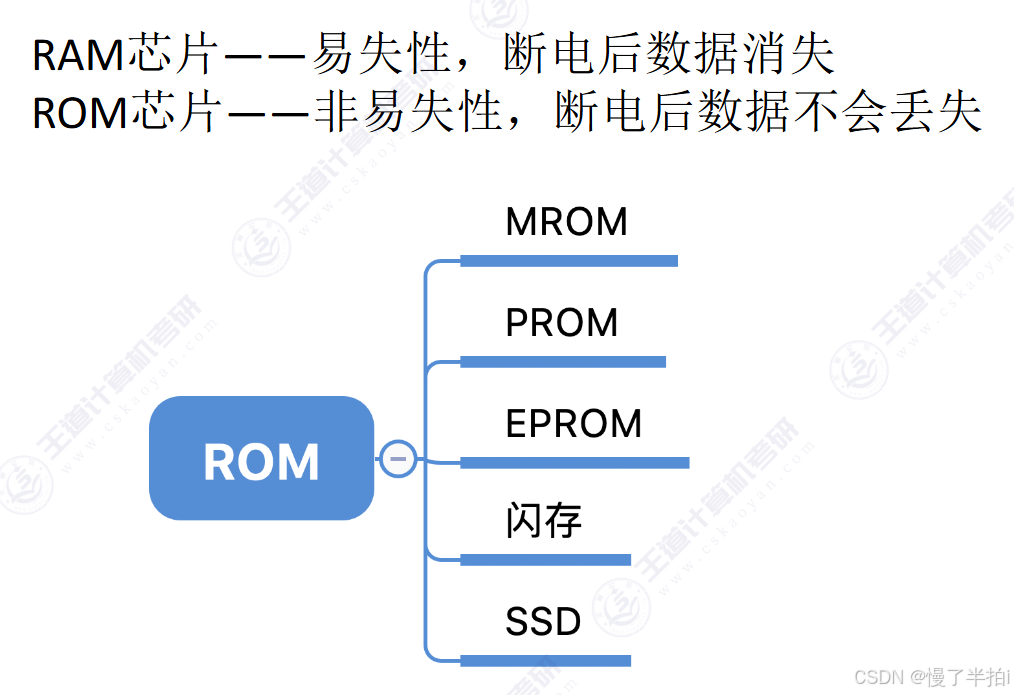

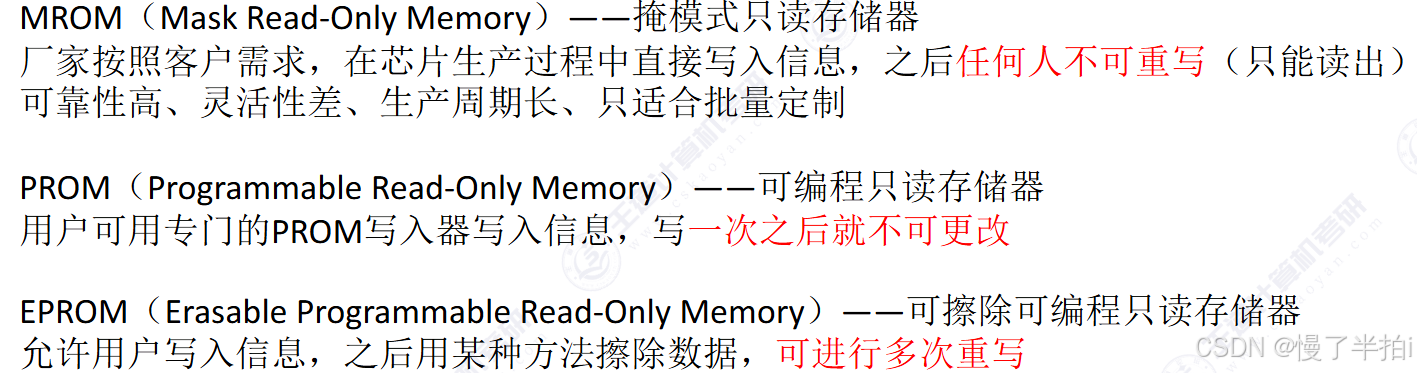

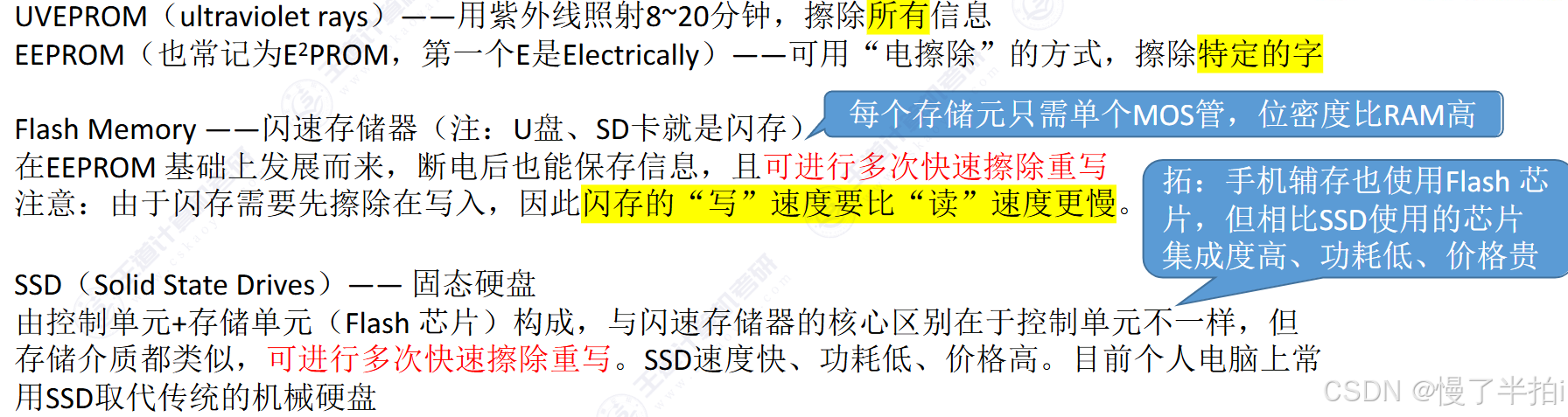

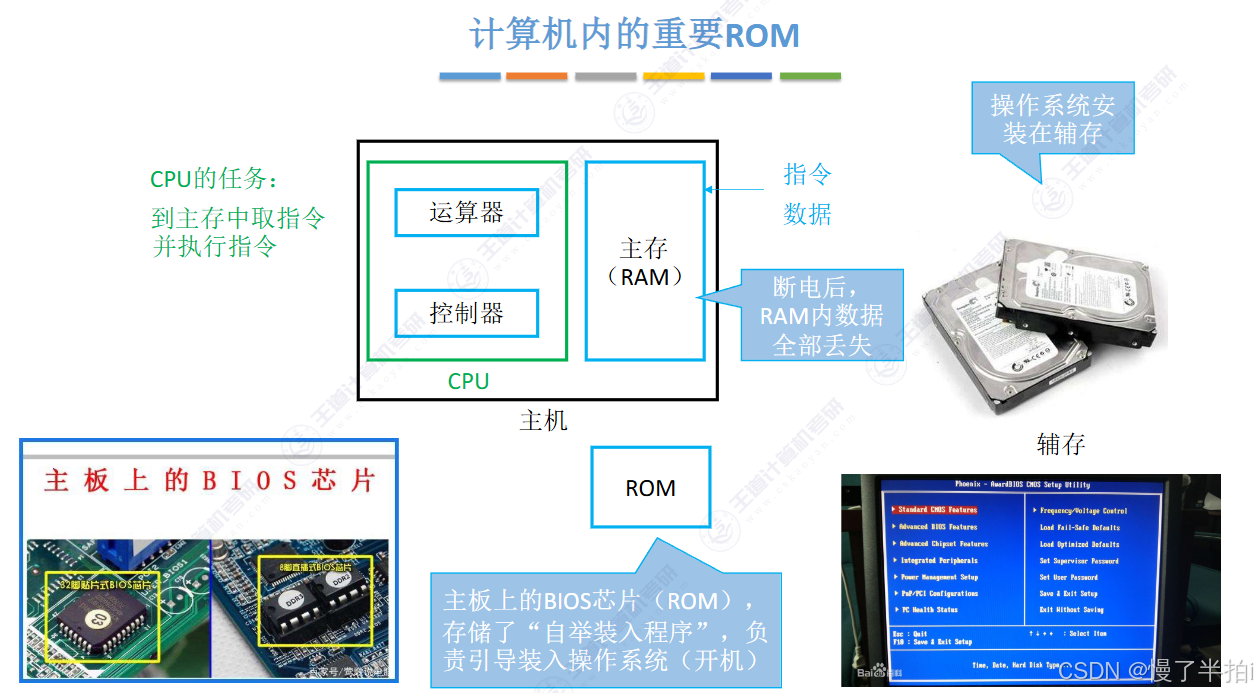

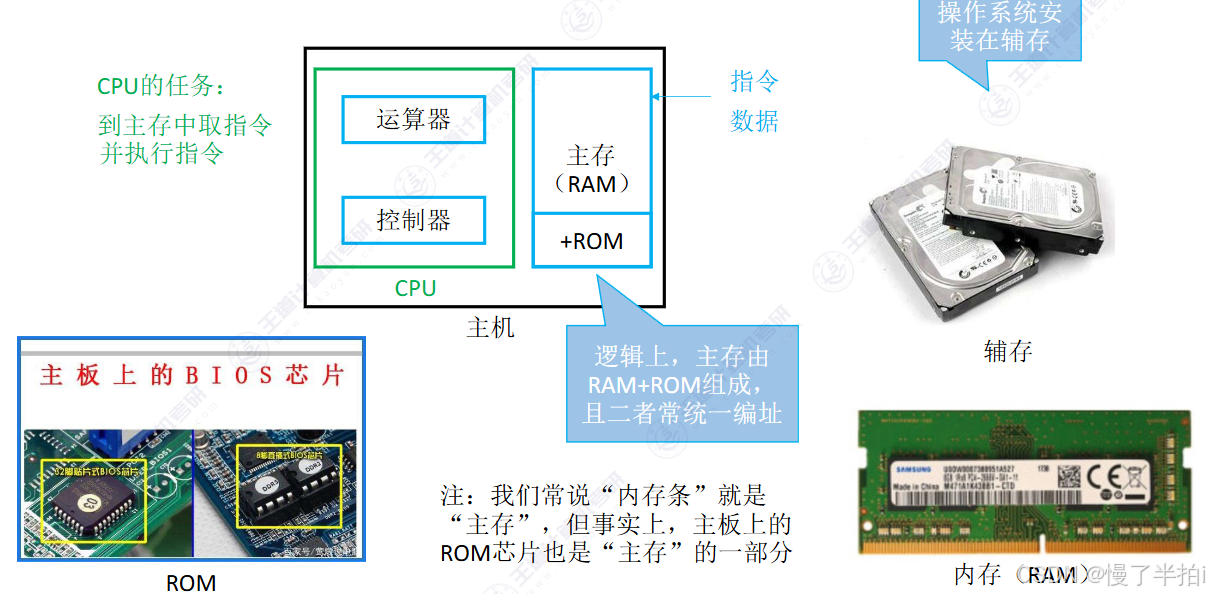

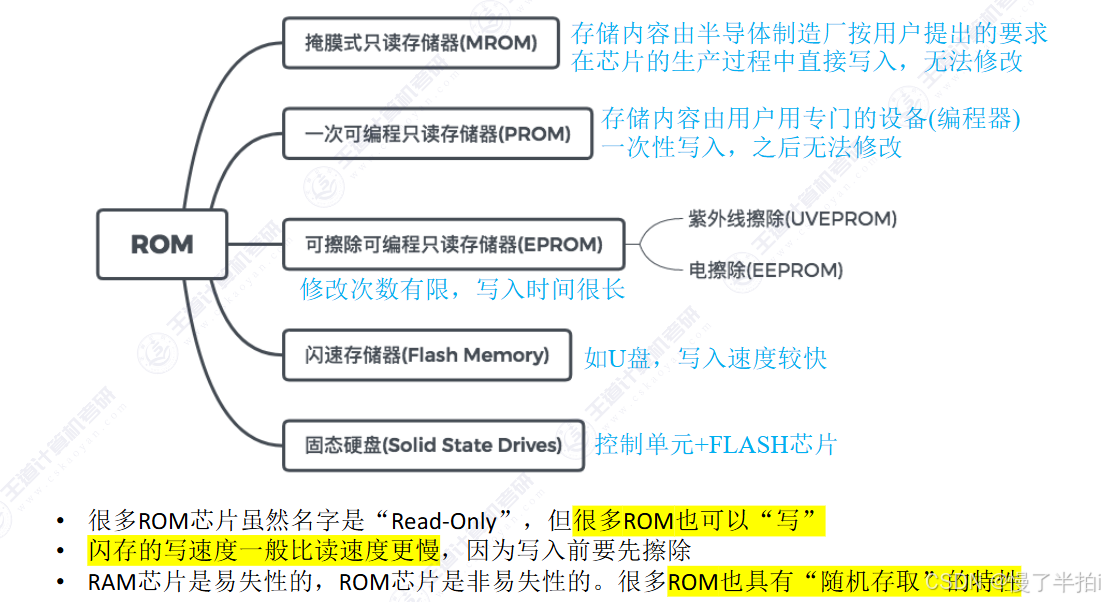

2.3 只读存储器

2.4 多模块存储器

三、主存储器与 CPU 的连接

3.1 连接原理

3.2 主存容量的扩展

3.3 存储芯片的地址分配和片选

3.4 存储器与CPU的连接

四、外部存储器

4.1 磁盘存储器

4.2 固态硬盘

五、高速缓冲存储器

5.1 程序访问的局部性原理

5.2 Cache的基本工作原理

5.3 Cache和主存的映射方式

5.4 Cache 中主存块的替换算法

5.5 Cache写策略

六、虚拟存储器

6.1 虚拟存储器的基本概念

6.2 页式虚拟存储器

6.3 段式虚拟存储器

6.4 段页式虚拟存储器

6.5虚拟存储器与 Cache 的比较