目录

1.引言

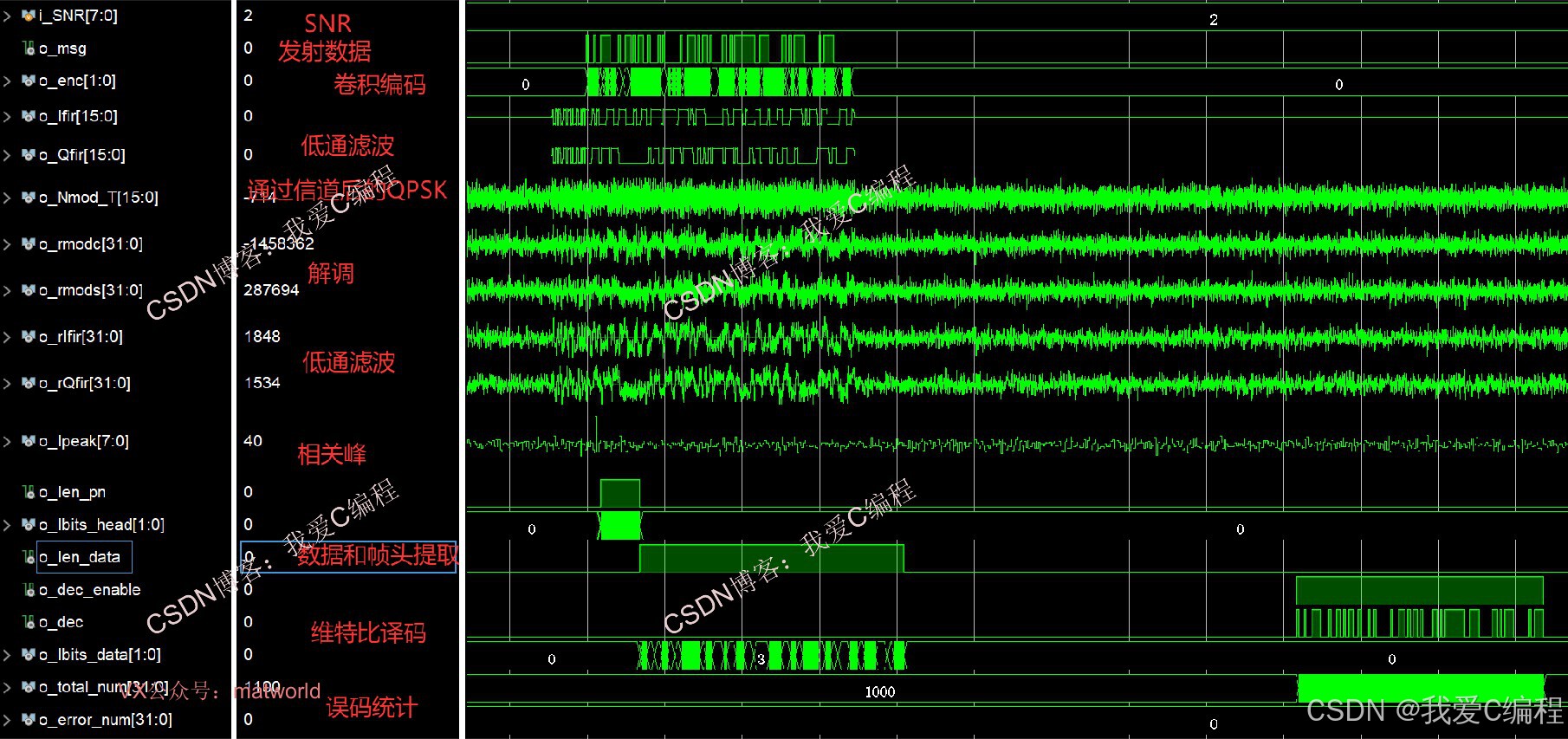

基于FPGA的QPSK软解调+卷积编码Viterbi译码通信系统开发,包含帧同步,高斯信道,误码统计,可设置SNR。系统包括QPSK调制模块,QPSK软解调模块,217卷积编码模块,维特比译码模块,AWGN信道模块,误码统计模块,帧同步模块,数据源模块等。

2.算法仿真效果

本系统是在

基于FPGA的QPSK软解调+帧同步系统开发,包含testbench,高斯信道,误码统计,可设置SNR_qpsk 帧同步-CSDN博客

基础上,增加了217卷积编码,维特比译码(不使用编译码IP核),从而提升系统性能。

vivado2022.2测试

设置SNR=7db

设置SNR=2db

我们对比

基于FPGA的QPSK+卷积编码Viterbi译码通信系统开发,包含帧同步,高斯信道,误码统计,可设置SNR-CSDN博客

将QPSK加入软解调之后,性能可以进一步提升,当SNR=2db时,误码率为0。

3.算法涉及理论知识概要

整体系统结构如下所示:

数据源模块 → 217卷积编码模块 → QPSK调制模块 → AWGN信道模块 →

QPSK软解调模块 → 帧同步模块 → 维特比译码模块 → 误码统计模块

3.1 QPSK

QPSK是一种数字调制方式,它将两个二进制比特映射到一个符号上,使得每个符号代表四种可能的相位状态。因此,QPSK调制解调系统可以实现更高的传输速率和更高的频谱效率。基于FPGA的QPSK调制解调系统通常由以下几个模块组成:

数据生成模块:生成要传输的二进制数据流。

QPSK调制模块:将二进制数据流转换为符号序列,并将每个符号映射到特定的相位状态。

QPSK解调模块:将接收到的符号序列解调为二进制数据流。

QPSK调制模块

QPSK调制模块将二进制数据流转换为符号序列,并将每个符号映射到特定的相位状态。QPSK调制使用四个相位状态,分别为0度、90度、180度和270度。在QPSK调制中,每个符号代表两个比特,因此,输入二进制数据流的速率必须是符号速率的两倍。

QPSK调制模块通常使用带有正弦和余弦输出的正交调制器(I/Q调制器)来实现。在I/Q调制器中,输入信号被分成两路,一路被称为“正交(I)路”,另一路被称为“正交(Q)路”。每个输入符号被映射到一个特定的正交信号,然后通过合成器将两个信号相加,形成QPSK调制信号。

QPSK软解调模块

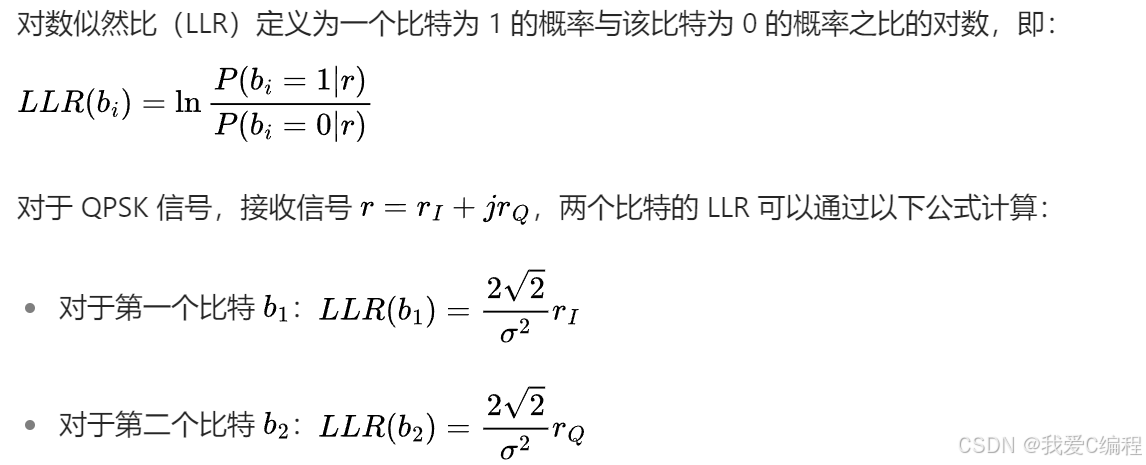

软解调是QPSK软解调的关键步骤,它利用判决符号和相位估计的结果进行概率估计,以提高解调的准确性。假设判决符号为d_hat,软解调过程的结果为软解调符号d。常见的软解调公式为:

该概率可以通过估计信号点的概率分布函数或使用最大似然估计等方法得到。软解调过程需要进行概率估计,以提高解调的准确性。这涉及到估计信号点的概率分布函数或使用其他概率估计方法,其中噪声的影响需要被适当地考虑。

3.2 帧同步

在数字通信中,信息通常是以帧为单位进行组织和传输的。帧同步的目的是确定每一帧的起始位置,以便接收端能够正确地解调出每帧中的数据。

设发送的帧结构为:帧同步码 + 信息码元序列 。帧同步码是具有特定规律的码序列,用于接收端识别帧的起始。

帧同步的过程就是在接收序列中寻找与帧同步码匹配的位置,一旦找到匹配位置,就确定了帧的起始位置,后续的码元就可以按照帧结构进行正确的划分和处理。

3.3 卷积编码,维特比译码

卷积编码是一种前向纠错编码方式,特别适用于无线通信和其他信道条件恶劣的应用场景。它主要通过卷积算子将信息序列映射成冗余度更高的码字序列。典型的卷积编码器由两个移位寄存器和一个加法器构成,遵循一定的生成多项式进行编码。

设信息序列是 u(n),卷积编码器的两个生成多项式为 G1(D) 和 G2(D),则编码输出v(n) 可以表示为:

v(n)=u(n)G1(D)+u(n−1)G2(D)+…

此处D 是延迟算子,实际表达形式取决于具体选择的生成多项式阶数及系数。

维特比译码是用于最大似然序列估计的一种动态规划算法,广泛应用于卷积编码以及其他序列编码的译码过程中。在卷积编码中,维特比译码器通过构造一棵称为“状态转移图”或“trellis”的树状结构来寻找最有可能的原始信息序列路径。

在 Viterbi 译码算法中,每一步都需要计算分支量度,路径量度,以及更新幸存路径,同时还需要知道状态转移网格图,时序控制等信息,其原理图如图:

假设维特比译码器面对的是接收到的带有噪声的码字序列y(n),其目标是最小化汉明距离或最大化似然性。维特比算法的核心在于维护每一步的状态概率以及从起始状态到达当前状态的最佳路径累积代价。

状态转移方程: 对于每个时刻n 和每一个状态Sj,其下一状态Sk 的最佳路径累积代价C(n,Sk) 可以递归地表示为所有前一状态Sj 的累积代价加上相应路径的概率增益:

C(n,Sk)=Sj∈prev(Sk)min[C(n−1,Sj)+P(y(n)∣Sk)]

其中,prev(Sk) 表示状态Sk 的前驱状态集合,P(y(n)∣Sk) 是给定当前状态Sk 下观测到y(n) 的概率。

终止状态判决: 译码结束时,选取累积代价最小的终止状态对应的路径作为最优解,回溯此路径即得到最优译码结果。

4.Verilog程序接口

module QPSK_tops(

input i_clk,

input i_clkdx,

input i_clkd2x,

input i_rst,

input signed[1:0]i_en,

input i_bits,

input signed[7:0]i_SNR,

output [1:0]o_enc,

output signed[15:0]o_Ifir,

output signed[15:0]o_Qfir,

output signed[15:0]o_Nmod_T,

output signed[31:0]o_rmodc,

output signed[31:0]o_rmods,

output signed[31:0]o_rIfir,

output signed[31:0]o_rQfir,

output [1:0]o_Ibits_data,

output [1:0]o_Ibits_head,

output [7:0]o_Ipeak,

output o_Ien_data,

output o_Ien_pn,

output o_Iframe_start,

output [1:0]o_Qbits_data,

output [1:0]o_Qbits_head,

output [7:0]o_Qpeak,

output o_Qen_data,

output o_Qen_pn,

output o_Qframe_start,

output o_dec_enable,

output o_dec,

output signed[31:0]o_error_num,

output signed[31:0]o_total_num

);

0sj2_080m5.参考文献

[1]罗常青,安建平,沈业兵.采用(2,1,7)卷积码+QPSK的中频调制解调系统的FPGA实现[J].电子技术应用, 2005, 31(10):3.DOI:10.3969/j.issn.0258-7998.2005.10.027.

[2]梁开勇,文红,吴一帆,等.FQPSK软解调信息提取新方法[J].电讯技术, 2009, 49(11):5.DOI:10.3969/j.issn.1001-893x.2009.11.009.

6.完整算法代码文件获得

完整程序见博客首页左侧或者打开本文底部

V