软件安装

首先通过Lattice官网下载Diamond软件,官网地址https://www.latticesemi.com/

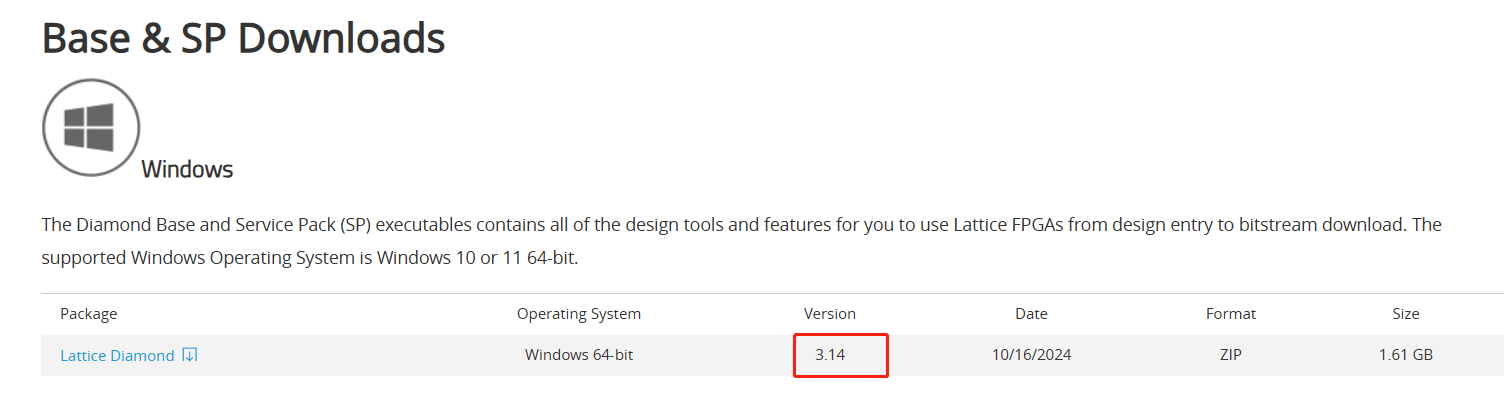

找到Diamond安装软件,如下图所示:

本次下载的是3.14最新版本,选择Windows安装,如下图所示:

下载完软件后需要在官网申请License,其中free license是免费的,该license一般使用在较低端的Lattice芯片上,选期间时需要注意,避免License不能使用,如下图所示:

本次采用的是MachXO2类产品,产品型号为LCMX02-1200HC-4MG132C。LICENSE需要自己创建lattice官方账号后发送邮箱申请,申请时需要填写电脑MAC地址,这里不做详细介绍。

获取License后将lincense.dat放在安装位置指定目录,如下图所示:

做环境变量更改,在我的电脑属性里查找环境变量,如下图所示:

在属性界面里找到高级系统设置:

在本地添加环境变量LM_LICENSE_FILE,值为前面License放置的目录,如下图所示:

到这里软件安装结束。

创建工程

双击diamond,创建一个led_demo点灯的工程:

选择工程名和工程路径,然后点击next:

选择本次工程使用的FPGA芯片类型和型号再一直点击next:

工程创建完毕后再添加文件,这里需要在impl1选择add、new file操作

选择创建一个命名为led_top的.v文件:

进行简单的代码编写,如下:

module led_top(

input clkin,

input sys_rst_n,

output reg led

);

reg[31:0] cnt;

wire sys_clk_100;

sys_pll sys_pll_inst(

.CLKI(clkin),

.CLKOP(sys_clk_100)

);/* synthesis NGD_DRC_MASK=1 */;

always @(posedge sys_clk_100 or negedge sys_rst_n)begin

if(sys_rst_n == 'd0)begin

cnt <= 32'h00000000;

led <= 1'd0;

end

else if(cnt >= 32'd25000000)begin

cnt <= 32'h00000000;

led <= ~led;

end

else begin

cnt <= cnt + 1'b1;

end

end

endmodule

使用IP

以上 代码使用了一个PLL IP,IP 的调用如下:

选择一个命名为sys_pll文件的PLL,生成代码类型为verilog:

对PLL做配置:

配置完成后点击Generate,这里需要注意的是需要先点击下划线里的calculate,否则generate是灰色的。

生成IP不会直接应用在工程里,需要手动添加.v文件,如下图所示:

添加.v文件

到这里PLL例化结束,可以在工程里看到顶层文件下有PLL文件。如下:

到这一步可以点击编译软件,如果编译成功代表代码编写没问题,如下所示:

约束

接下来做管教约束,在tools工具栏里打开引脚约束

主要对管脚和电平属性做约束,电平属性根据硬件环境选择。

点击保存后会生成约束文件,后期改动也可以直接在约束文件里面做修改,生成约束文件代码如下:

工程比较简单,为保证约束的完整性再做一个时钟频率约束,如下图所示:

配置如下:

PAR-ADJ是Lattice时钟约束中用于预布局布线时序优化的参数,通过增加时钟不确定性余量,确保设计在物理实现后仍满足时序要求。合理配置该参数对平衡设计性能和可靠性至关重要。

Clock Jitter(时钟抖动) 是指时钟信号边沿(上升沿或下降沿)相对于理想时序位置的短期、非累积性偏差。它是时钟信号质量的关键指标,直接影响电路的时序余量(Timing Margin)和可靠性。

以上两个参数暂时不做设置,点击OK完成后再查询约束文件如下:

重新编译工程,生成烧录文件,如下:

查询约束没有问题,生成JEDEC文件。

文件烧录

接下来上板烧录,板卡上电,店家programmer烧录界面,如下图所示:

根据烧录器选择型号,本次烧录器Cable选用的是FTDI。

点击烧录后,系统会进行擦除烧录动作,烧录成功后显示pass,如下图所示:

此时板卡LED灯闪烁,功能实现:

在线调试

一般功能验证过程中少不了debug环节,LATTICE的debug也需要先添加debug信号,点击创建debug信号如下:

选择要抓取的信号和深度

选择触发条件:

这里选择LED信号的上升沿作为触发信号,所以选择trriger unit作为触发。

trigger unit和trigger expression触发的区别如下:

| 特性 | Trigger Unit | Trigger Expression |

|---|---|---|

| 作用 | 监测单个信号或简单条件 | 组合多个 Trigger Units 的条件 |

| 复杂度 | 低(边沿、电平、计数器等) | 高(支持逻辑运算和时序关系) |

| 资源占用 | 占用硬件资源(数量有限) | 不额外占用硬件(基于表达式逻辑) |

| 示例 | 信号 A 的上升沿 |

(A上升沿) AND (B=1) |

点击SAVE ALL,选择保存DEBUG文件路劲,如下图所示:

再将RVL文件添加到工程中,如下图所示:

在debug目录添加rvl文件

重新生成bit和jedec文件,如下所示:

首先烧录JEDEC文件,这里不再阐述。

然后导入debug,如下图所示:

选择当前环境和文件目录 :

弹出debug页面后可以重新选择触发条件,比如选择led的下降沿作为触发,再点击LA Waveform页面

点击抓取,抓取结果如下:

到这里debug功能简单介绍完毕。