目录

一、PS侧电源

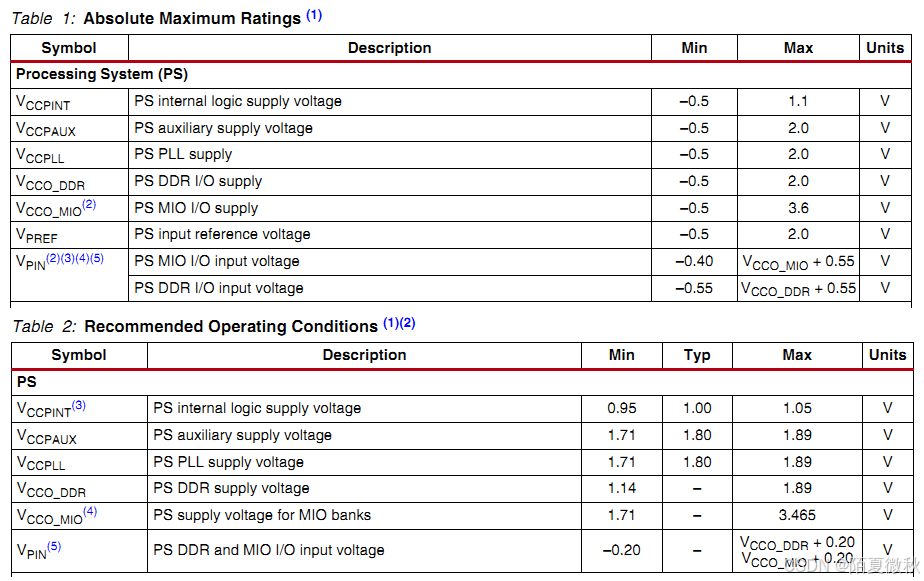

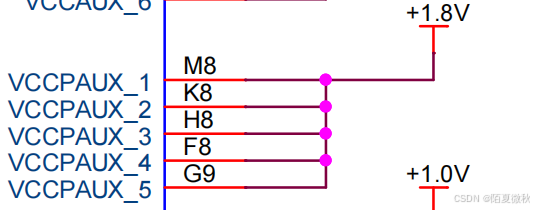

1、VCCPINT

PS内部逻辑(内核)电源电压,最大不超过1.1V;一般设计采用1.0V,要求1.0V±3%;

该电源网络命名为VCCPINT_1V0;保证100uF、4.7uF、0.47uF电容至少各1个,其余每个电源管脚视PCB面积保证至少有1个4.7uF或0.47uF去耦电容。

另外,VCCPINT_1V0的上电爬升时间要求为0.2ms-50ms。

2、VCCPAUX

PS辅助电源电压,最大不超过2.0V;一般设计采用1.8V,要求1.8V±5%。

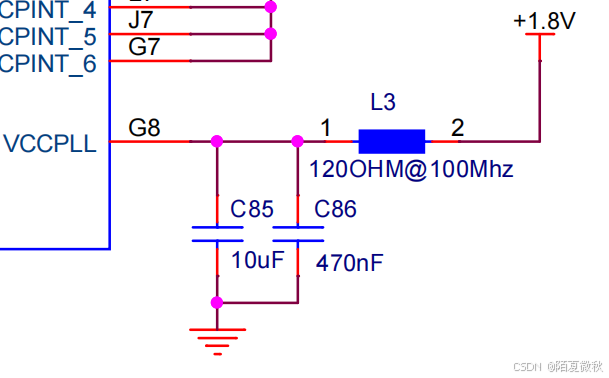

3、VCCPLL

PS PLL电源,PLL内部时钟供电电源,最大不超过2.0V;一般设计采用1.8V,要求1.8V±5%;

通常串磁珠消除电源链路的RF噪声;保证100uF、4.7uF、0.47uF电容至少各1个,其余每个管脚视PCB面积保证至少有1个4.7uF或0.47uF去耦电容。

针对VCCPAUX、VCCPLL,通常共用一路1.8V的电源,该电源网络命名为VCCPAUX_1V8;为滤除噪声干扰,推荐在该1.8V电源网网络和VCCPLL管脚之间串接磁珠。

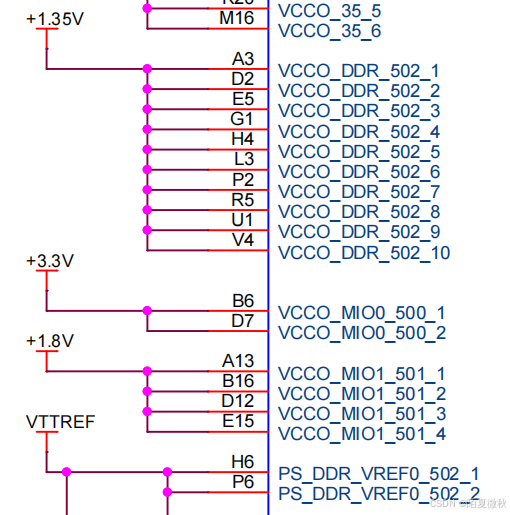

4、PS_VCCO(VCCO_MIO)

PS VCCO包括PS_VCCO_DDR、PS_VCCO_MIO I/O电源,一般根据外设选择相应的电源,外设不同电源电压可能会有差异;

VCCO_DDR连接DDR3,可使用1.5V的电源电压,要求1.5V±3%。

VCCPINT →VCCPAUX&VCCPLL →PS_VCCO,即VCCPINT_1V0 →VCCPAUX_1V8 →VCCO_1V5;

二、PL侧电源

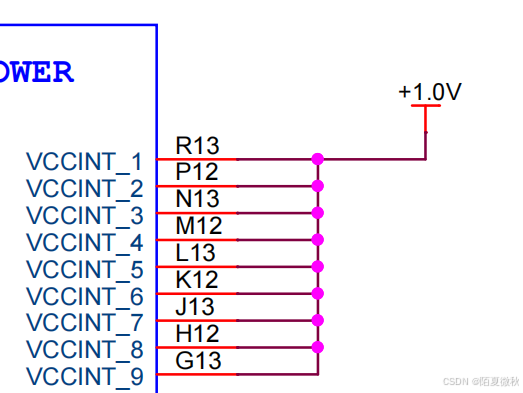

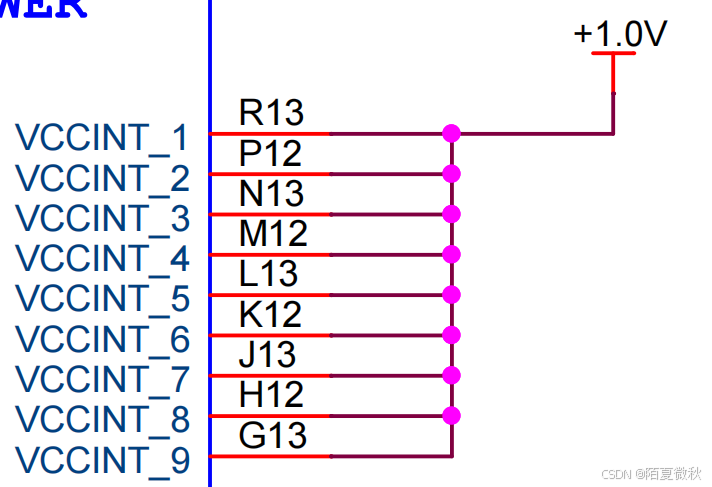

1、VCCINT

VCCINT为内核供电,即用于FPGA运行工作。要求供电电源为1.0V±3%;该电源网络命名为VCCINT_1V0;由于VCCINT_1V0电源电流很大,在靠近电源芯片侧,需要放置2个680uF或4个330uF的电容(由于低气压要求,不能使用钽电容),用于储能;另外,每个电源管脚视PCB面积保证至少有1个4.7uF或0.47uF去耦电容。该电源的上电爬升时间要求为0.2ms-50ms。

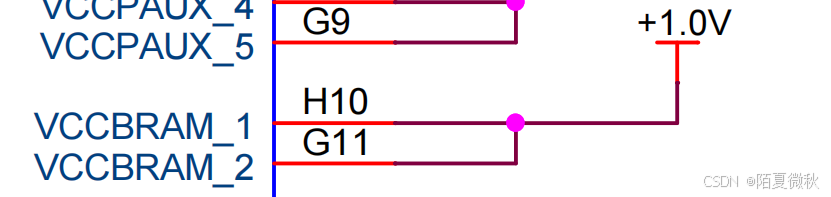

2、VCCBRAM

RAM电源电压,要求供电电源为1.0V±3%;该电源网络可以直接连接到VCCINT_1V0,VCCINT and VCCBRAM可用同一电源供电。

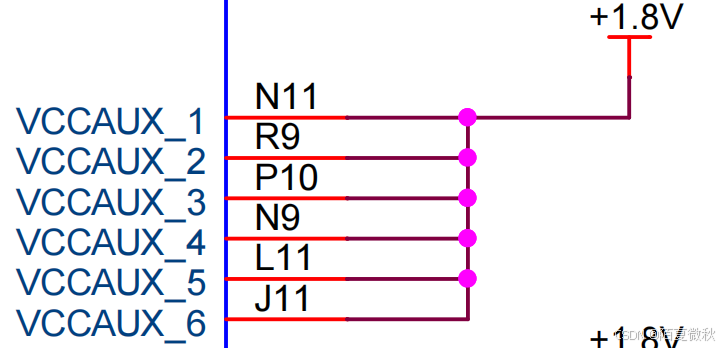

3、VCCAUX

FPGA辅助电源电压辅助电源,要求供电电源为1.8V1.8V±5%,该电源网络命名为VCC_PL_1V8;保证至少有1个100uF电容,其余每个管脚视PCB面积保证至少有1个100nF去耦电容;该电源的上电爬升时间要求为0.2ms-50ms。

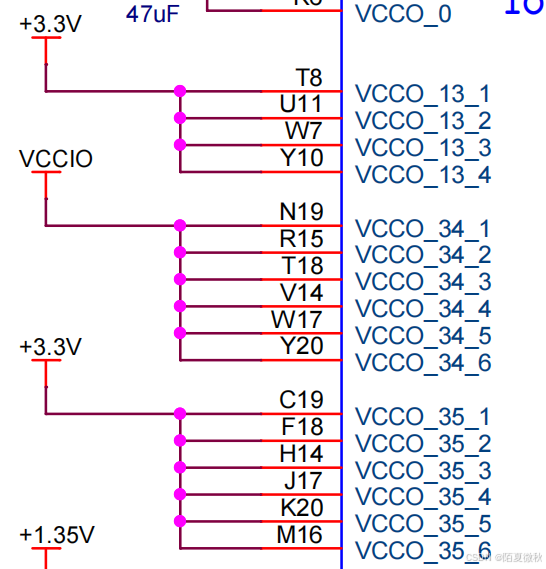

4、VCCO

Bank的IO电源电压,K7芯片有HR和HP两种Bank;

- HR Bank的VCCO范围是1.2V-3.3V;HP Bank VCCO一般使用1.8V,要求1.8V±5%,该电源网络命名为VCCO_1V8,该电源网络可以直接连接到VCC_PL_1V8;

- HP Bank的VCCO范围是1.2V-1.8V。HR Bank VCCO一般使用3.3V,要求3.3V±5%,该电源网络命名为VCCO_3V3。

5、VCCAUX_IO

PL IO辅助电源电压,根据不同的速率要求,IO辅助电压可以选择为1.8V或者2.0V。

一般使用1.8V IO作为辅助电压,要求1.8V±5%,该电源网络可以直接连接到VCC_PL_1V8;VCCAUX, VCCAUX_IO, and VCCO_1V8可用同一电源供电。

VCCINT&VCCBRAM→VCCAUX&VCCAUX_IO&VCCO_1V8 →VCCO,即VCCINT_1V0→VCC_PL_1V8 →VCCO_3V3;

三、MGT电源

1、VMGTAVCC

GTX收发器的模拟电源电压、锁相环电源,其电压大小一般由QPLL频率决定,一般低于10GHz的使用1.0V,要求1.0V±3%;该电源网络命名为MGTXAVCC_1V0。

2、VMGTAVTT

GTX收发器的端接电路的模拟电源电压,一般使用1.2V,要求1.2V±0.03V;该电源网络命名为MGTXAVTT_1V2。

3、VMGTVCCAUX

GTX收发器的辅助模拟QPLL电源电压,一般使用1.8V;该电源要求为1.8V±0.05V。按照规范,把该信号命名为MGTVCCAUX_1V8,很多设计中VMGTVCCAUX与VCCAUX用同一电源网络VCC_PL_1V8。

VCCINT →VMGTAVCC →VMGTAVTT或者 VMGTAVCC →VCCINT →VMGTAVTT;

并且 VMGTAVCC 和 VCCINT可以同时上电;对VMGTVCCAUX时序没有要求

四、上电时序

PS侧上电时序:VCCPINT_1V0 →VCCPAUX_1V8 →VCCO_1V5;

PL侧电源(FPGA)上电时序:VCCINT_1V0 →VCC_PL_1V8→VCCO_3V3;

GTX模块时序:VCCINT_1V0→MGTXAVCC_1V0→MGTXAVTT_1V2→MGTVCCAUX_1V8;

根据以上分析,可将一些电源合并以简化上电时序:

VCCPINT_1V0、VCCINT_1V0 可合并;

VCCPAUX_1V8、VCC_PL_1V8、MGTVCCAUX_1V8 可合并;

VCCO_1V5&VCCO_3V3可同时上电。

合并后:VCCINT_1V0→MGTXAVTT_1V2→VCC_PL_1V8 →VCCO_1V5&VCCO_3V3 →PS_POR_B

五、BANK设计

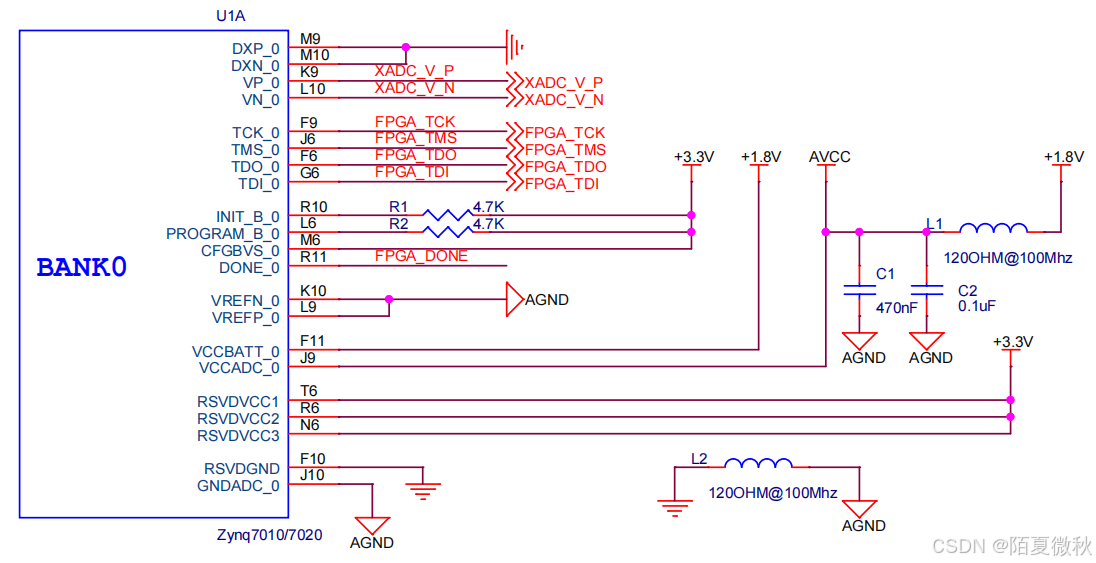

1、BANK0-功能

主要是辅助供电,XADC、JTAG等。

2、BANK34 35-PL

(1)、IO

几乎都可以做IO。

(2)、时钟

注重MRCC、SRCC。

(3)、差分

差分对必须固定。

(4)、专用

AD、DQS、VREF等。

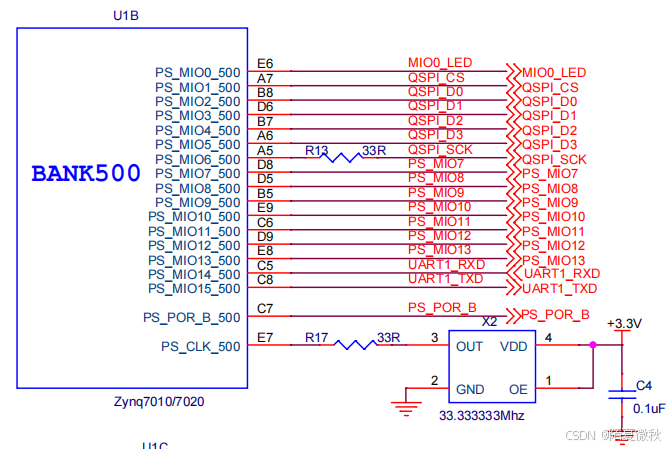

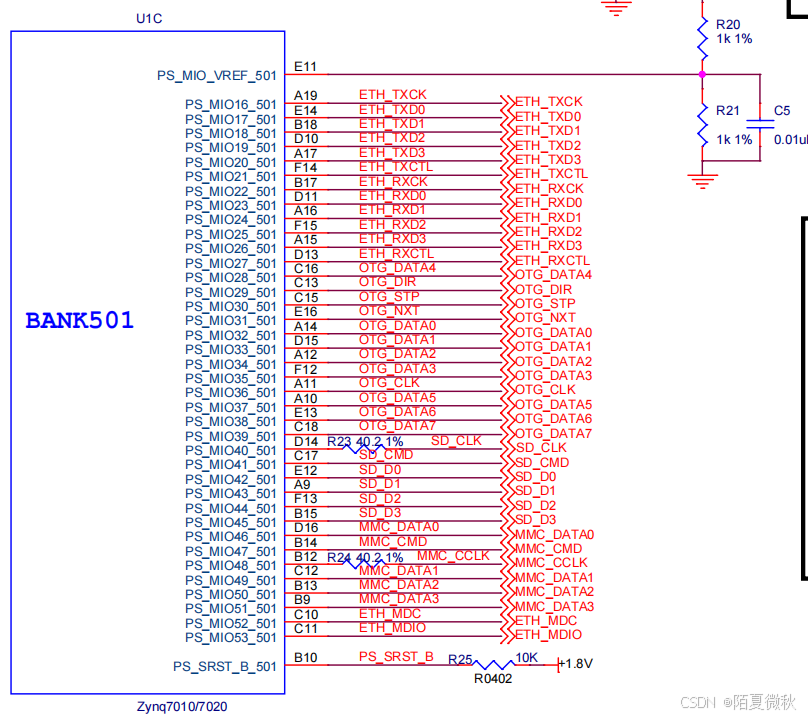

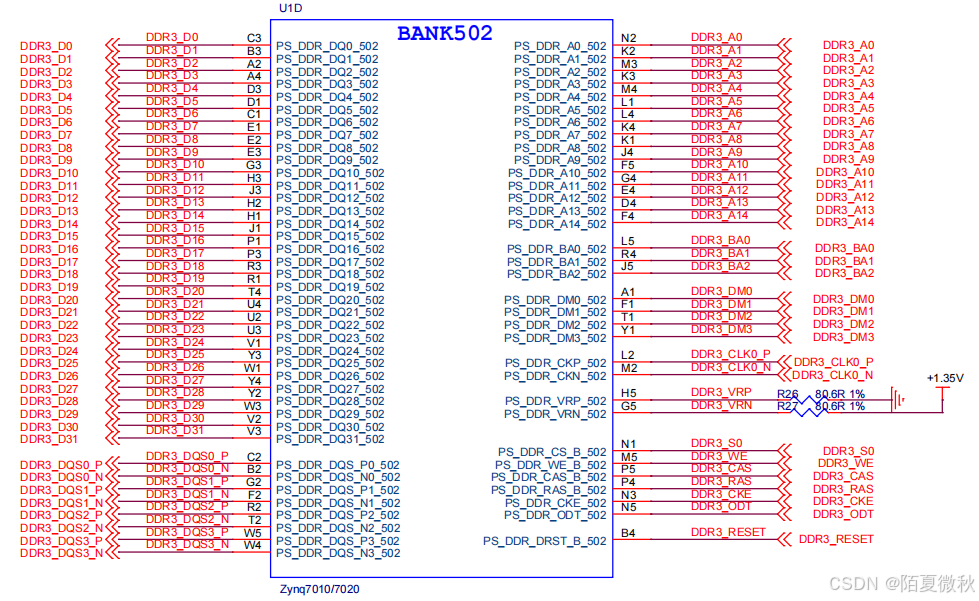

3、BANK500 501 502

PS端对专用IO更加做出了限制。

表面看好似只有BANK502命名为DDR专用。

实际上由于ARM的限制,其不像FPGA随意变更,IO负责的外设几乎全部确定。例如:IIC、SPI、USB、QSPI、UART、ETH等。虽然标注的全都是MIO常规。