目录

7. MDC (Management Data Clock)

8. MDIO (Management Data Input/Output)

5. VDD_ANA (Analog Power Supply)

9. VDD_EXT (External Power Supply)

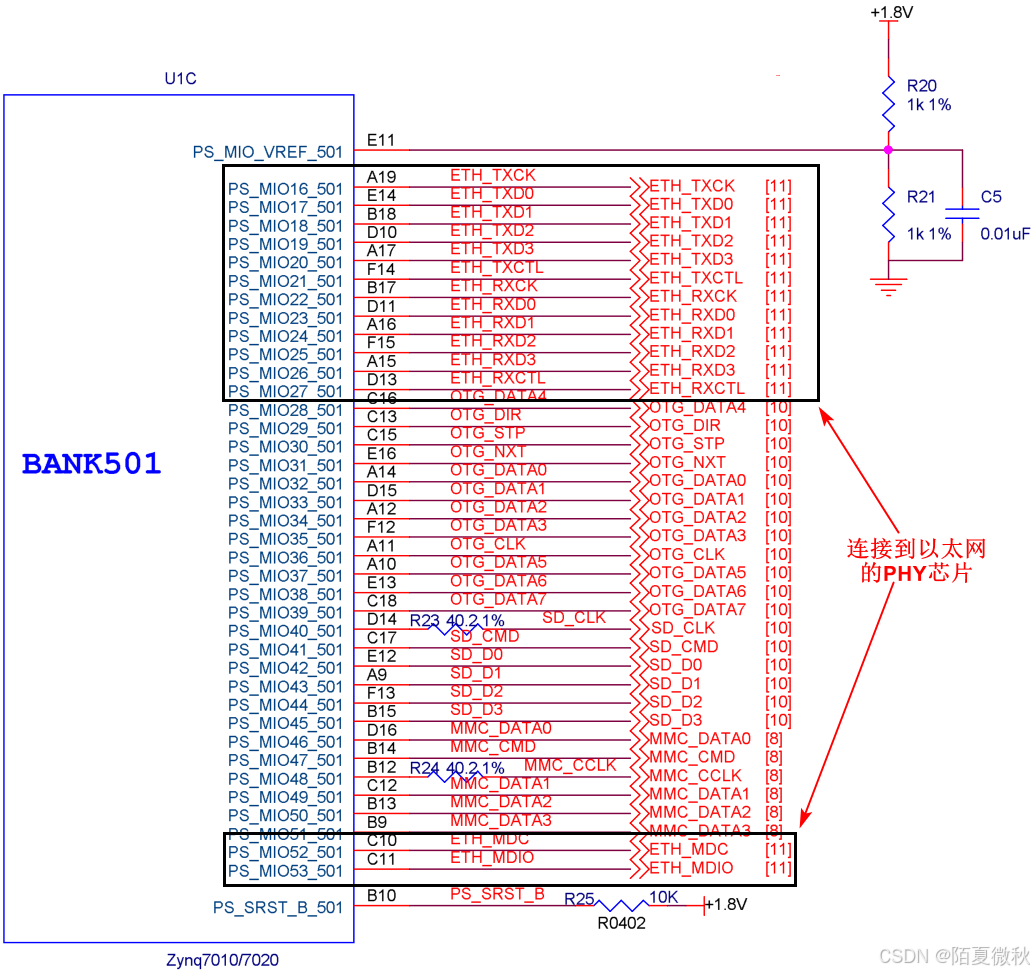

一、PS以太网

比较推荐,因为PS端具有专用IO,且PL可以直接读写PS端的DDR。

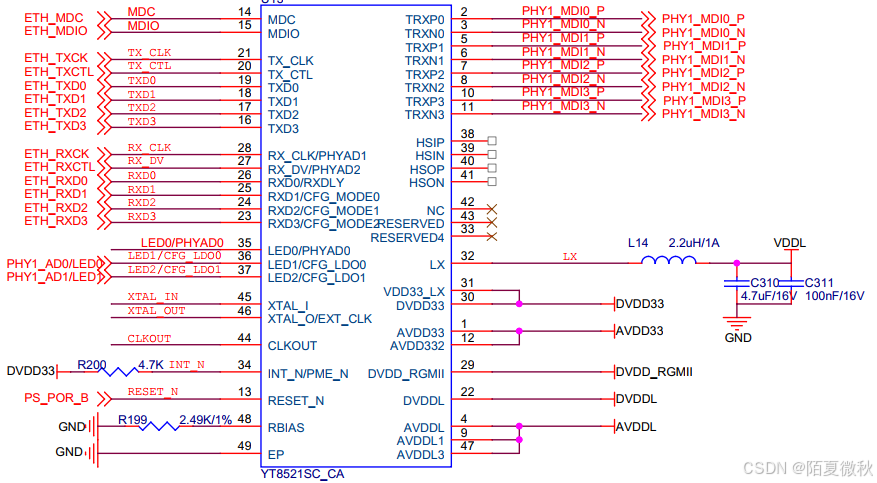

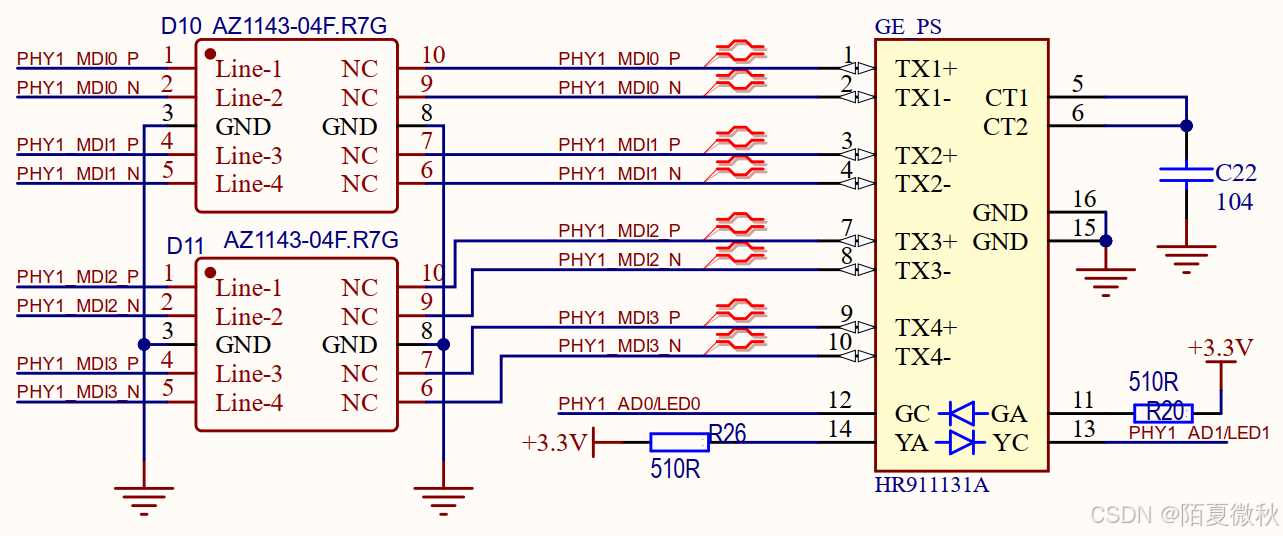

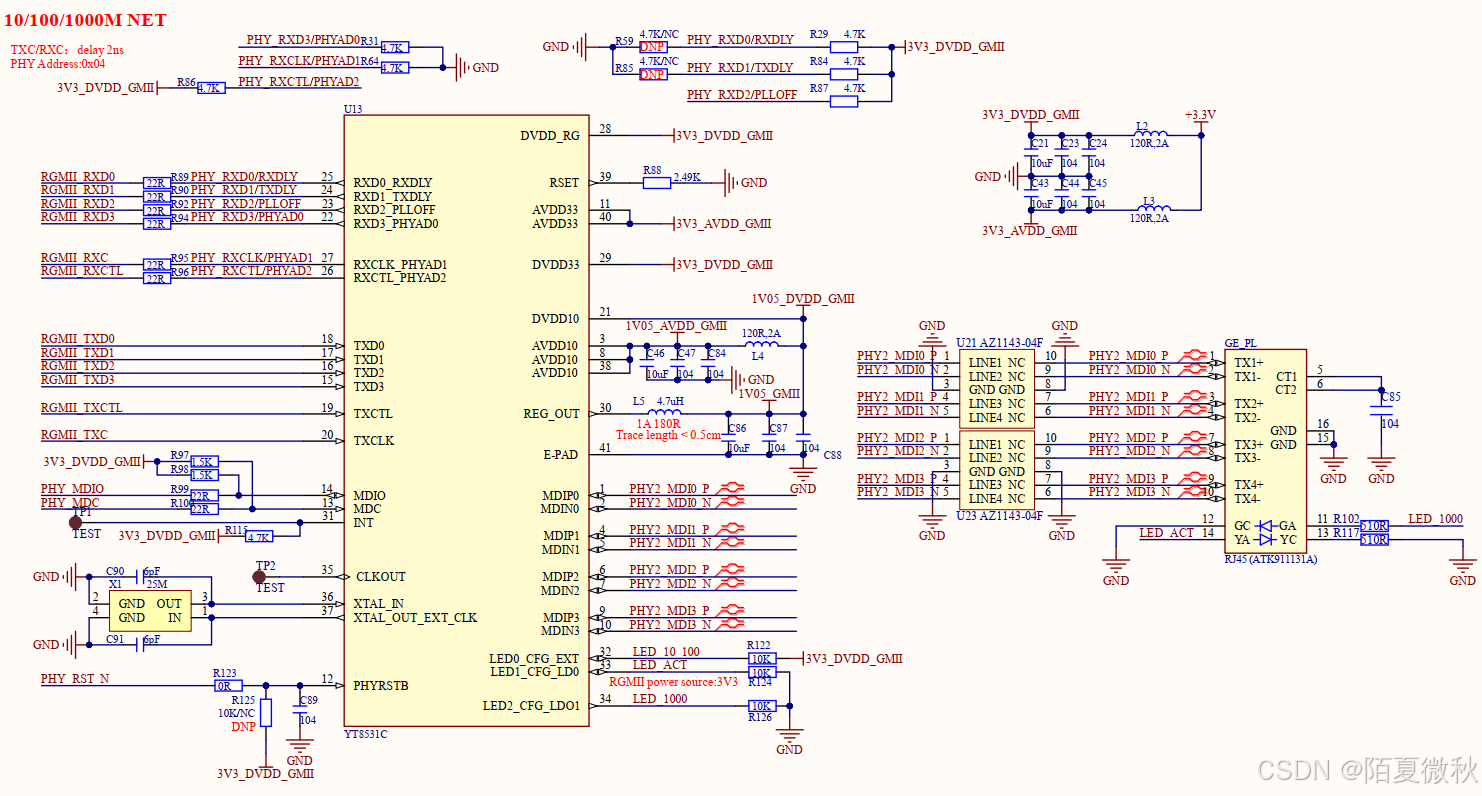

1、原理图设计

连接ETH_TXCK、TXDx、TXCTL、RXCK、RXDx、RXCTL、MDC、MDIO。

在以太网(Ethernet)外设的硬件设计中,涉及到的信号如ETH_TXCK、TXDx、TXCTL、RXCK、RXDx、RXCTL、MDC、MDIO等,都是以太网MAC(Media Access Control)层和PHY(Physical Layer)之间通信的关键接口信号。下面是每个信号的作用说明:

1. ETH_TXCK (Transmit Clock)

- 作用:传输时钟信号,用于同步数据发送。

- 描述:ETH_TXCK是用于控制以太网数据发送的时钟信号。它决定了数据传输的速率和时序。在大多数设计中,它通常与数据总线(TXDx)和控制信号(TXCTL)一起工作,确保数据按正确的时序发送。

2. TXDx (Transmit Data)

- 作用:传输数据总线,用于发送数据。

- 描述:TXDx是一个或多个数据线(通常是4、8或10条),用于将以太网数据从MAC发送到PHY。在以太网数据包发送过程中,TXDx承载着实际的数据负载。根据不同的以太网标准(如10/100/1000Mbps),数据宽度可能有所不同。

3. TXCTL (Transmit Control)

- 作用:发送控制信号,用于指示数据传输的开始和结束等控制信息。

- 描述:TXCTL是一个控制信号,通常是用来指示数据帧的开始、结束或其他控制信息(例如,数据有效/无效)。它可以包括冲突检测、数据使能等控制标志,帮助MAC和PHY之间进行同步。

4. RXCK (Receive Clock)

- 作用:接收时钟信号,用于同步数据接收。

- 描述:RXCK是用于控制接收数据的时钟信号,它决定了接收数据的速率和时序。它与接收数据总线(RXDx)和接收控制信号(RXCTL)一起工作,确保数据按正确的时序从PHY传输到MAC。

5. RXDx (Receive Data)

- 作用:接收数据总线,用于接收数据。

- 描述:RXDx是一个或多个数据线(通常是4、8或10条),用于从PHY传输数据到MAC。通过RXDx,MAC能够接收来自网络的以太网数据帧。在不同的以太网标准中,RXDx的数量和宽度可能会有所变化。

6. RXCTL (Receive Control)

- 作用:接收控制信号,用于指示接收数据的开始、结束等控制信息。

- 描述:RXCTL是接收数据的控制信号,通常用来指示接收数据帧的开始、结束,或者标识数据是否有效等。它帮助MAC确认数据接收的正确性,并对数据进行适当的处理。

7. MDC (Management Data Clock)

- 作用:管理数据时钟,用于控制与PHY的管理通信。

- 描述:MDC是用于管理接口(MII、RMII、SMII、GMII)中控制和数据通信的时钟信号。它通常由MAC产生,用来同步通过MDIO进行的读写操作。MDC的频率通常较低,通常是MDIO总线的时钟频率的1/10。

8. MDIO (Management Data Input/Output)

- 作用:管理数据输入/输出,用于通过MII、RMII等接口与PHY进行配置和状态读取。

- 描述:MDIO是与MDC一起使用的双向数据线,通常用于MAC与PHY之间的管理接口通信。通过MDIO,MAC可以读取PHY的状态、配置PHY寄存器或写入配置数据。MDIO支持多个操作模式(例如读、写),并允许设备之间进行数据传输。PHY的状态寄存器、自动协商、速度、全双工/半双工模式等通常通过MDIO进行管理。

总结:

这些信号共同工作,支持MAC与PHY之间的以太网数据传输。主要包括:

- 数据传输:TXDx和RXDx分别承担发送和接收数据的任务。

- 时钟同步:ETH_TXCK和RXCK提供数据传输和接收的同步时钟。

- 控制信号:TXCTL和RXCTL用于数据传输过程中的控制和状态指示。

- 管理接口:MDC和MDIO用于配置PHY、管理网络状态和控制参数(如自动协商、速率选择、全/半双工模式等)。

在设计和调试以太网外设时,理解这些信号的作用和时序要求是非常重要的,以确保网络通信的稳定性和数据的正确性。

2、供电设计

在以太网(Ethernet)外设芯片(如以太网PHY芯片)中,电源信号和其他输出信号都起到了至关重要的作用。这些信号涉及到电源供电、内部电压调节、LED指示灯、以及其他相关的功能。下面是你提到的几个常见电源信号及其作用:

1. ETH_AVDD

- 作用:AVDD是为以太网PHY的模拟电路提供电源。它通常用于为PHY芯片的模拟部分(如模拟接收和发送电路)供电。

- 电压:ETH_AVDD的电压通常为3.3V或2.5V,具体取决于PHY芯片的要求。有的芯片甚至有多个电压需求。

- 注意事项:

- AVDD电源的稳定性非常重要,因为它直接影响到PHY的模拟部分的性能,如接收信号的放大、滤波等。

- 确保AVDD电源干净、噪声低,通常会加入去耦合电容以减少电源噪声对信号的干扰。

2. DVDD

- 作用:DVDD是为以太网PHY的数字电路提供电源。它为PHY的数字部分(如MAC接口、控制逻辑、寄存器等)供电。

- 电压:DVDD的电压通常为1.8V、2.5V、3.3V等,具体取决于PHY芯片的设计要求。

- 注意事项:

- DVDD电压必须稳定,尤其是在高速数据传输时,不稳定的电压可能会影响PHY的数字信号处理和数据传输。

- 电源噪声的抑制对于数字部分也至关重要,因此需要确保DVDD的电源设计符合芯片的规格要求。

3. REG_OUT

- 作用:REG_OUT是由PHY芯片内部的LDO(低压差稳压器)或DC-DC转换器提供的电压输出。这个输出通常用于为其他电路或外部设备(如外部模块、外围电路等)提供稳定的电源。

- 电压:REG_OUT的电压值通常是PHY内部某个特定电压(如1.2V、1.8V等),以供给其他芯片或电路。

- 注意事项:

- REG_OUT电源输出的质量(如稳定性和噪声)直接影响到外部电路的稳定运行,特别是在高性能要求的应用中,电源输出需要非常稳定。

4. LED输出

- 作用:LED输出引脚用于驱动以太网PHY的状态指示灯(LED)。这些LED通常用于显示网络连接状态、传输速率、链路状态等信息。

- 常见LED指示灯功能:

- Link:表示网络连接状态(通常为绿灯表示已连接,灭灯表示未连接)。

- Activity:表示网络活动状态(如闪烁表示数据传输中)。

- Speed:表示网络速度(如不同颜色的LED指示不同的速率,10Mbps、100Mbps、1000Mbps)。

- 注意事项:

- LED引脚的电流通常通过电阻限制,确保LED不会因过流而损坏。

- LED信号的控制通常由PHY芯片内部的寄存器设置,具体的LED状态与网络的物理层连接和数据传输情况密切相关。

5. VDD_ANA (Analog Power Supply)

- 作用:VDD_ANA是为以太网PHY的模拟电路部分提供电源。该电源负责为PHY的模拟信号链路供电,确保其接收和发送数据的质量。

- 电压:通常是3.3V或2.5V,具体取决于芯片的要求。

- 注意事项:

- VDD_ANA的噪声可能会影响接收和发送的模拟信号,因此通常会加入去耦电容来减少噪声。

- 高质量的电源对于保证以太网PHY的信号处理精度和稳定性至关重要。

6. VDD_IO (I/O Power Supply)

- 作用:VDD_IO是为PHY芯片的I/O接口部分提供电源,主要用于连接MAC层或其他控制器的接口部分。

- 电压:通常为3.3V或1.8V,具体取决于PHY芯片的I/O标准。

- 注意事项:

- 确保VDD_IO电压稳定,因为它直接影响到PHY与外部设备(如MAC控制器或其他模块)之间的数据交换稳定性。

7. VDD_PHY (PHY Power Supply)

- 作用:VDD_PHY是为PHY芯片提供的主要电源,通常会分为数字部分(VDD)和模拟部分(VDD_ANA)。

- 电压:通常为3.3V、1.8V或2.5V。

- 注意事项:

- 需要稳定的电压,以确保PHY芯片的正常工作。电压不稳定可能会导致PHY无法正常接收和发送数据。

8. VSS (Ground)

- 作用:VSS是电源地(地线),为所有电源信号提供一个公共参考地电位。

- 注意事项:

- 电源地的设计必须考虑到系统噪声的影响,确保地线的良好连接,避免电源地噪声对信号传输的干扰。

9. VDD_EXT (External Power Supply)

- 作用:VDD_EXT通常用于外部扩展设备(如外部网络芯片、光模块等)的供电,支持PHY芯片的扩展功能。

- 电压:具体电压依赖于外部设备的需求。

- 注意事项:

- 需要确保VDD_EXT的电源质量,避免影响外部扩展设备的正常运行。

总结:

这些电源和信号分别为以太网PHY芯片的不同部分提供电力和控制。正确理解它们的作用和稳定性要求对于设计可靠的以太网系统至关重要。电源的稳定性和去耦设计、LED指示灯的正确配置、以及适当的电源管理(如REG_OUT的使用)都会影响到最终以太网通信的稳定性、性能和可调试性。在设计时,要根据芯片的具体要求来布置电源线路,并确保所有电源信号的稳定供应。

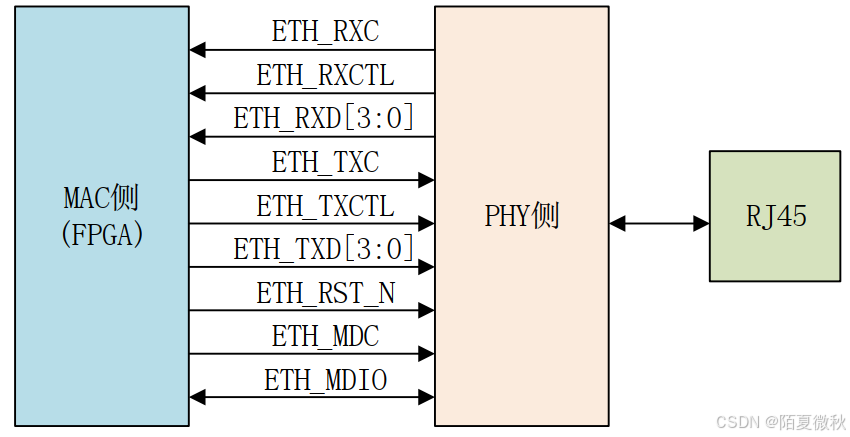

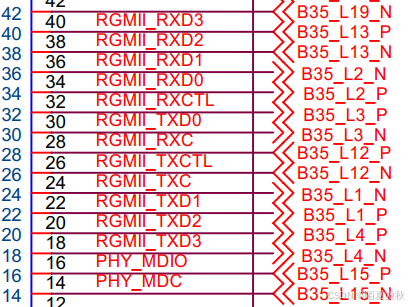

二、PL以太网

- ETH_RXC:接收数据参考时钟, 1000Mbps 速率下,时钟频率为 125MHz,时钟为上下沿同时采样; 100Mbps 速率下,时钟频率为 25MHz; 10Mbps 速率下,时钟频率为 2.5MHz, ETH_RXC 由 PHY 侧提供。

- ETH_RXCTL(ETH_RX_DV):接收数据控制信号。ETH_RXD:四位并行的接收数据线。

- ETH_TXC:发送参考时钟, 1000Mbps 速率下,时钟频率为 125MHz,时钟为上下沿同时采样; 100Mbps速率下,时钟频率为 25MHz; 10Mbps 速率下,时钟频率为 2.5MHz, ETH_TXC 由 MAC 侧提供。

- ETH_TXCTL(ETH_TXEN):发送数据控制信号。ETH_TXD:四位并行的发送数据线。

- ETH_RESET_N:芯片复位信号,低电平有效。

- ETH_MDC:数据管理时钟(Management Data Clock),该引脚对 ETH_MDIO 信号提供了一个同步的时钟。

- ETH_MDIO:数据输入/输出管理(Management Data Input/Output),该引脚提供了一个双向信号用于传递管理信息。

PL读写以太网,是属是比较复杂,时序完全手搓,如果时延等要求不高的场合,一般还是推荐PS做以太网+DDR,PL写DDR,PS读DDR并进行回传。