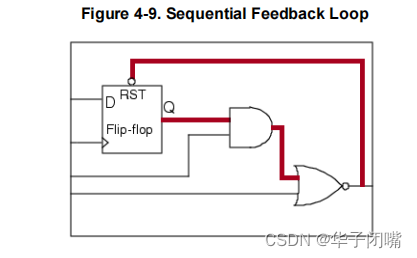

处理方式 如下:虽然ATPG工具可能会因顺序循环而损失一些测试覆盖率,但这些循环不会像组合循环那样给工具带来广泛的问题。就其本质而言,ATPG tool使用“非扫描单元的ATPG处理”中描述的模拟基元,对设计中的非扫描顺序元素重新建模。插入这些基元后,以某种方式自动打断循环。(改变就会自动的打断)

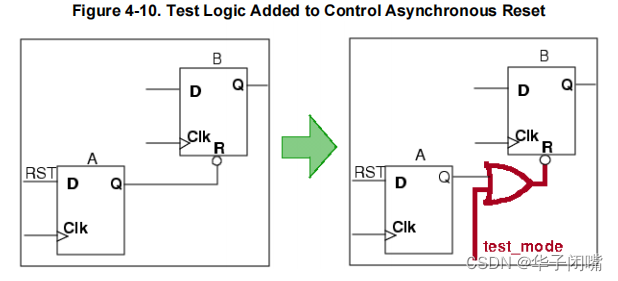

在本例中,Tessent Scan添加了一个OR门,它使用test_mode(而不是Scan_enable)信号在测试过程中保持触发器B的复位处于非活动状态。然后将test_mode信号限制为1,这样触发器B在测试期间就永远不会复位。要插入这种类型的测试逻辑,可以使用Tessent Scan命令set_test_logic 。

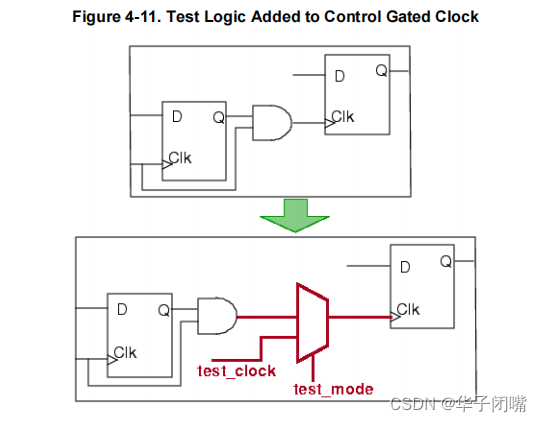

在本例中,Tessent Scan通过为扫描加载/卸载和数据捕获添加测试时钟,并将其与原始时钟信号多路复用,使元素可扫描。它还添加了一个名为test_mode的信号来控制添加的多路复用器。test_mode信号不同于scan_mode或scan_enable信号,因为它在整个测试期间处于活动状态,而不仅仅是在扫描链加载/卸载期间。

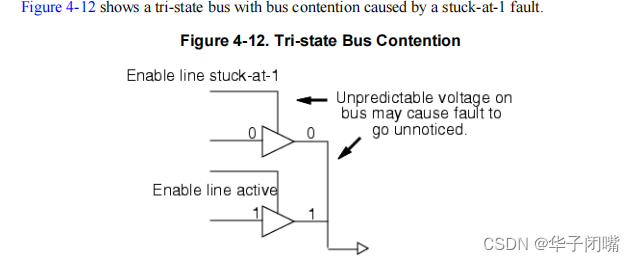

Tessent Scan可以添加选通逻辑,在扫描链移动期间关闭三态设备。该工具用scan_enable信号将三态设备启用线选通,使其处于非活动状态,从而防止扫描数据移位期间的总线争用。要插入这种类型的选通逻辑,可以使用Tessent Scan命令set_tristate_gating 此外,ATPG工具允许您指定总线争用对三态网络的故障影响。这种能力提高了三态驱动器使能线的可测试性。

Non-Scan Cell Handling

在规则检查和学习分析过程中,ATPG工具学习不属于扫描电路的所有状态元素的行为。此学习涉及扫描加载操作后非扫描元素的行为。作为学习分析的结果,ATPG工具对每个非扫描单元进行分类。

•TIEX-在这一类别中,ATPG工具认为触发器或锁存器的输出在测试期间始终为X值。

•TIE0-在这一类别中,ATPG工具认为触发器或锁存器的输出在测试期间始终为0值。

•TIE1-在这一类别中,ATPG工具认为触发器或锁存器的输出在测试期间始终为1值。

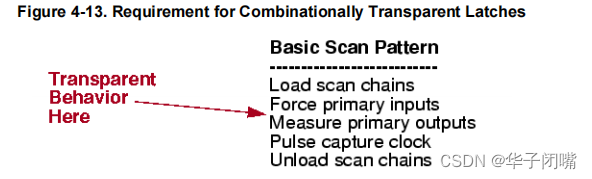

•Transparent (combinational) -在此类别中,非扫描单元是一个锁存器,锁存器的行为透明。当其行为透明时,它实际上作为将数据输入值传递给数据输出的缓冲区。TLA模拟门对此行为建模。图4-13显示了闩锁必须透明的点行为

如果锁存器的时钟输入在主输入力和主输出测量之间的时间段内处于非活动状态,则会出现透明度。如果锁存器设置为行为透明,则不应该遇到任何重大故障检测问题(时钟、设置和重置线路上的故障除外)。然而,只有在有限的案例中,非扫描cell的行为确实透明。对于认为锁存器透明的工具,必须满足以下条件:

o锁存器不得产生潜在反馈路径,除非路径被扫描单元或非扫描单元(透明锁除外)破坏。

o锁存器必须具有传播到可观察点的路径。

o当所有时钟关闭时,锁存器必须能够将数据值传递给输出。

o锁存器必须具有时钟、设置和重置信号,这些信号可以设置为确定的值

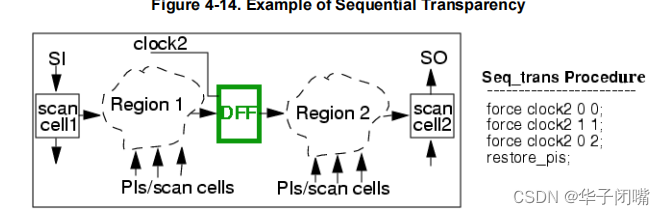

•Sequential transparent-扩展了透明的概念,将非扫描元素包括在内,这些元素可以被强制同时透明出现自然透明度的点。在这种情况下,非扫描元件可以是触发器、锁存器或RAM读取端口透明,如果给定一系列事件,它可以捕获一个值并将该值传递给其输出,而不会干扰关键扫描单元。非扫描单元格的顺序透明处理允许您描述将非扫描单元格置于透明模式的事件。为此可以在测试过程文件中指定一个名为seq_transparent的过程。此过程包含创建非扫描单元透明行为所需的事件。在工具加载扫描链、强制主要输入并强制关闭所有时钟后,seq_transparent程序脉冲所有非扫描单元的时钟或执行其他指定事件,以“透明”地通过单元传递数据

图4-14所示的DFF在工具脉冲时钟输入clock2时的顺序透明。顺序透明过程显示启用透明行为的事件。与透明处理相比,顺序透明处理的优点包括更灵活的使用,以及使用此技术创建“结构化部分”的能力扫描”(以最小化区域开销,同时仍然获得可预测的高测试覆盖率)。此外,顺序透明的概念支持使用称为透明从属的单元的设计实践。透明从属是使用从属的非扫描锁存时钟来捕获数据。此外,可以在测试过程文件中定义和使用多达32个不同的、唯一命名的seq_transparent过程来处理设计中的各种类型的非扫描单元电路。规则检查通过这些程序确定非扫描单元是否符合顺序透明性。具体来说,单元格必须满足规则P5、P6、P41、P44、P45、P46、D3和D9。有关这些规则的更多信息,请参阅《Tessent Shell参考手册》中的“设计规则检查”。时钟规则检查将顺序透明元素视为扫描单元。

存在的限制包括:

o检测AC缺陷的能力受损(过渡故障类型导致连续透明元件显示为tie-X门)。

o如果没有条件声明,无法使扫描单元按顺序计时的非扫描单元透明。

o如果应用顺序透明程序干扰扫描单元(seq_transparent程序期间扫描单元的内容发生变化),则顺序透明程序的可用性有限。

o非扫描单元的反馈路径,除非被扫描单元打断,否则无法将非扫描单元视为顺序透明。

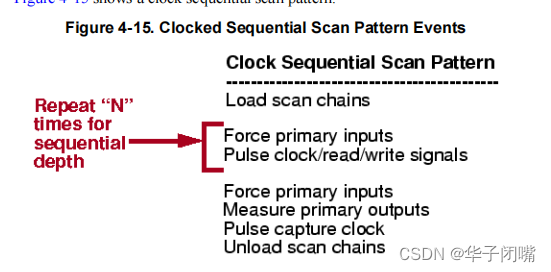

•Clock sequential-如果非扫描单元遵守标准扫描时钟规则,即如果单元在所有时钟关闭的情况下保持其值,则工具将其视为时钟顺序单元。在这种情况下,在工具加载扫描链后,它强制主输入并多次脉冲时钟/写入/读取线(基于非扫描的顺序深度单元格)设置测试条件。随后是一个正常的观察周期。图4-15显示了时钟顺序扫描模式。

这种重复主输入和时钟脉冲的技术允许工具跟踪扫描单元和反馈路径内的新值。当DRC执行扫描单元检查时,它也会检查非扫描单元。检查过程完成后,规则检查器会发出一条消息,指示符合时钟顺序处理条件的非扫描单元的数量。通过选择set_pattern_type命令的-sequential选项,可以指示该工具使用时钟顺序处理。在测试生成过程中,该工具首先尝试组合,然后尝试RAM顺序技术,为目标故障生成测试模式。如果使用这些技术失败,如果指定非零顺序,该工具将执行时钟顺序测试生成。

o最大允许连续深度为255(典型深度范围为2至5)。

o复制和阴影单元格不能按顺序操作。

o该工具无法检测时钟/设置/重置线路上的故障。

o不能使用时钟顺序模式的只读RAM测试模式

o该工具模拟在后续时钟边缘捕获数据的单元格(当数据更改时在前缘)使用数据输入上的原始值。

o加载_卸载模拟后保持恒定值的非扫描单元是被视为锁存器。

o此类测试具有较高的内存和性能成本。

Clock Dividers

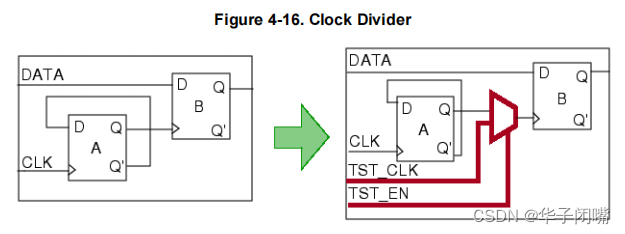

一些设计包含不可控时钟电路;也就是说,可以对触发器进行时钟、设置或重置的内部生成信号。如果这些信号仍然无法控制,Tessent Scan将不会考虑这些信号控制的顺序元素“可扫描”。因此,它们可能会在扫描移位期间干扰序列元素。下图显示了由时钟分频器信号驱动的序列元件(B)的示例,并添加了适当的电路来控制分割的时钟信号。

Tessent Scan可以在必要时在这些节点插入称为测试逻辑的特殊电路,从而帮助您修改电路以实现最大可控性(从而实现序列元素的最大可扫描性)。Tessent Scan通常使用芯片级测试引脚对不可控电路进行选通。在时钟不可控的情况下,Tessent Scan会添加一个由test_clk和test_en信号控制的MUX。

Pulse Generators

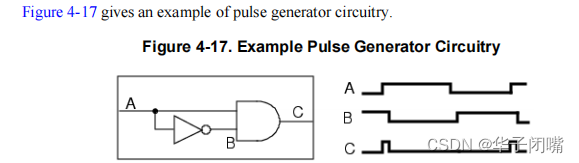

脉冲发生器是一种在激活时在输出端产生脉冲的电路。

当设计者在时钟路径中使用该电路时,无法创建稳定的导通状态。如果没有稳定的开启状态,故障模拟器和测试生成器就无法将数据捕获到扫描单元中。脉冲发生器也可用于写控制电路,这种用途会阻碍RAM测试。默认情况下,ATPG工具会在学习过程中识别再转换脉冲发生器接收器(PGS)门,或简称为“脉冲发生器”。对于提供支持的工具,“脉冲发生器”必须满足以下要求:

•“脉冲发生器”门必须与存储器元件的时钟输入或RAM的写入线连接(图4-17中的C处)。

•“脉冲发生器”门必须是AND、NAND、OR或NOR门。

•“脉冲发生器”门的两个输入必须来自一个再转换source gate。

•两条重覆盖路径只能包含逆变器和缓冲器。

•两个再覆盖路径中必须存在反转差异。

•两条路径必须具有不同的长度(传播时间)。

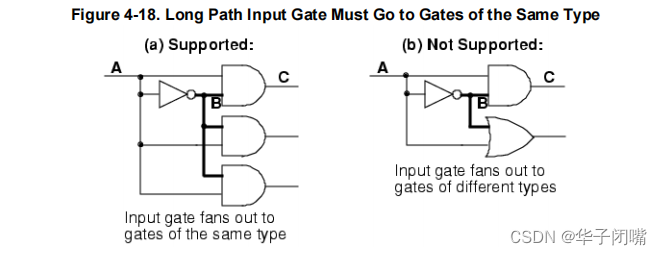

•在长路径中,连接到“脉冲发生器”输入端的逆变器或缓冲器只能进入图4-18(a)所示的相同门类型的门。fanout to gate不支持图中(b)所示的不同类型。工具将此输入门建模为与“脉冲发生器”门的非控制值相关联(TIE1用于AND和NAND门,TIE0用于OR和NOR门)。