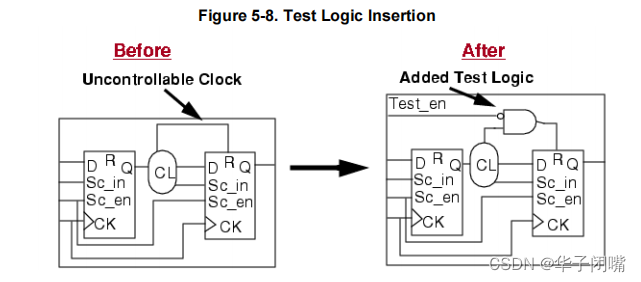

可以使用set_test_logic指定要插入测试逻辑的信号,在扫描插入过程中向所有不可控(设置、重置、时钟或RAM写入控制)信号添加测试逻辑。默认情况下,Tessent Scan不添加测试逻辑,但是可以使用此命令显式启用测试逻辑。在添加测试逻辑电路时,该工具执行一些基本优化,以减少所需的测试逻辑总量。

Setup for Wrapper Chain Identification

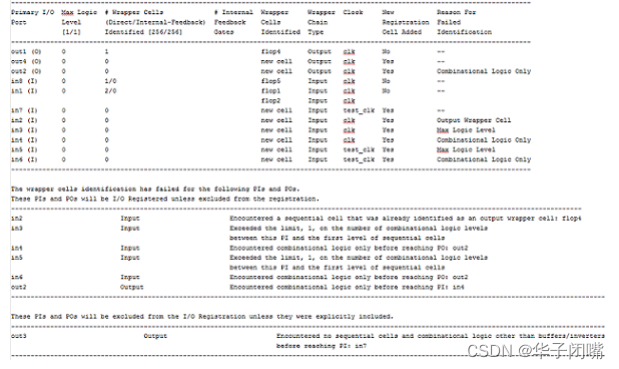

Tessent Scan通过降低设计子模块内部核心扫描链的可见性,提供了提高分层设计性能和测试覆盖率的能力。在顶层测试子模块的唯一要求是逻辑输入必须使用扫描链可以控制(即必须由寄存器驱动),逻辑输出必须通过扫描链可见(即必须注册)。使用包装扫描链可以满足这些要求,包装扫描链是子模块外围的扫描链,连接到待测试子模块的每个输入和输出(用户定义的时钟、扫描相关I/O引脚和用户排除的引脚除外)。包含可从子模块输入端到达的包装单元的包装链被视为输入类型包装链和包含从子模块的输出可到达的包装单元的包装链被视为输出型包装链。输入和输出包装链用于在INTEST和EXTEST期间提供分层设计的适当测试覆盖模式。在INTEST模式下,子模块的所有输入都可以使用输入包装扫描链进行控制,所有输出都可以通过输出包装扫描链观察到。这提供了为子模块独立生成一整套ATPG模式的能力。在EXTEST模式下,子模块的所有输出都可以使用输出包装扫描链进行控制,所有输入都可以通过输入包装扫描链观察到。这提供了在顶层测试/优化子模块逻辑的能力,而不需要子模块的内部可见性(即不需要核心扫描链)。

•使用set_wrapper_analysis_options和analyze_wrappers_cells将包含包装扫描链的扫描单元标识为输入和输出包装单元命令和使用insert_test_logic命令缝合到单独的输入和输出包装链中。

o当有analyze_wrapper_cells命令时,Tessent Scan执行包装单元分析并识别输入和输出包装单元,这将缝合到单独的输入和输出包装链中。

o如果未发出set_wrapper_chains命令,analyze_wrappers_cells命令将执行默认包装单元标识,类似于发出不带参数的set_wrpper_chains命令。

o如果analyze_wrapper_cells命令与set_dedicated_wrappers_cell_options命令一起发出,则添加到主输入的专用包装单元将缝合到相应的输入包装链中,而添加到主输出的专用包装单元将缝合到适当的输出包装链中。

•当发出set_dedicated_wrapper_cell_options命令而未发出analyze_wrappers_cells命令时,添加到主I/O的专用包装单元被视为Core单元,并被缝合到相应的Core扫描链中。

o当发出insert_test_logic命令时,通常会分析专用包装单元并将其插入扫描链。

o为了向后兼容,当发出set_dedicated_wrapper_cell_options命令时,report_wrappers_cells命令将触发专用的包装单元分析,但analyze_wrappper_cells需求并没有。

•如果在set_wrapper_chains命令之后发出insert_test_logic命令,但尚未发出analyze_wrappers_cells命令,则会收到一条错误消息,说明在插入之前需要进行包装链分析。

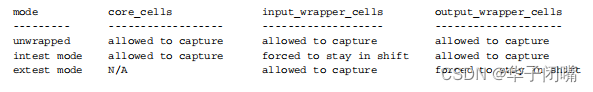

此外,在内部测试(intest模式)期间,输入包装单元将核心与主要输入完全隔离,输出包装单元提供核心内部节点的可观察性。识别为输入包装单元的扫描单元的扫描启用连接将与intest启用信号相结合,以防止这些单元在intest期间捕获来自主输入的任何值。标识为输出包装单元的扫描单元的scan_enable连接将与extest启用信号相结合,以防止这些单元在extest模式下捕获数据。每个模式下的行为如下所示:

以下段落提供了包装器分析算法的高级描述,以便更好地理解工具何时将选择使用专用包装器单元而不是共享包装器单元作为主要输入和主要输出。该工具首先从主输出引脚反向trace。如果在此回溯跟踪期间遇到的扫描单元数超过特定阈值,则会插入专用的包装单元。此外,在外部测试期间,输出包装单元的设置和复位引脚必须可控。这意味着该工具需要从潜在共享输出包装单元的设置和重置端口追溯,以查看是否还有可能影响这些端口的扫描单元,并将其视为额外的输出包装单元。如果组合连接的扫描单元数量加上设置和重置端口反馈路径中的扫描单元超过某个阈值,则将再次插入专用包装单元。最后,对每个主要输入进行类似的分析。如果特定主输入达到的扫描单元数超过用户指定的阈值,则使用专用输入包装单元。对于输入包装单元,工具必须在扫描单元的所有端口具有已知值。这意味着除了设置和重置端口外,它还必须从时钟和数据端口追溯,以查找也必须成为包装单元的任何扫描单元。如果组合连接的扫描单元的数量,以及反馈路径中的扫描单元数量包括设置、重置和时钟线超过用户指定的阈值,然后将插入专用的包装单元。请注意,在extest期间,反馈路径中的单元必须保持完全可控,并且它们很可能从非包装(核心)扫描单元捕获值。这意味着该工具必须将这些单元格标记为输出包装单元格,以便将它们连接到内部生成的扫描启用信号,该信号在捕获期间保持高电平。发生的所有跟踪都基于通过未阻塞路径的跟踪。这意味着pin约束可能会对该分析产生巨大影响。例如,如果输出包装单元的设置或重置端口由于pin约束而保持常数0,则不进行反向跟踪。

除了超过阈值之外,还有其他几种情况可以触发插入专用包装单元。其中包括:

•识别的顺序单元是现有扫描链的一部分。

•在I/O的包装单元标识期间遇到“黑匣子”。

•在I/O的包装单元识别期间,没有识别出顺序单元。(注意:对于直通连接,不插入包装单元)。

•当前标识的顺序单元已标识为与当前I/O方向相反的I/O的包装单元。

set_dedicated_wrapper_cell_options命令可用于指定用于专用包装单元的库模型(默认值除外),并提供有关应向专用包装单元注册哪些I/O的附加信息set_dedicated_wrapper_cell_options命令的“on-ports list”中指定的I/O将自动注册到专用包装单元,而当“关闭端口列表”中指定的I/O无法识别共享包装单元时,它们将被排除在专用包装单元的自动注册之外(在这种情况下,失败的I/O既不会被共享包装单元识别,也不会被专用包装单元注册包装单元)。

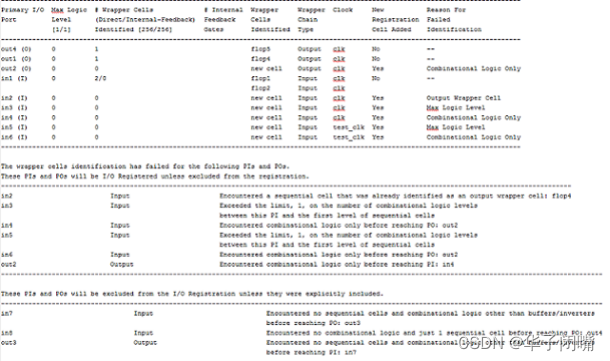

ex2:pin in2/3不包括在自动注册范围内

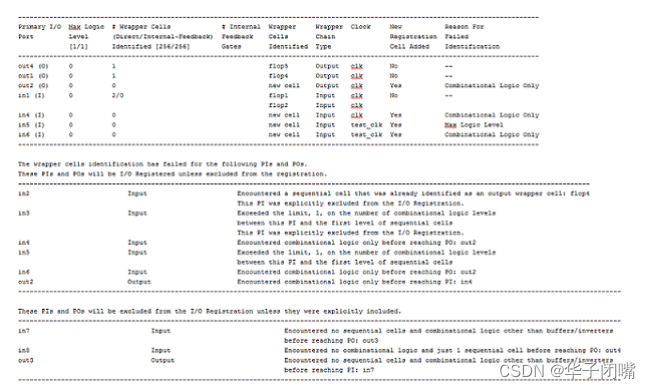

example 3:pin in7和out4指定被注册

Clock Selection for Dedicated Wrapper Cells

如果没有明确指定专用包装单元的时钟,该工具首先会根据控制入和/或出中触发器的最上级时钟选择适当的时钟域。在时钟域选择期间,工具将忽略任何既不是现有扫描单元,也不是扫描插入目标的触发器。此外,初始搜索将限于与测试点位置位于同一power_domain_island中的触发器。当在出或入中仅找到单个时钟域时,将使用该域。否则,将使用控制点fanout(或观察点fanin)中引用最多的时钟域。接下来,它选择一个连接点,如下所述:

•它连接到扇出(对于输入包装单元)或扇入(对于输出包装单元)中一个触发器的时钟端口。如果连接的扫描单元的时钟端口无法直接访问,则它将通过时钟网络中的敏感路径进行跟踪,以找到最接近的可能连接点。

•如果如上所述找不到有效的连接点,它会尝试连接到层次结构上最近的模块输入端口处的识别时钟。

•否则,它会连接到时钟源。

How to Mask Output Partition Pins

输出分区管脚是块输出管脚,无法从芯片级主输出直接观察到。输出分区引脚是那些进入块B和块C的输出。因为这些是不可见的输出,所以必须使用add_output_masks命令屏蔽它们。为了确保在测试其他分区期间屏蔽的主输出驱动非活动值,可以指定主输出在测试模式期间保持0或1值。称为输出保持0或输出保持1包装单元的特殊单元用于此目的。默认情况下,该工具使用常规输出包装单元。

Child OCC Schematic

child occ是三种occ类型之一。它用于时钟斩波控制。它还通过创建时钟门启用信号而不是单个时钟门来提供时钟门控。它使布局工具能够根据需要在布局期间复制时钟网关。当scan_en较高时,子OCC允许时钟通过。当scan_en较低时,它允许一组可编程的恒定时钟脉冲通过。父OCC通常为子OCC的时钟输入供电。显示了child occ控制系统的两个示意图。一个有时钟网关,另一个没有。图5-9显示了带有时钟网关的子片上控制器。