OpenOCD是一个开源的Debug Translator,它负责将GDB的调试命令(与CPU Architecture无关)翻译为操作芯片Debug Module的硬件指令。OpenOCD源代码的src/target目录包含了与CPU architecture相关的源代码。

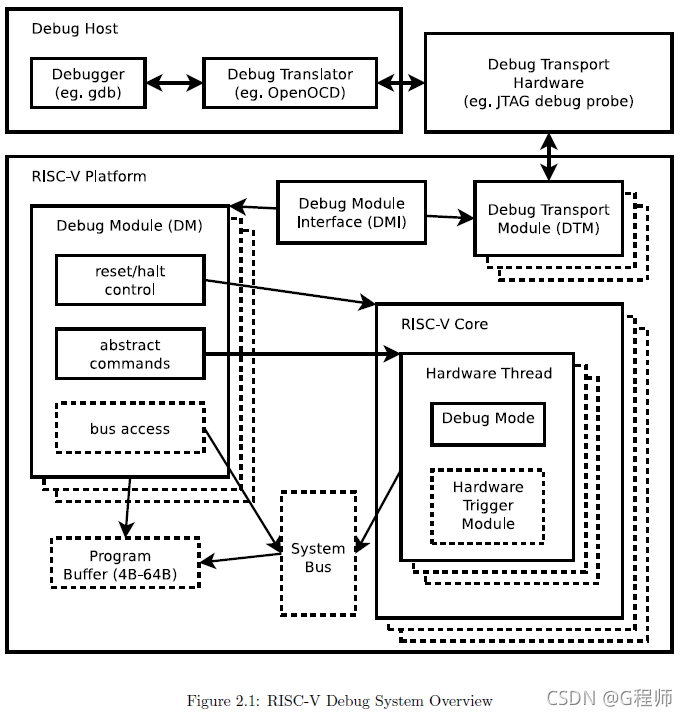

下图中,

- Debug Host采用了开源的 GDB + OpenOCD,也可以是其他的软件,比如Segger的J-Link Commander。

- Debug Transport就是JTAG在线调试(仿真)器,比如J-Link Probe。RISC-V规定采用JTAG作为Debug Transport Module,详见文档《risc-v debug release》的6.1节 JTAG Debug Transport Module和文档《RISC-V SweRV™ EL2 Programmer's Reference Manual》的9.1.1节 Control/Status Registers in JTAG Address Space。

在github上有三个不同的OpenOCD项目

另外,还有以下两个OpenOCD binary distribution

xPack OpenOCD GitHub - xpack-dev-tools/openocd-xpack: A binary xPack with OpenOCD![]() https://github.com/xpack-dev-tools/openocd-xpack

https://github.com/xpack-dev-tools/openocd-xpack

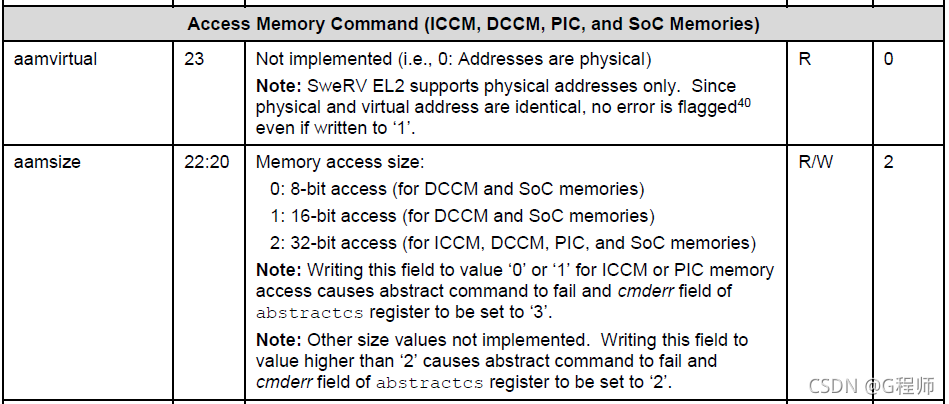

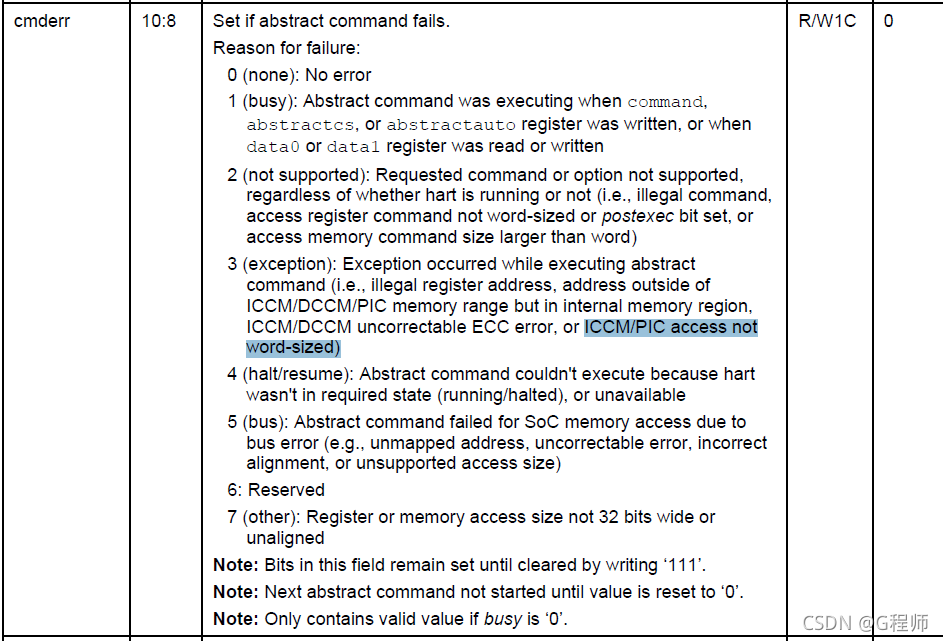

只有SweRV OpenOCD支持SweRV调试。RISC-V平台的Debug Module支持通过Abstract Command访问ICCM,但是SweRV存在以下Memory access size限制。

由于ICCM只能以32-bit长度被Debug Module访问,所以如果要把指定地址上的原16 bit指令替换成16 bit指令c.ebreak(即设置Software breakpoint),会产生如下错误

SweRV OpenOCD针对SweRV的这个限制,提供了workaround,详见SweRV OpenOCD的README。

如果要使用RISC-V OpenOCD,也可以采用关闭16 bit compressed instruction的方式来规避这个限制,即 从gcc的-march参数中去掉‘c’,比如将'-march=rv32imc'改为'-march=rv32im',从而保证不会生成16 bit compressed instruction。但是,这会带来code size增加的问题。

另外,Codasip公司还提供了Core SweRV Support Package(SSP)帮助实现基于SweRV-based SoC设计 GitHub - chipsalliance/Cores-SweRV-Support-Package: Processor support packages![]() https://github.com/chipsalliance/Cores-SweRV-Support-Package

https://github.com/chipsalliance/Cores-SweRV-Support-Package

Western Digital为SweRV系列还提供一个FuseSoC-based参考平台项目 SweRVolf https://github.com/chipsalliance/Cores-SweRVolf![]() https://github.com/chipsalliance/Cores-SweRVolf

https://github.com/chipsalliance/Cores-SweRVolf