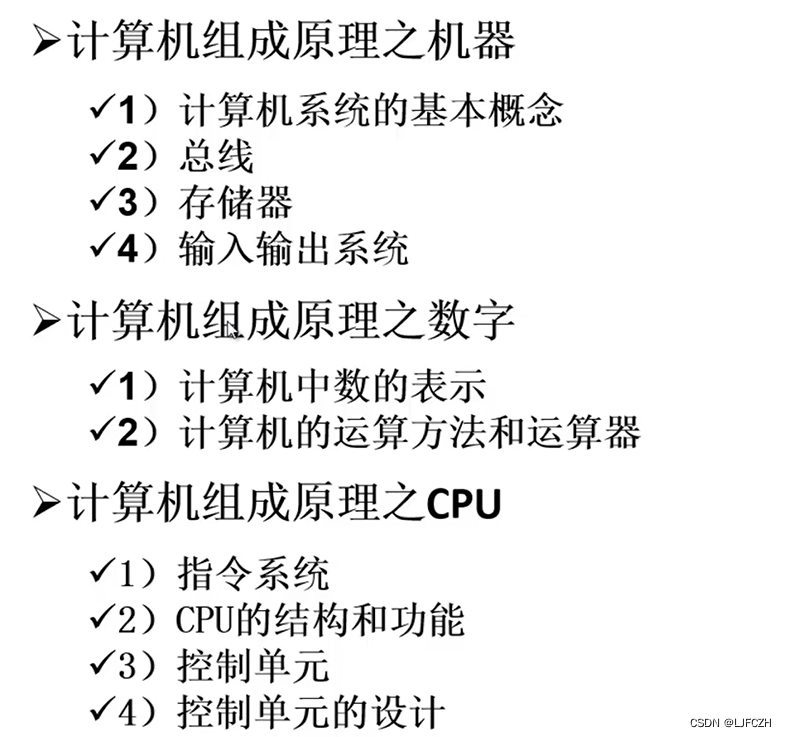

存储器

概述

1. 分类

(1)按存储介质分:

- 半导体存储器:一般用作主存;断电容易丢失(有的不易丢失)

- 磁存储器

- 磁表面存储器:用作辅存;不易丢失

- 磁芯存储器

- 光盘存储器

(2)按存取方式:

- 随机访问:存取时间和物理地址无关

- 随机存储器:程序执行过程中可读可写

- 只读存储器:程序执行过程中只读

- 串行访问:存取时间和物理地址有关

- 顺序存取存储器:磁带

- 直接存取存储器:磁盘

(3)按作用分:

- 主存

- RAM

- 静态RAM

- 动态RAM

- ROM

- MROM

- PROM

- EPROM

- EEPROM

- RAM

- 闪存(Flash Memory)

- 缓存(Cache)

- 辅存(磁盘、磁带、光盘)

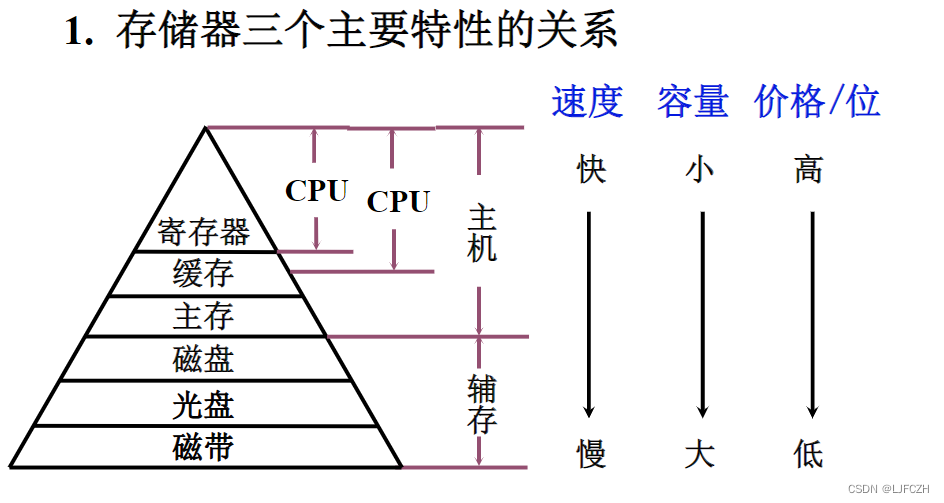

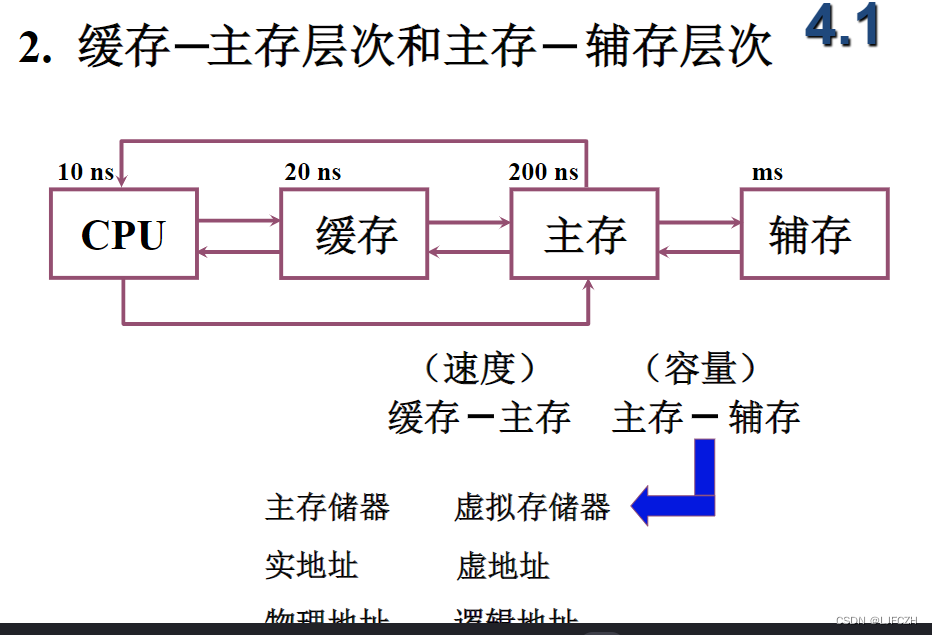

2. 存储器的层次结构

CPU中的存储器是寄存器,速度很快、容量小,做运算时存储数据

缓存解决CPU与主存速度差异,有一部分在CPU中,还有一部分在CPU外面

- 主存——辅存层次解决容量问题,软硬件结合实现,被称为虚拟存储器,使用虚地址,是逻辑地址

- 缓存——主存层次解决速度问题,由硬件实现,对使用人员透明,称为主存储器,使用实地址,是物理地址

主存储器

1. 概述

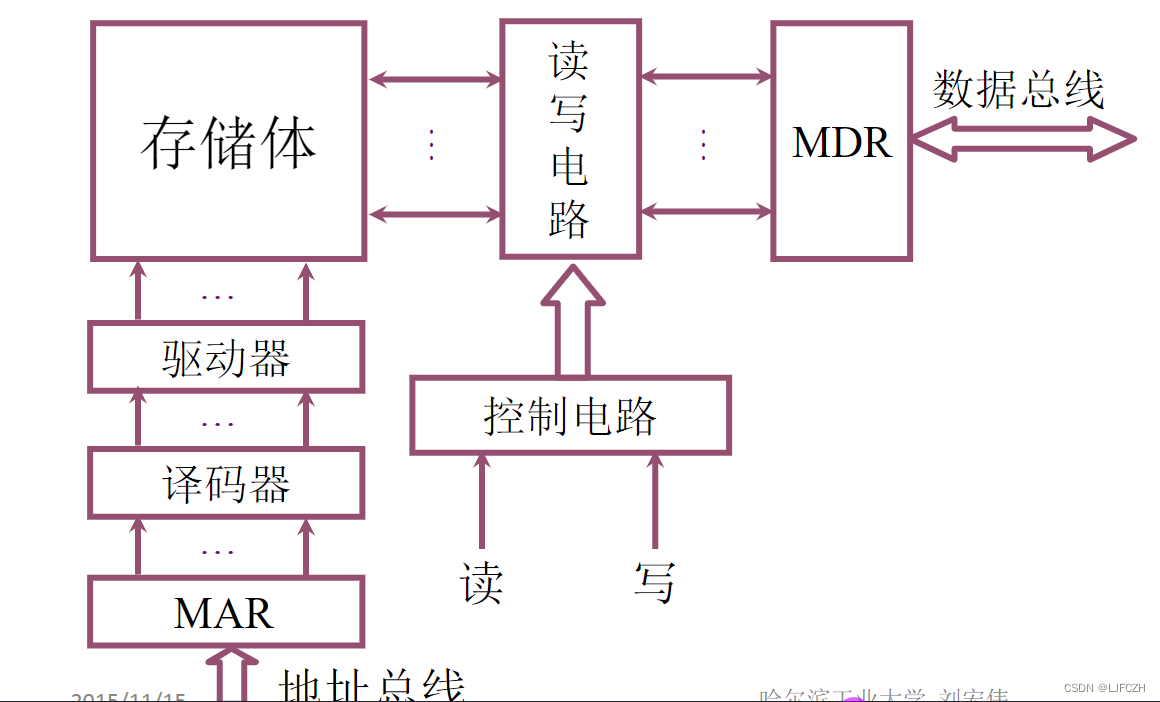

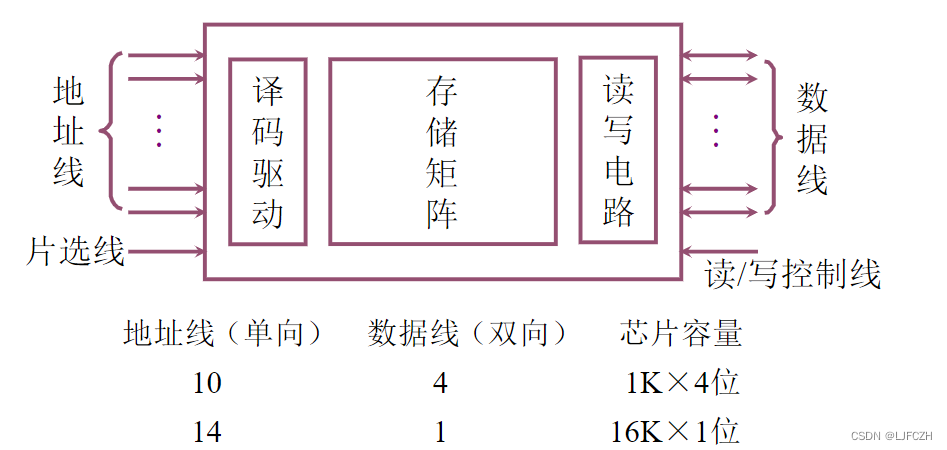

- 主存结构:除了存储体、MAR、MDR之外,还有译码器、读写电路、控制电路

译码器将传来的地址转换为存储体中对应的地址

控制电路来控制读写电路是读操作还是写操作

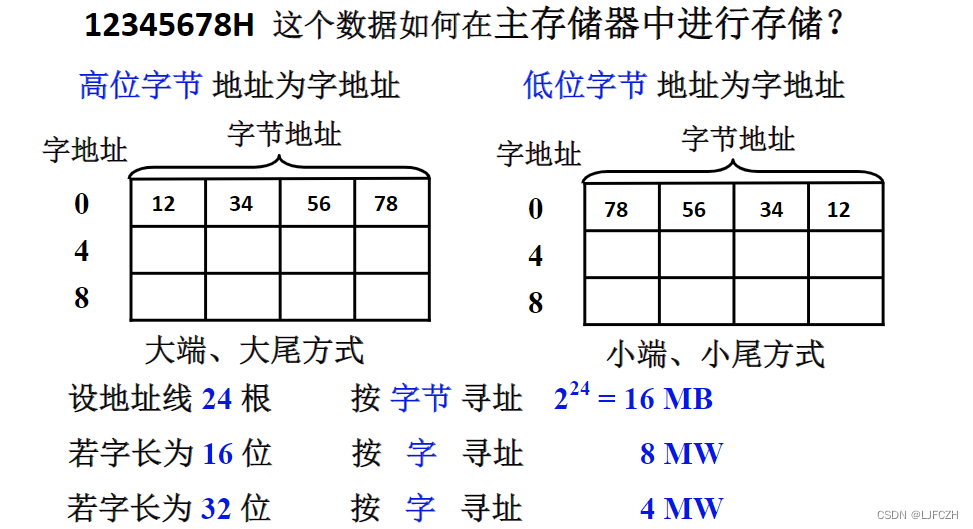

- 主存中的存储单元的地址的分配

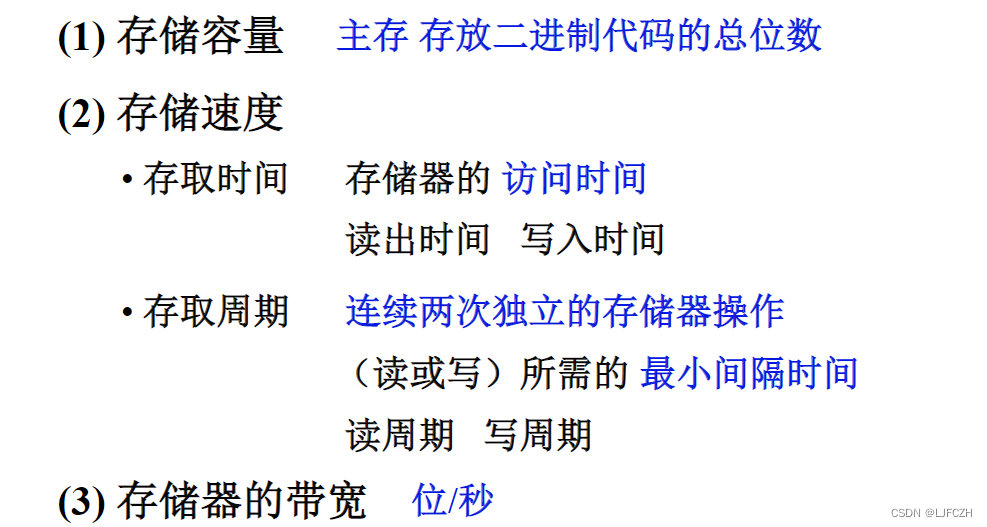

- 主存的技术指标

存取周期 > 存取时间

2. 半导体存储芯片

- 半导体存储芯片的基本结构

- 主存中的MAR、MDR一般集成到CPU中

- 地址线连着译码器,还有片选线用来选择当前传来的地址对应着存储体中哪一组芯片

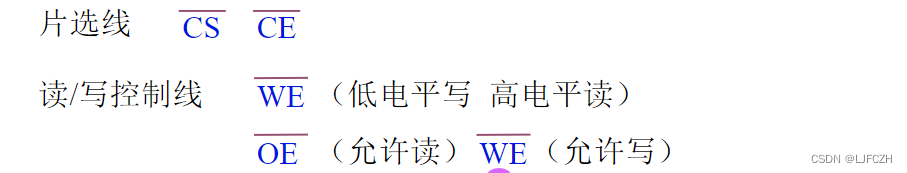

片选线CS或CE,当它为低电平时有效

读写控制线一根WE,低电平为写,也可以两根OE和WE

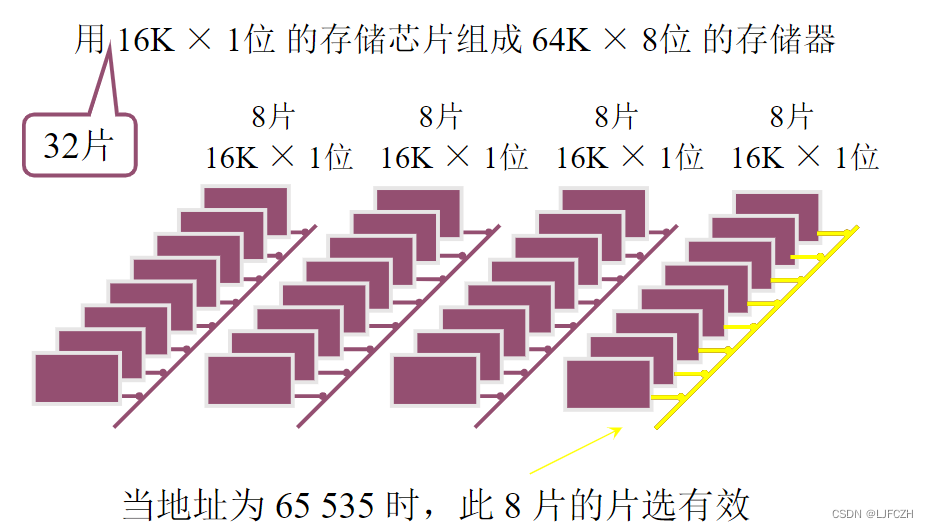

片选线:每8个存储芯片为一组,共有4组,每一组连接着片选线

第一组地址范围:0~16K-1…地址65536传来时,它对应着第四组芯片,所有第四组芯片的片选信号为低电平,可以同时选中第四组芯片

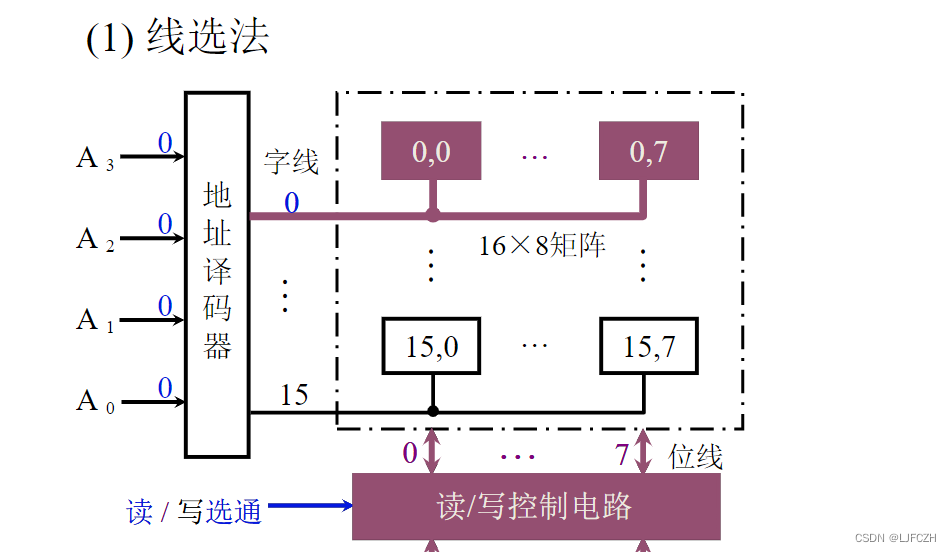

- 译码方式

- 地址线都为0时,译码之后对应的第0个线的芯片被选中;为01时,译码之后就是第1个线

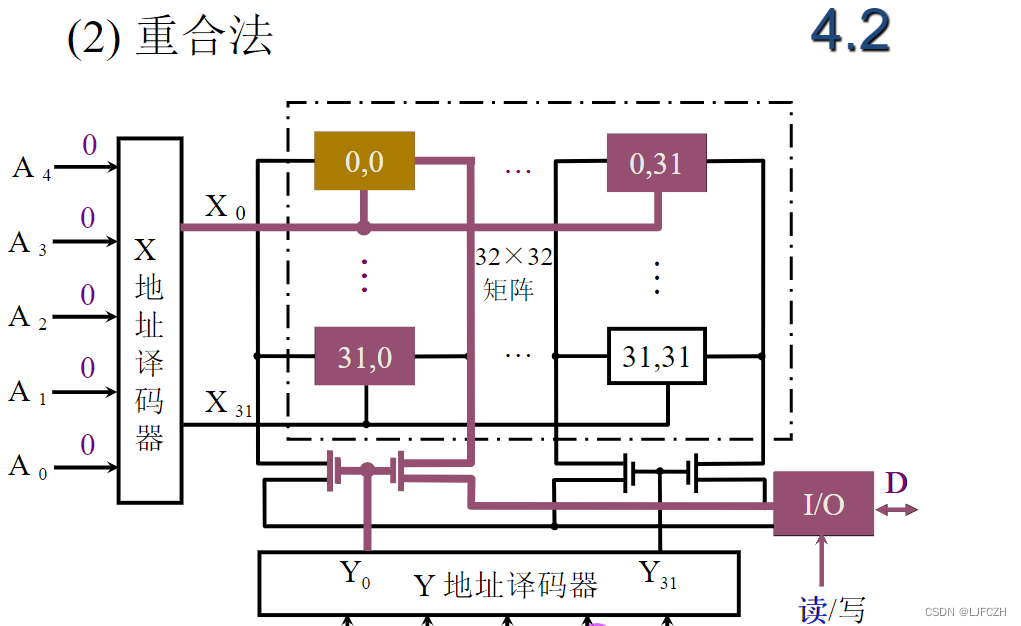

- 但是16太少了,当线数量很大时,1M*8就是1M根线,太密集,于是有了重合法

采用行地址和列地址分别译码,两个方向同时选中的信号会被输出

3. RAM

- 静态RAM(SRAM)

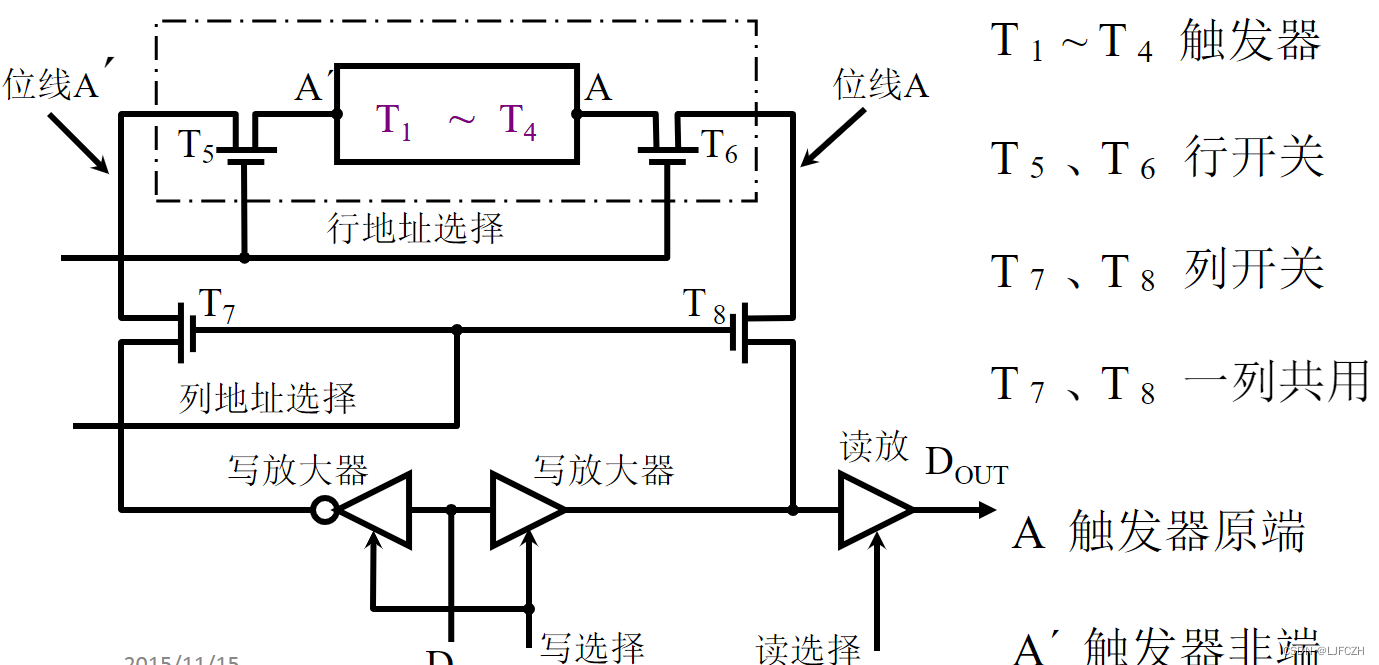

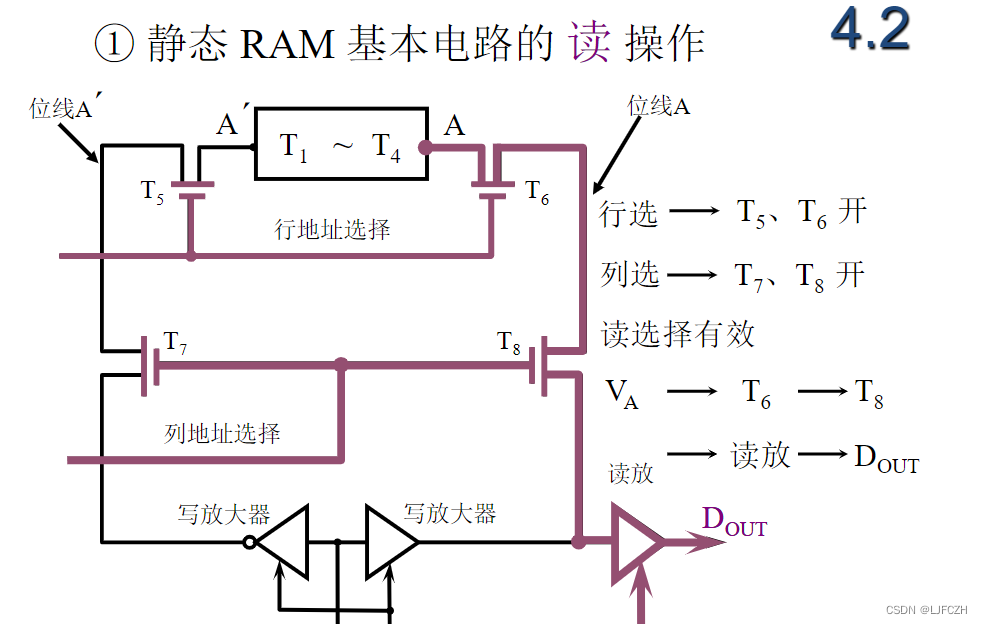

SRAM基本电路

- 保存0、1的原理:虚线框中的晶体管T1~T4构成一个触发器,触发器两个状态表示0和1,触发器的原端A保存这个存储元的数据(0或者1),它的非端A撇保存相反的数据。

- 触发器两端各有一个行开关,选中这一行的芯片时,每个元件的行开关都会打开,数据从原端经过T6开关到达位线再到T8开关,在到达数据线完成读操作。T5开关也是打开的,但是T5到T7后经过左边的写放大器会被拦截,所以非端数据不会输送出去。

- T7、T8是列开关,是一列元件共享的,列地址选中某一列时,这一列的两个列开关就会打开

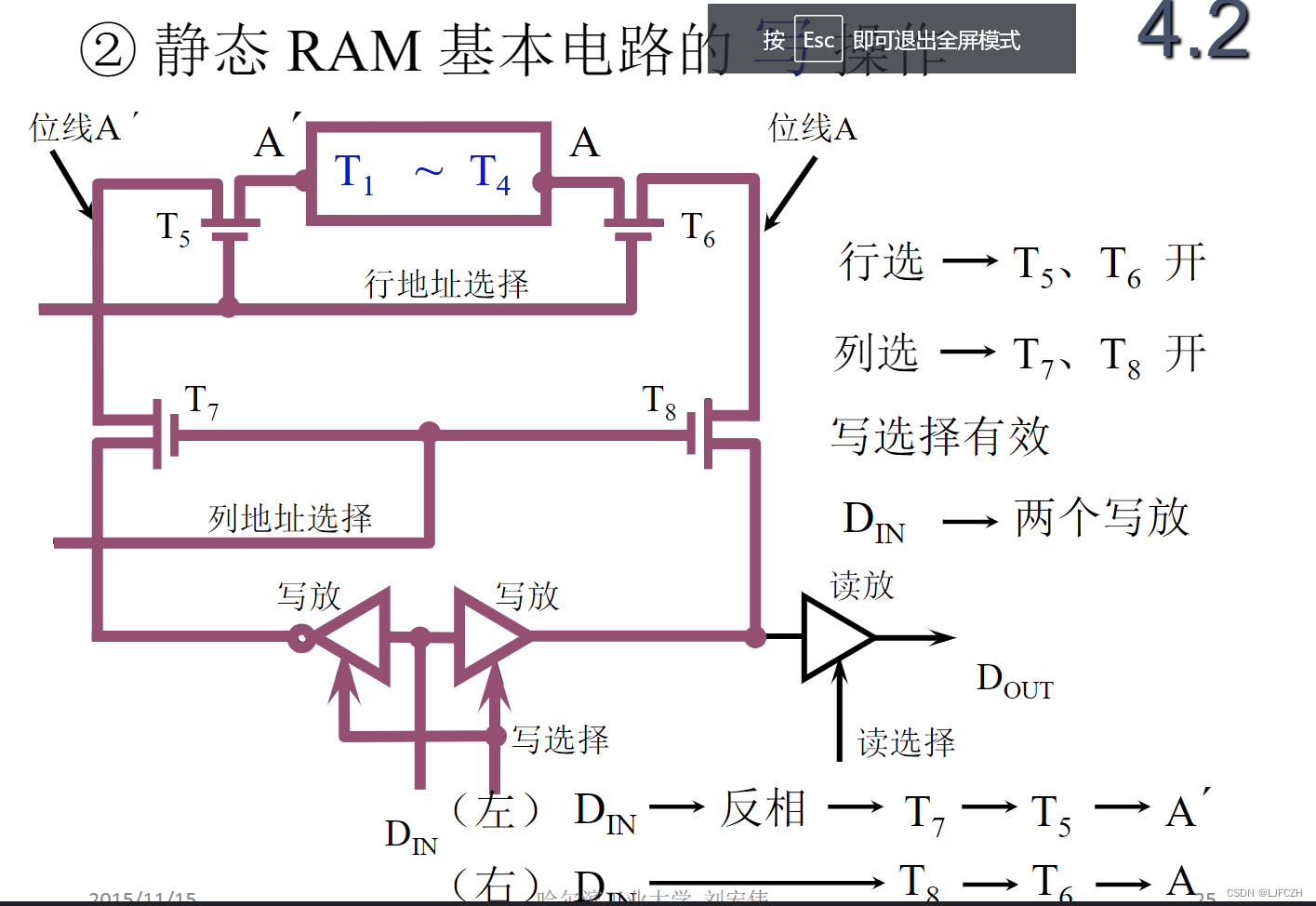

写操作时,数据从右边的写放大器写入到原端,从左边的写放大器经过非运算取反之后写如非端,保证原端、非端数据相反

- SRAM芯片举例

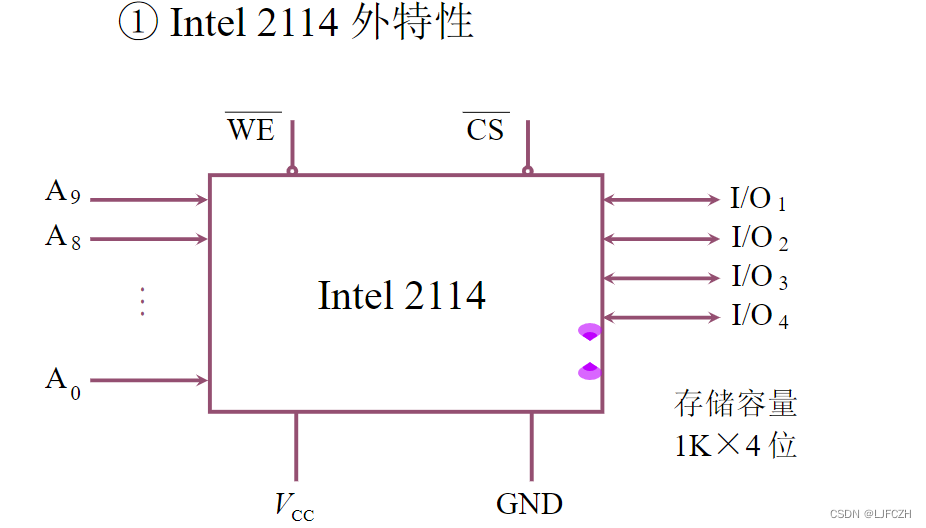

10根地址线,4根数据线,容量1K4

4根数据线,所以一次要读取或写如4位数据

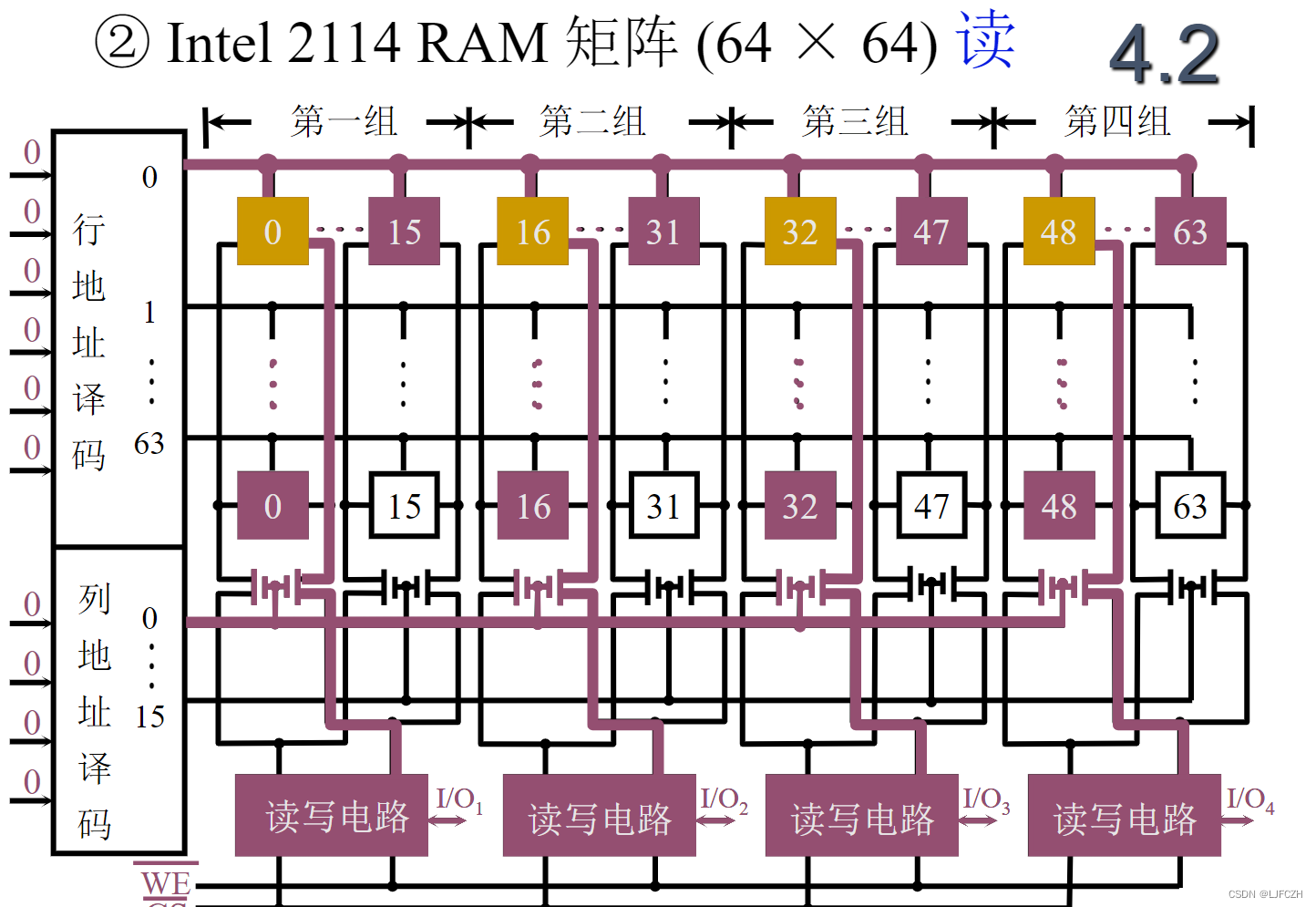

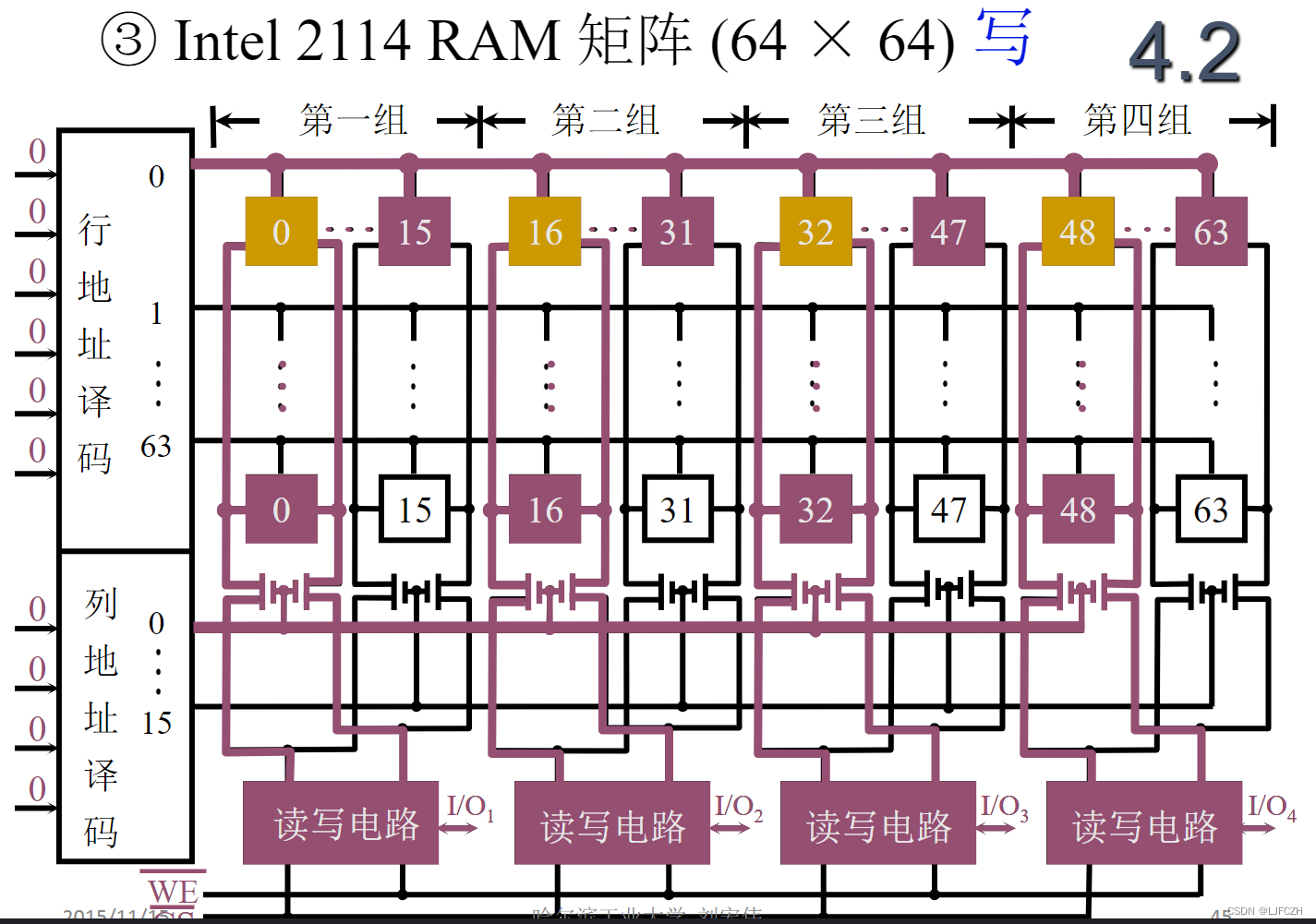

把它设计成64行64列,分成4组,每一组各连一条数据线

行地址为0时选中第0行,列地址为0时,选中每一组的第0列,这样每次选中4位数据进行操作

- 动态RAM(DRAM)

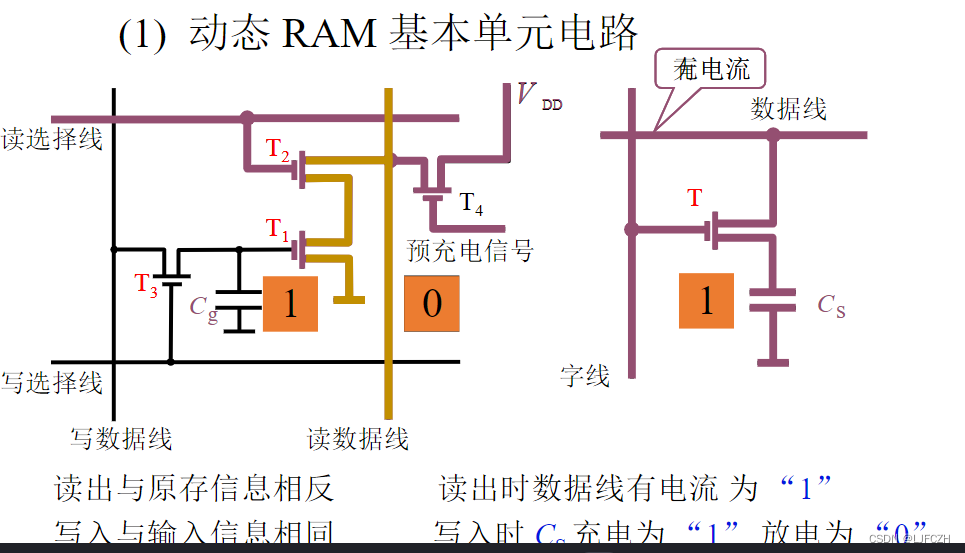

- DRAM存储0、1采用电容,有电表示1,没电表示0,通过读写控制线对电容进行充放电

- DRAM有两种实现方式:

- 三管

- 单管

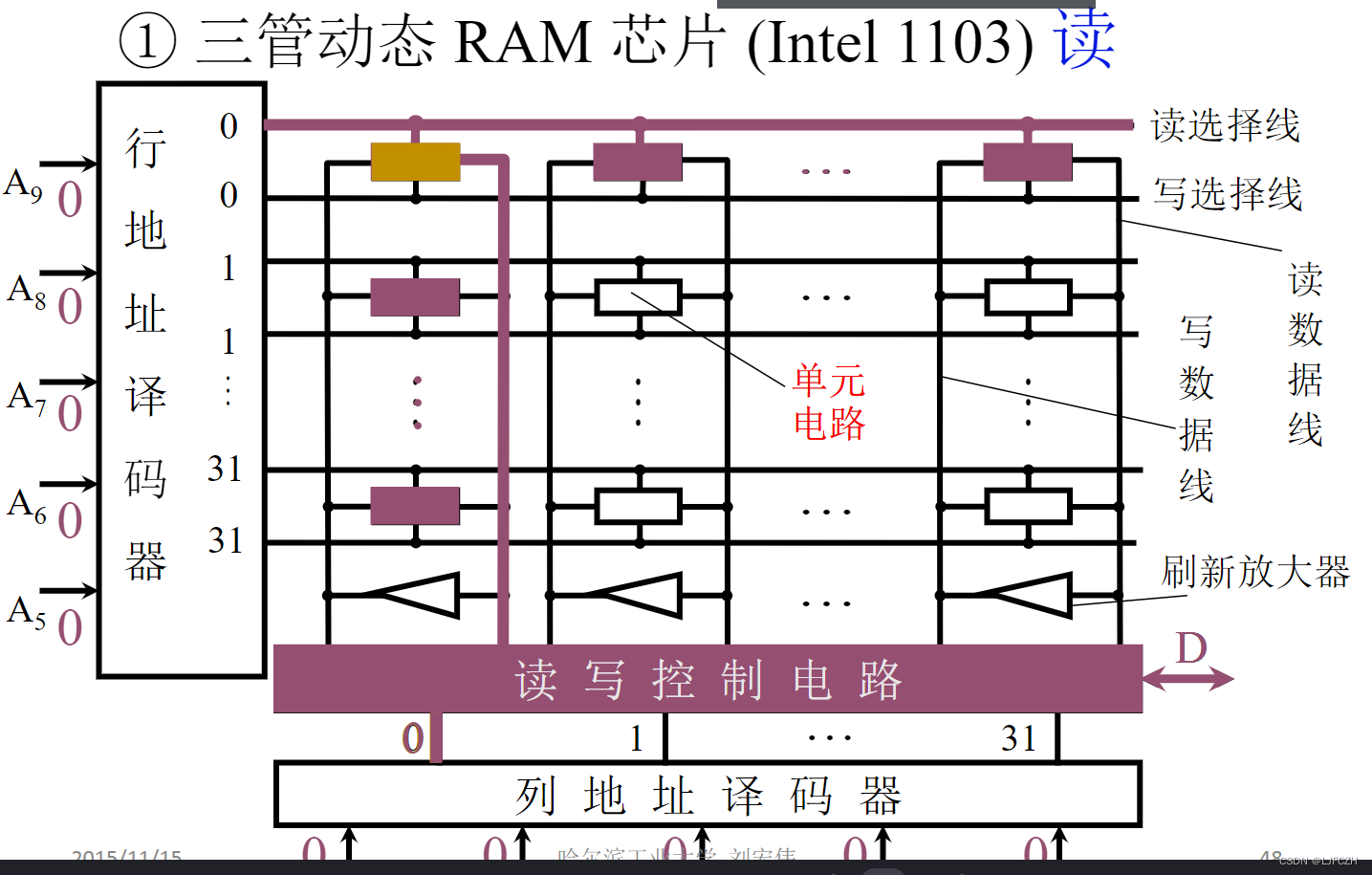

三管读操作:

1. 首先会有一个预充电信号使得T4导通,VDD这条线会通过T4使得读数据线上的信号为高电平表示1

2. 读操作时,读选择线被选中,是高电平,T2倍导通

3. 当电容为低电平保存的是0时,T1不导通,数据线读的数据是1

4. 当电容为高电平保存的是1时,T1导通,数据线读的数据是1,这时读数据线上的高电平通过T2、T1进行放电变成低电平,读出的数据变成0

5. 读出的数据与存储的数据相反,读出时需要非运算

三管写操作:

1. 写选择线选中,T3导通

2. 写数据线输入1,高电平通过T3向电容充电,保存的就是1

3. 写数据线输入0,写数据线为低电平,电容通过T3放电,保存的就是0

单管:

1. 子线就是控制线,当这个元件被选中时,子线会有电流,T会被导通

2. 电容有电时,通过T会将数据线变为高电平,传输的就是1

3. 写数据时,数据线有电,通过T向电容充电;数据线没电,电容通过T放电,电容保存的就是0

三管动态RAM举例:

需要注意的是每一列都有一个刷新放大器,这是因为电容会漏电,所以需要动态刷新:原来保存几还让它保存几

4. 动态RAM刷新

电容会漏电,需要刷新。以行为单位, 每次刷新一行,每一列各有一个刷新放大器

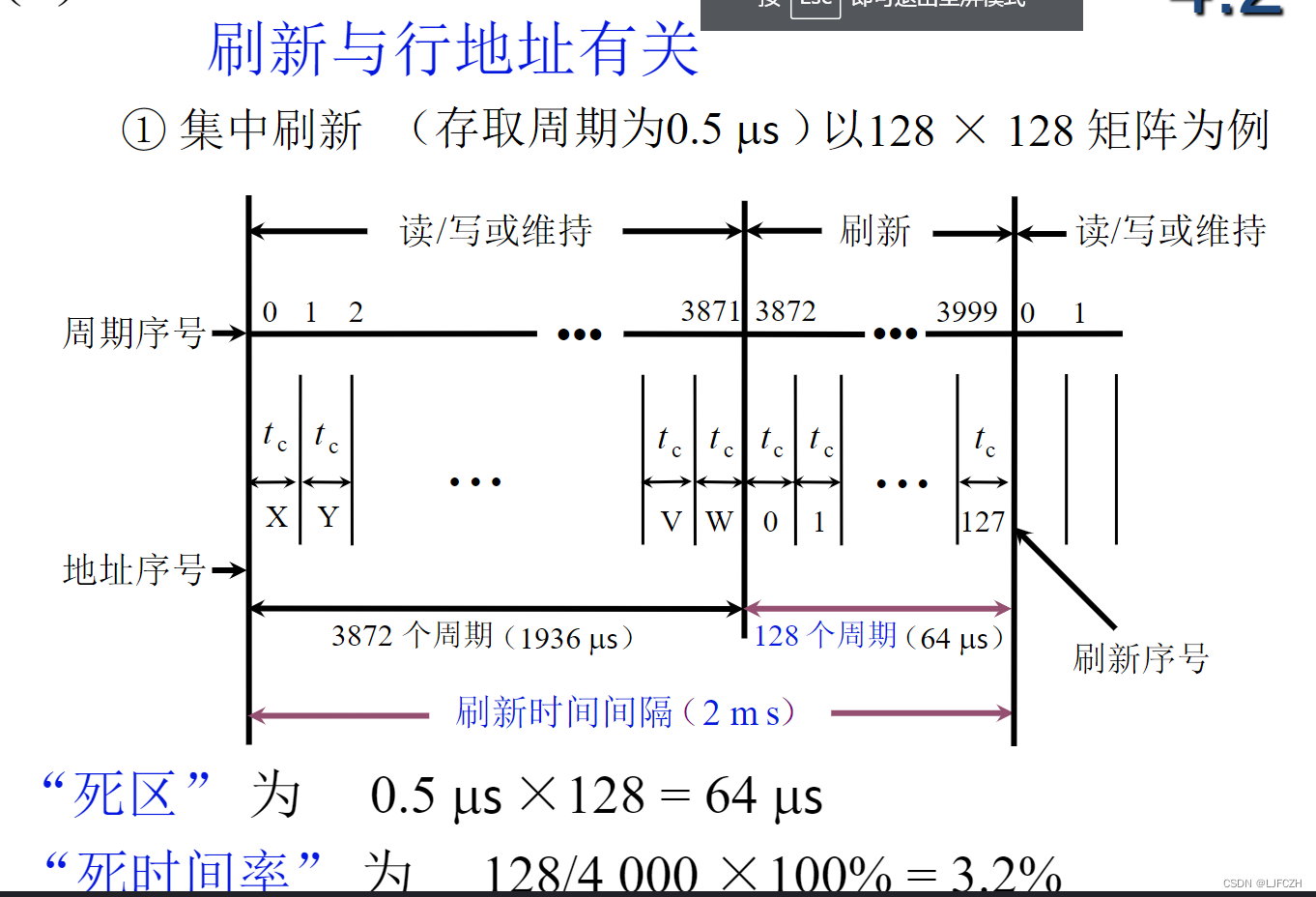

- 集中刷新

- 分散刷新

- 异步刷新

集中刷新:

假设刷新周期为2ms,存取周期为0.5us,就是每隔2ms要将芯片的全部电容刷新一遍,128行就需要128个周期(刷新一行需要一个存取周期),集中刷新会把刷新时间集中起来,其余时间用来读写操作,剩下的128周期用来刷新,死区时间为128*0.5=64us

在64us的死区时间里,无法进行读写操作

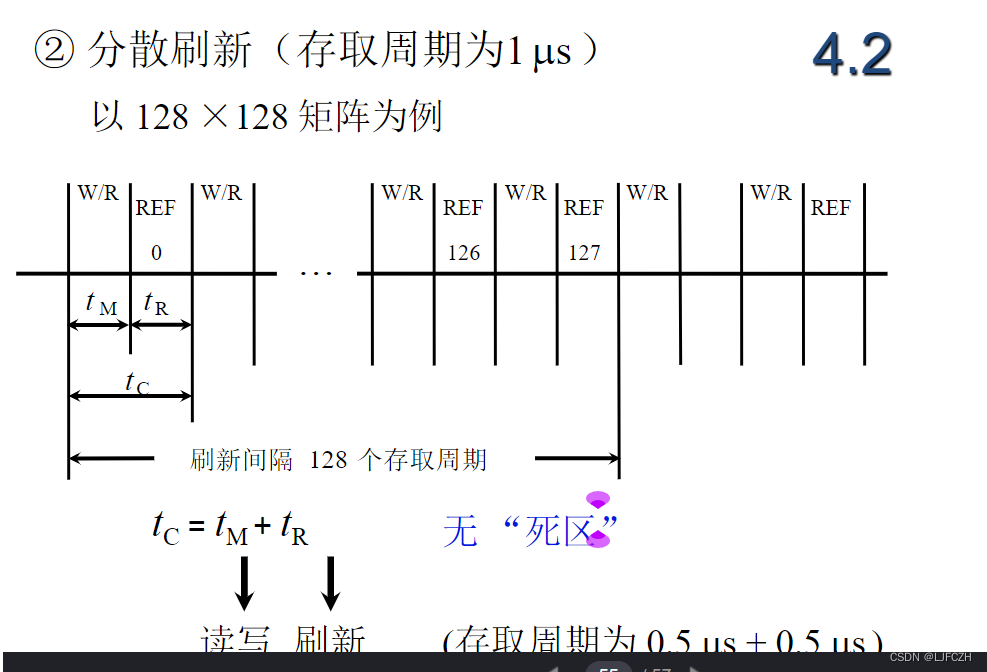

分散刷新:

每完成一次读写操作就伴随着刷新某一行

存取周期 = 读写周期 * 2,前半个存取周期完成读写,后半个进行刷新

128行经过128个存取周期就刷新一个遍,刷新周期为128us,2ms内共有2000/128 = 15.6个,后面继续刷新,2ms之后会完成15次刷新

虽然没有死区,但刷新得过于频繁,造成性能下降,存取周期变长

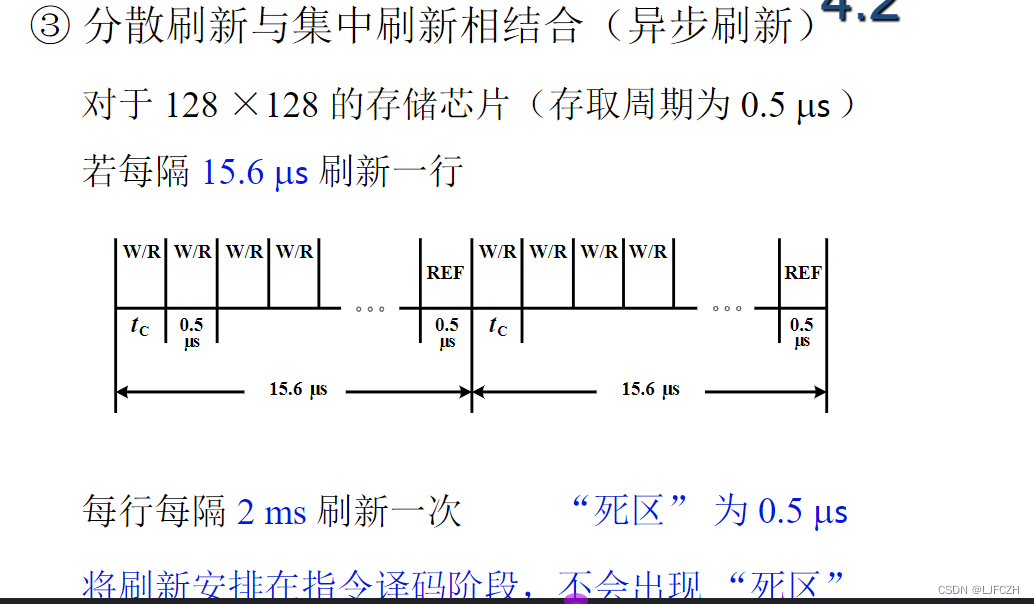

异步刷新:

每隔2ms全部刷新一次,128行每次刷新一行,将2ms分为128份,每份15.6us,每15.6us完成某一行的刷新

每一份是集中刷新,整体是分散刷新

最后会有0.5us的死区时间,可以将每次刷新放到译码阶段消除死区

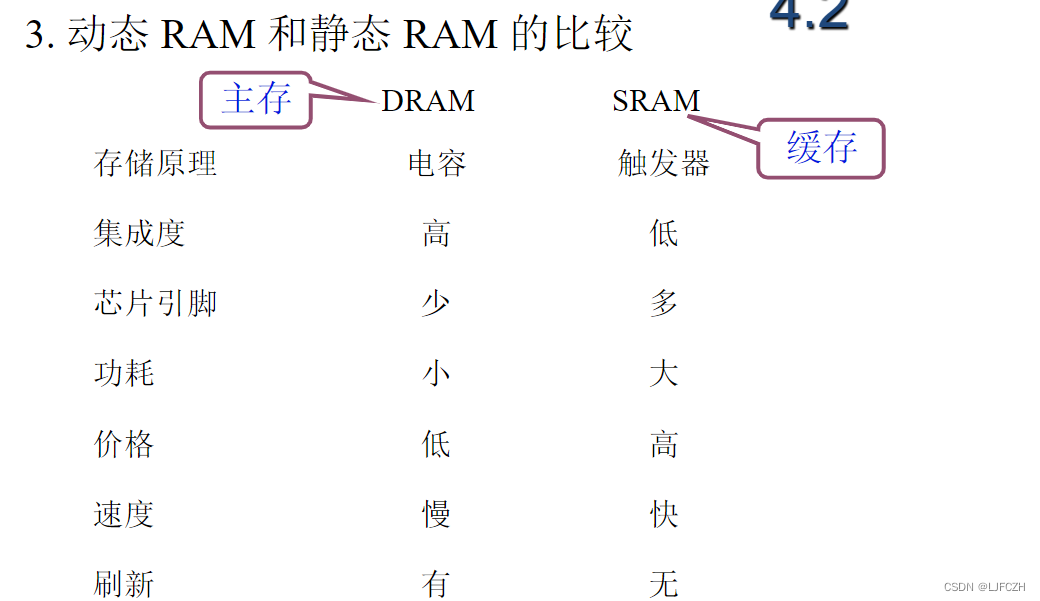

5. SRAM和DRAM比较

SRAM采用触发器,结构较复杂,引脚多,集成度低,但速度快,价格高

DRAM采用电容,结构较为简单,引脚少,集成度高,但速度慢,价格低

6. ROM

ROM一般保存系统程序、参数等

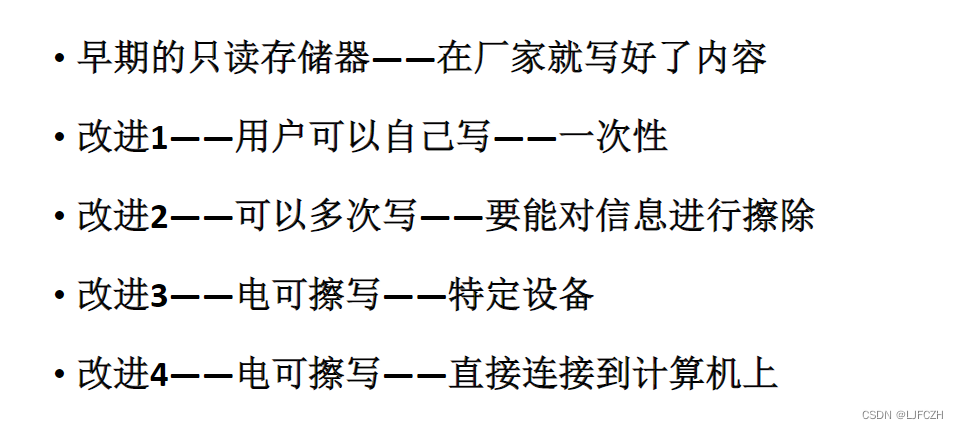

只读存储器ROM发展历程

- 最开始由厂家写好,用户不能修改——MROM

- 用户可以写1次——PROM

- 用户可以写多次——EPROM

- 用户可以写多次,可以电擦除——EEPROM

分类

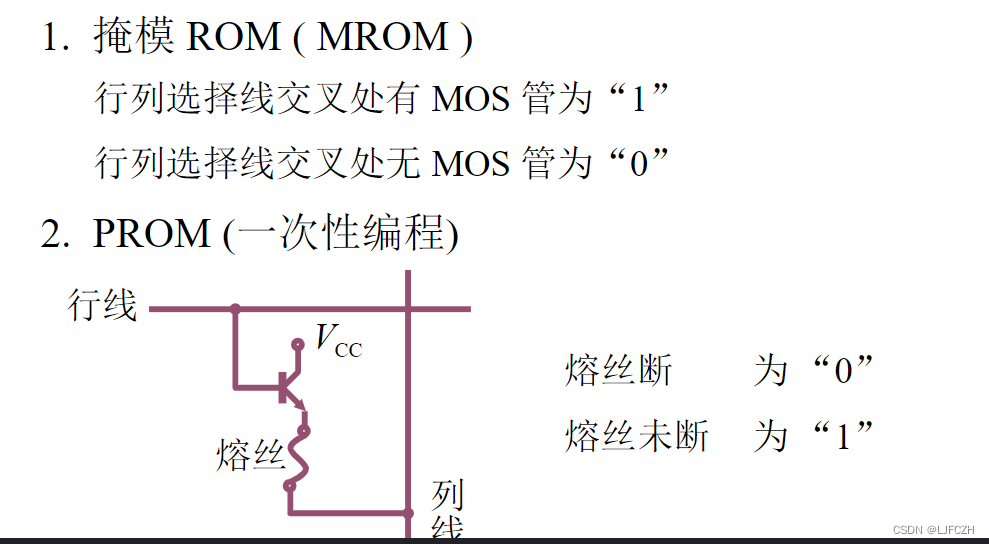

- MROM:根据行列选择性交叉处有无MOS管决定存储1或0

- PROM:可以写一次,写操作时,电流会将熔丝烧断,根据熔丝是否断决定存储0或1,断了之后不能复原,所以只能写一次

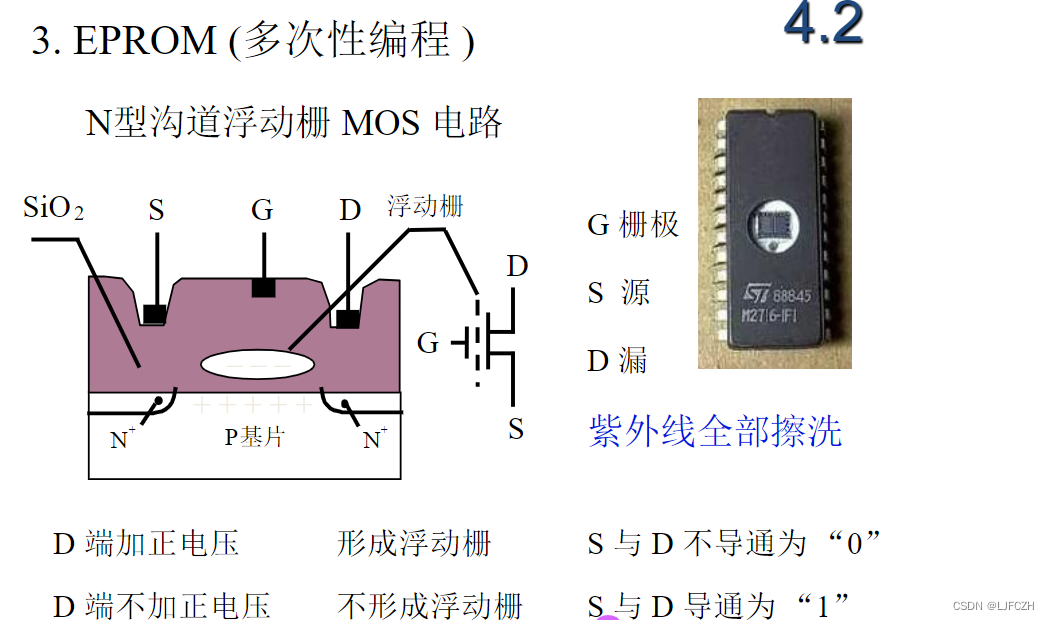

- EPROM:可写多次,紫外线擦除,比较麻烦。便宜,集成度高

- EEPROM:写多次,电擦除,局部、全部擦除

- Flash Memory(闪存):U盘,比EEPROM快,具备RAM功能