正文

CPU 部件:

- CPU 简介:CPU 是计算机内部功能最复杂且技术难度最高的子系统,其部件众多、架构复杂、功能多样。(所以,如果你懂得如何用数字电路 FPGA 去设计一个 CPU,那么,你的能力将深不可测哟)

- CPU 内部的主要部件:从硬件的角度,主要包括运算部件、控制器、缓存部件、寄存器(堆)、时序部件,它们通过数据通路、控制通路相互连接,从而形成 CPU 的微架构。

- 运算部件:通过 ALU 对操作数进行运算,主要是算术运算和逻辑运算;ALU 主要是在加法器(全加器)的基础上发展起来的,然后影响加法器运算速度的主要因素是进位信号的传递。

- 控制器:根据指令、时钟、外部信号等信息,产生各种控制信号(微命令),以便控制各种功能部件协同工作,完成指令的功能;产生微命令的方式主要有两种,即组合逻辑硬件电路和微程序译码。

- 缓存部件:主要是 Cache 从主存中读取部分指令和数据。

- 寄存器(堆):主要是存储各种用途的数据信息。(一个地址对应一个存储单元,一个存储单元对应一个寄存器(组))

通用寄存器(多个):

主要用途:存储各种用途的数据信息。

特征:通用寄存器有全局唯一地址,可通过地址码访问,可在机器指令中直接使用,负责提供操作数、地址码、存放运算结果等等;

暂存器(多个):

主要用途:用来暂存产生的临时数据,以备在后续操作过程中使用;

特征:内部专用,无需分配地址码,不能在机器指令中使用;

指令寄存器(IR)(一个):

主要用途:用于存放指令代码;

特征:从存储器(或者指令缓存)中读取到指令以后,就直接存入到指令寄存器中;CPU 内部使用,程序员无法通过程序对该寄存器进行直接的读写操作;

程序计数器(PC)(一个):

主要用途:用来指明指令在存储器(IR)中的存放位置,即存储单元的地址码;

特征:取指令结束后,PC 保存的地址码自动修改,以指向下一条指令的存储单元(立刻存储下一条指令所在的内存的地址),修改量取决于指令字长和存储器的编址单位;

程序状态字寄存器(PSW)(一个):

主要用途:记录现行程序的运行状态和程序的工作模式;

特征:A、特征位,也叫标志位,反映了 CPU 的当前状态;指令执行时,根据情况自动设置这些特征位,作为后续操作的判断依据,通常有 5 类:进位C、溢出V、零值Z、负值N、奇偶P;自动设置,即具备该特征,就设置该标志位为一;B、编程设定位,某些位或字段可通过程序来设定,以决定程序的调试、对中断的响应、程序的运行模式等等:跟踪位T、允许中断I、程序优先级P、运行模式;

地址寄存器(MAR)(一个):

主要用途:读写存储器时,先要定位存储单元,因此设置 MAR 来存放目标单元的地址码;

数据缓冲寄存器(MBR)(一个):

主要用途:过渡性地存放 CPU 与主存之间交换的数据;

特征:无论是从主存读取的数据,还是写入到主存的数据,都要经过它;

堆栈指针(SP)(一个):

主要用途: 固定存放堆栈的栈顶单元的地址码,根据这个地址码,去读写堆栈。 - 时序部件:定义了周期、节拍、脉冲等频率类型的信号序列;产生时序信号的部件称为时序发生器或时序系统,由 1 个低频振荡器(输出频率固定的基准脉冲信号,即外频,作为系统时钟信号)和倍频逻辑组成。

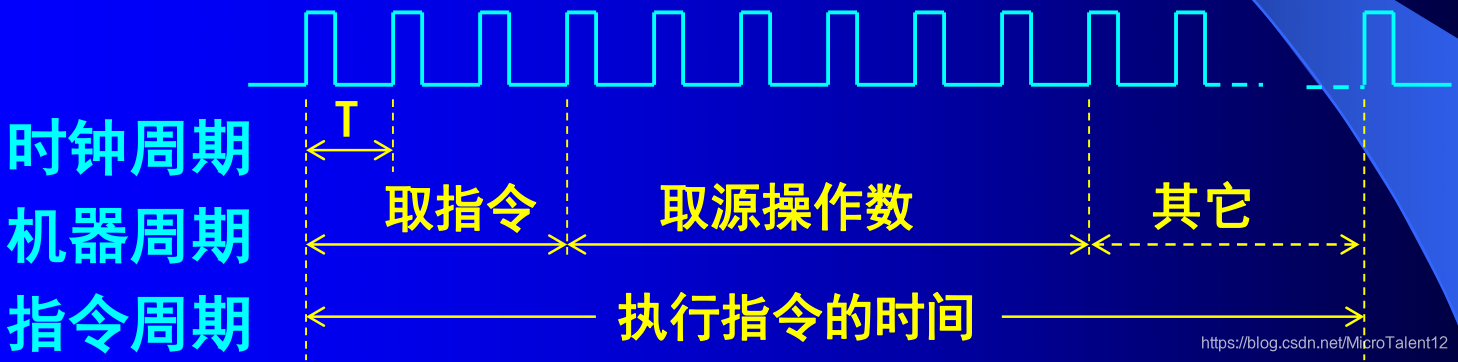

指令周期包括若干(>= 2)机器周期(工作信号);

机器周期包括若干(>= 1)时钟周期(节拍信号);

CPU 执行与 RISC:

- CPU 执行流程:

取指:从存储器中读取;

译码:通过控制器进行、产生控制信号;

执行:寻址、取数、运算。 - 如何控制上述部件协同工作,完成指令功能呢:

同步控制方式:A、每步操作都需要向统一的外部时序信号对齐;B、各步操作之间无交互;

异步控制方式:A、每步操作都不需向统一的外部时序信号对齐;B、各步操作之间通过交互应答来实现协同。 - 设计 CPU 的一般过程:指令系统(指令集、指令格式、寻址方式、User 指令类型)、数据通路设计、控制器设计、CPU Top 设计。

- 指令:Instruction,计算机执行某类操作的信息的集合,是 CPU 工作的主要依据。(其实计算机的运算如加减乘除之类的信息全部都包含在这指令的某个段里,当把指令输送给控制器进行解码之后,就有了 CPU ALU 的相应操作)

- 指令集:Instruction Set,处理器能执行的全体指令的集合;决定了计算机的硬件功能,是计算机中软硬件的分界面。

- 指令字:用来表示指令的一组二进制代码。

- 指令字长:指令字的长度,指令中包含的二进制代码位数。

- 机器字长:计算机能够直接处理的二进制数据的位数,等于寄存器的宽度。

- 指令集类型:CISC(复杂指令集计算)、RISC(精简指令集计算);CISC 到 RISC 的技术背景主要一点就是 2 - 8 规律:指的就是 CISC 中不同的指令使用频率悬殊,约占 20% 的简单指令使用频率高达 80%,而约占 80% 的复杂指令使用频率只有 20%,而那些很少被用到的特殊指令让 CPU 的设计变得极为复杂,大大增加了硬件设计的时间成本与面积开销。所以,我们不能够“平等对待”所有的指令(这个思想在我们的生活中也很重要,谨记,谨记),正是因为如此,RISC 一般只有少量指令如存取数据的时候,才会读写存储器,其余指令只涉及 CPU 内部寄存器,速率快效率高。还有一点就是复杂指令的功能可以用简单指令构成的子程序来等效实现。

- 指令的基本格式:操作码 + 地址码/操作数。

- 指令的地址结构:指令中提供的地址一般为地址偏移量/立即数、寄存器编号。

- 提供地址的方式:显式地址方式(指令中明确指明地址码,可以通过直接或者间接的方式给出)、隐式地址方式(地址码隐含约定,不在指令中出现,从而简化了地址结构)。

- 常见的地址结构类型:四、三、二、一、零地址结构指令。

- 主机对于外设的寻址方式:寻找 I/O 接口中的(I/O 端口)寄存器的方式;该类寄存器的编号 ,也称为 I/O 端口的地址,简称端口地址。

MIPS32 架构:

- MIPS32 架构的指令格式:RISC 的指令集类型(R、I、J)、32 位的指令字长、32 个的寄存器数量(如下)。

- MIPS32 中,只有 lw 和 sw 这两个指令可以访问存储器。

- MIPS 指令操作码的最高两位隐含说明了不同的寻址方式(也可以在地址码的最高三位中设置):

00:寄存器-寄存器寻址;

01:寄存器-变址寻址;

10:基址-立即寻址;

11:基址-基址寻址。

指令中的寻址方式:

- 立即寻址:指令中直接包含了操作数,用来提供偏移量、常数、设置初值等等;取值之后,直接截取指令中的低 16 位代码即可获取操作数的方式(哎,也就是把数直接给你嘛,无需去索引,明明白白的)。

- 直接寻址:指令中直接给出操作数的地址码,可以是寄存器编号或者是存储器地址(哎,也就是把地址直接给你嘛,去索引一下,明明白白的,而地址长度也就限制了索引范围)。

- 间接寻址:指令给出操作数的间接地址;有主存、寄存器、堆栈间接寻址;而这在 RISC 中很少使用的。

- 变址寻址:指令给出一个寄存器编号和一个地址量,寄存器内容与地址量之和为有效地址;有效地址 = 寄存器内容(R)+ 指令中的立即数 D(有点麻烦,就是索引一次寄存器编号,然后与地址量相加,然后再去索引一次)(基址,就是起始地址;变址,就是相对地址)。

- 基址寻址:类似于变址寻址;变址寻址是指令提供基准量,寄存器提供偏移量;基址寻址是指令提供偏移量,寄存器提供基准量。

- PC 相对寻址:指令给出偏移量,PC 当前值与偏移量相加得到有效地址;这是一种特殊的基址寻址方式,有效地址相对于 PC 浮动,编程较为方便。

- 页面寻址:也称伪直接寻址,就是指令给出位移量,PC 的高位部分与位移量拼接形成有效地址;PC 的高位部分可以是页号,然后位移量可以是页内地址(这里要对“页”这个字解释一下,通常出现“页面”,指的就是三维空间下的数据存储,可想象一个具有多个 Sheet 的表格,不同的 Sheet 就对应一个“页”,二进制数的高位就可以对应你的“页号”,剩下的低位数据就可以对应你的页号里面不同行列所在的位置,你可以建立一个 WPS Excel 形象地理解一下,这就是“页式存储系统”)。

流水线 Pipeline:

- 流水线的特点:

流水线的子过程称为流水线的“级”,子过程的数目称为流水线的“流水深度”;

流水技术适合于大量相同指令的执行,每个子过程由专用的功能段实现,各功能段的时间应基本相等,通常为 1 个时钟周期,即 1 拍;

流水线需要经过一定的通过时间才能稳定,稳定即无空闲功能段。 - 流水线的层次:

操作部件级流水:把功能部件( 如浮点加 )细分成若干子功能段 ( 求阶差、对阶、尾数加、规格化 ) ;多条指令中该操作的不同子操作可在这些子功能段上流水执行;

指令级流水:把一条指令的执行分成若干个过程( 如 FT/DT/ET ),多条指令的不同过程可以流水执行;

处理机级流水:把复杂任务细分成若干子任务( 指令组 ),多个任务的不同子任务可以在不同处理器上流水执行。 - 流水线的指标:

吞吐率:单位时间内处理的任务数或数据量;

加速比:同一程序,不采用流水的执行时间与采用流水的执行时间的比值,如 24T/9T(如下浮点加法的四段式流水线时空图);

利用率:流水线中各部件的平均利用率,即一定时间内,部件实际工作时间与部件总时间的比值,如 (4T*6)/(4T*9)。

多线程与多核:

- 多线程:在一颗 CPU 上同时硬件级地并行执行多个程序的指令。

- 多核:在一颗处理器芯片上集成多个 CPU 内核(包括集成 GPU);主要是通过提高单核 CPU 主频 和 IPS 的手段已无潜力。

本文含有隐藏内容,请 开通VIP 后查看