Clock Gating简介

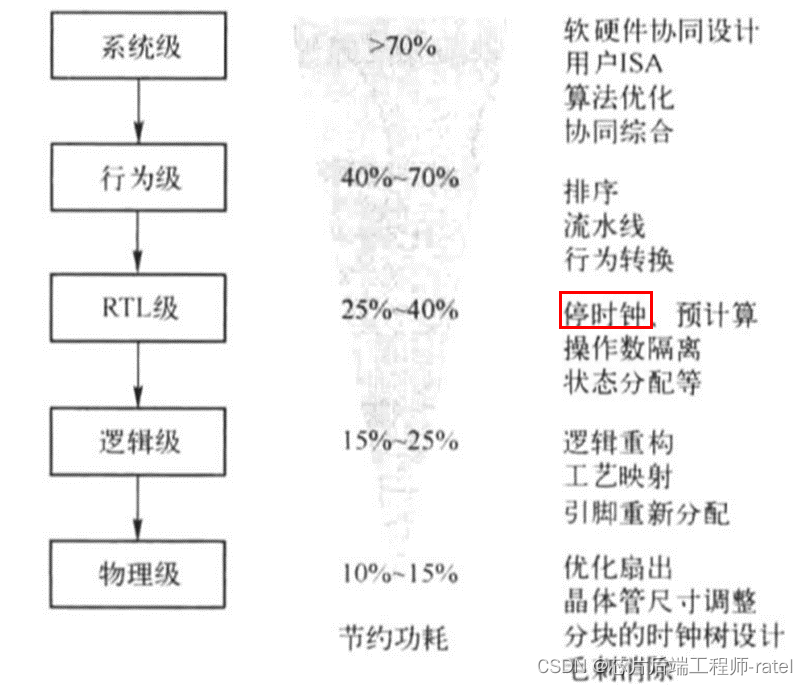

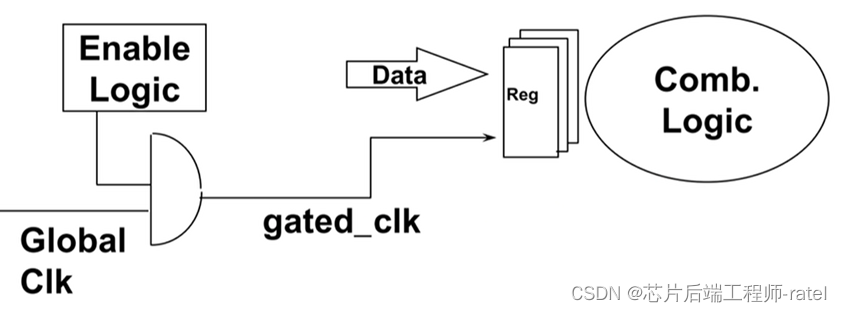

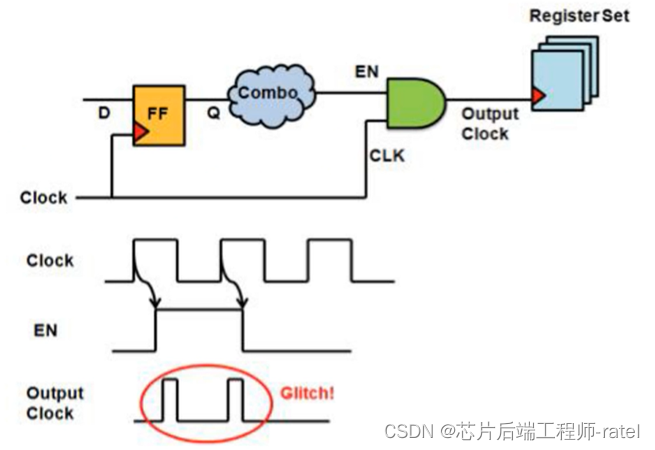

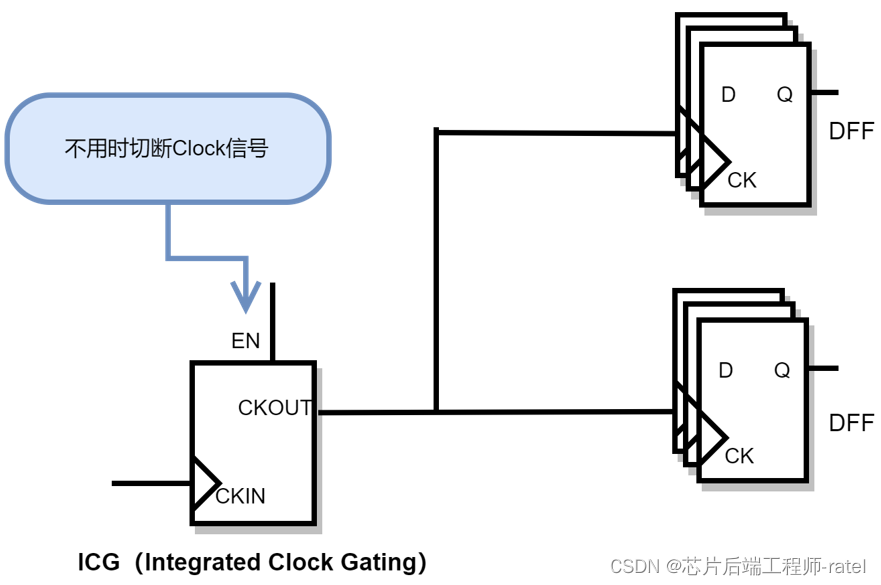

门控时钟(clock gating)在RTL级电路设计过程中进行低功耗优化常用方法,能够有效降低动态功耗(翻转功耗)。Clock gating cell 可以由与门,与非门,或门或者或非门构成,但很容易产生Glitch。在实际使用中,一般用ICG(集成门控时钟单元)来完成clock gating。

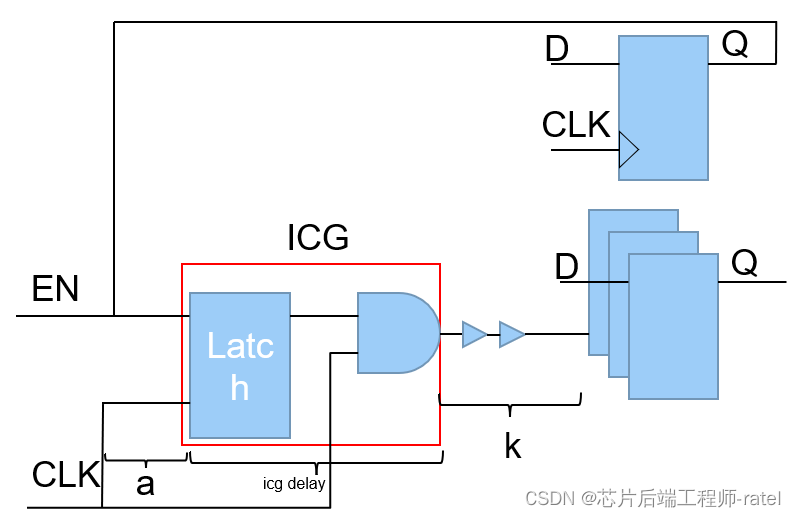

下图展示了glitch的产生原因

ICG setup timing violation 产生原因(一)

在CTS时钟树综合的时候,ICG不会被看作sink,通常放置在source点附近,因此就会出现如上图这种结果。

上图可以看出,在分析DFF到ICG的setup timing时:

launck clk delay = a + k + d(icg)

capture clk delay = a

因此,对于ICG的setup path,天然存在clock skew:k ,而skew的大小完全取决于ICG 距离 sink DFF有多远。

在出现setup violation的ICG path上,比较多见的就是因为ICG和sink DFF的clock之间存在较多逻辑或者物理上距离较远,从而导致skew较大而发生setup violation。

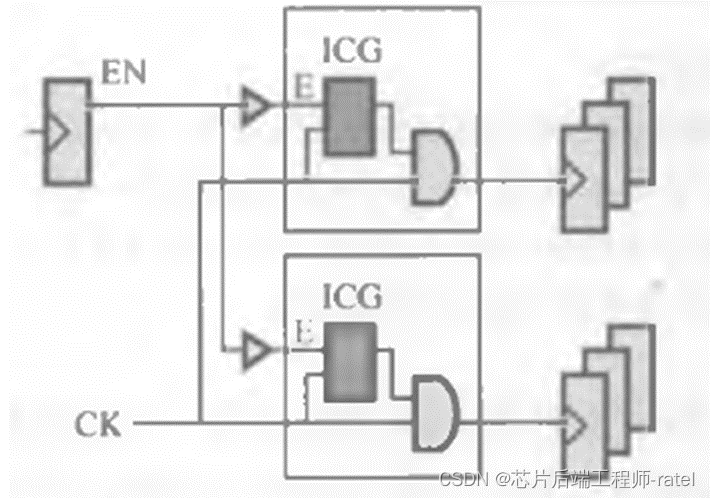

ICG setup timing violation 产生原因(二)

ICG cell 放在了sink点附近(skew小),这种ICG setup timing 问题通常是data path太长(逻辑级数)的原因。

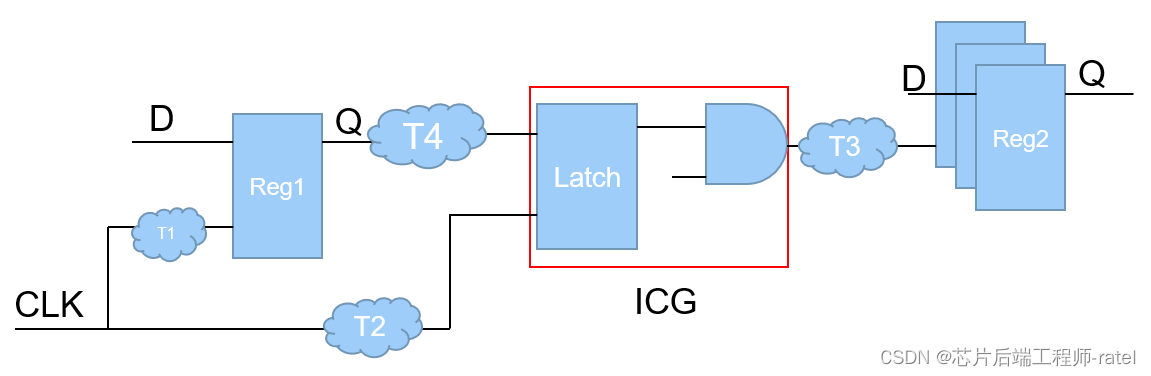

ICG setup timing violation 修复策略

CTS 阶段默认Reg1和Reg2尽量长平,所以 T1 ≈ T2 + D(icg) + T3

当reg1和cgate进行clock gating check时,T1 >> T2,也就是launch clock >> capture clock

方法:

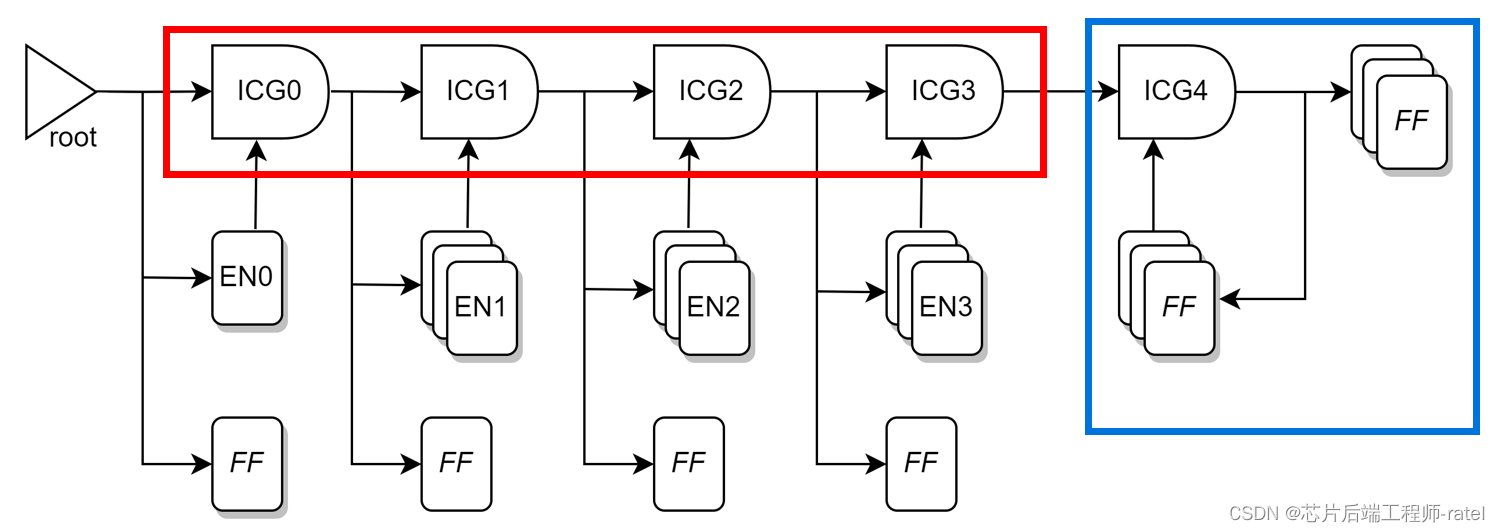

EDA工具也提供命令来收紧 ICG 的timing constraint来迫使工具来优化这些Path

比如:set_clock_gating_check 命令,其实也是对data path路径的优化。

在place之前 :set_clock_gating_check

在CTS之后 :reset_clock_gating_check为default

注:CTS之前设clock gating check为了弥补clock tree, ICG cell的latency较短,所以加一些余量。CTS之后remove_clock_gating_check并不是不让tool做ICG timing check,而是用library的gating check的值。