一、基础语法

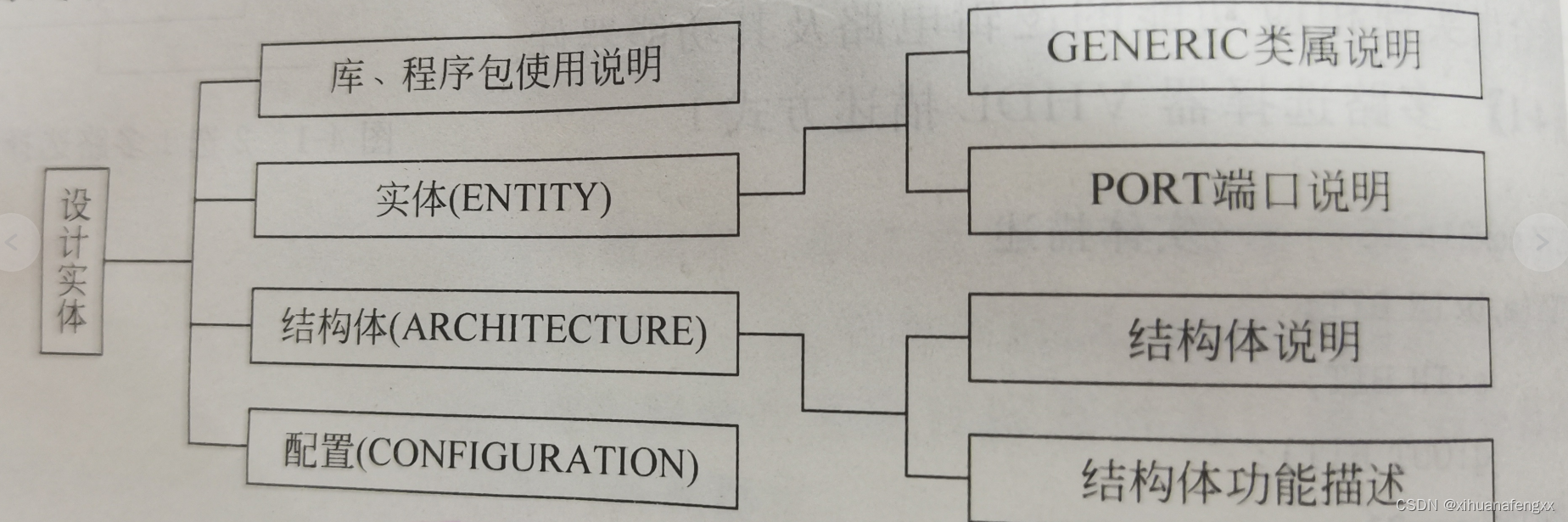

1、代码的总体架构

1.1 库、程序包的使用

类比与c语言的引用头文件,python中的调用包

LIBRARY IEEE; -- 调用IEEE库

USE IEEE.STD_LOGIC_1164.ALL; --调用IEEE库中的STD_LOGIC_1164程序包(必须在设计实体前显示出来)

-- 这一句话就像python中的 form pandas import *

1.2 实体(ENTITY)

类似于其它语言的全局变量。格式为

ENTITY 实体名称 IS

[GENERIC(类属表);]

[PORT(端口名);]

END 实体名(也可以省略)

1.1.1 GENERIC(类属说明语句)

GENERIC ([CONSTANT]常数名:[IN]数据类型[:=静态表达式(初值)]);

GENERIC 是用于说明设计实体和其外部环境通信的对象,规定端口的大小、实体中子元件的数目、实体的延时特性等。只能用整数类型表示,如整型、时间型等,其他类型的数据不能逻辑综合(还没怎么用到过)

1.1.2 PORT(关键字用于定义模块的端口)

PORT( [SIGNAL] 端口名称:端口模式 数据类型 [:=静态表达式(初值)])

- SIGNAL:SIGNAL 是关键字,但是由于 PORT 之后必须是信号类,所以一般可以将 SIGNAL关键字省略。

- 端口名称:是该端口的标识,通常由英文字母和数字组成,但是必须是英文字母打头。

- 端口模式:输入(IN)-只读,输出(OUT)-单项赋值模式,输出,双向(INOUT)-;缓冲(BUFFER)-具有读功能的输出模式,不允许作为双向端口使用。

- 数据类型:说明流过该端口的数据类型,常用的数据类型有 BIT(位)、BIT_VECTOR(位向量)、BOOLEAN(布尔型)和 INTEGER(整数型)4 种。

-- 实体(generic / port说明)

ENTITY light IS

PORT(clk, res:IN std_logic; -- 创建时钟端口clk和复位端口res(输入模式)

out1:OUT std_logic_vector(3 DOWNTO 0):="0000"); --(标准位矢类型,从高到低) 创建输出端口,对应4个led。要使用位移操作符(位输出模式)其左侧必须为BIT_VOCTOR类型(位矢量)

END light;

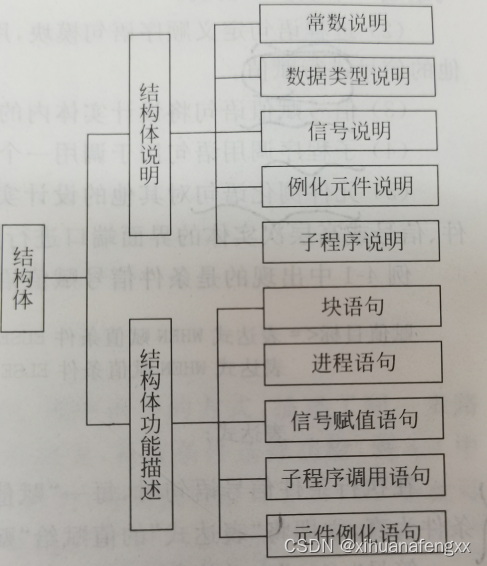

1.3 结构体

类似于其他语言的函数集合,在里面拥有很多小函数。

结构体描述实体的行为功能,一个实体可以有多个结构体。结构体是一个基本设计单元,它具体地指明了所设计模块的行为、元件及内部的连接关系,也就是说它定义了设计单元具体的功能。结构体对其基本设计单元的输入/输出关系可以用 3 种方式进行描述,即行为描述(基本设计单元的数学模型描述)、寄存器传输描述(数据流描述)和结构描述(逻辑元件连接描述)。格式为

ARCHITECTURE 结构体名 OF 实体名 IS

[定义语句]

BEGIN

[并行处理语句]

END 结构体名;

也没学太明白,结构体功能描述主要是由以下一些解释:

- 块语句:由一系列并行执行的语句构成的组合体,他的功能是将结构体中的并行语句组成一个或多个模块。

- 进程语句:定义顺序语句模块,用以将从外部获取的信号值或内部的运算数据向其他信号进行赋值。

- 信号赋值:设计实体内的处理结果向定义的信号或界面端口进行赋值。

- 子程序:调用一个已经设计好的子程序

- 元件例化语句:对其他的设计实体作元件的调用说明,并将此元件的端口和其他的元件、信号、或高层次的界面端口进行连接。

-- 创建结构体 behave并综合结构体behave到实体hello上 light 为实体名

ARCHITECTURE behave OF light IS

SIGNAL sta:std_logic_vector(3 DOWNTO 0) :="0001"; -- 初始化sta值

-- SIGNAL cnt:integer RANGE 0 TO 23; --创建整型的cnt,数值范围为0到23

SIGNAL count:integer:=0; -- SIGNAL 信号名:类型标识:[=初值]

SIGNAL tim:bit:='0';

BEGIN

PROCESS(clk) -- PROCESS() 进程语句,顺序执行,clk为关键词(铭感词),只要发生变化,语句执行

BEGIN

IF (clk'event and clk='1') THEN --如果时钟上升沿,则cnt加1(一个进程只能有一个边缘触发)

count<=count+1;

IF(count = 5000000) THEN -- 主频为50MHZ 设置为50 000 000 为1s。5 000 000 为0.1s的闪烁速度

tim<='1';

count <=0;

else

tim<='0';

end if;

end if;

END PROCESS;

PROCESS(tim) -- 含有多个进程语句,都为并行执行

BEGIN

IF(tim'event and tim = '1') THEN

sta <= sta(2 DOWNTO 0) & sta(3);

END IF;

END PROCESS;

out1 <=sta; -- 信号赋值

END behave;

a <= sta(2 DOWNTO 0) & sta(3);

END IF;

END PROCESS;

out1 <=sta; -- 信号赋值

END behave;

本次记录的代码为–vhdl版本的流水灯

全部代码如下

-- 库、程序包使用说明

LIBRARY IEEE; -- 调用IEEE库

USE IEEE.STD_LOGIC_1164.ALL; --调用IEEE库中的STD_LOGIC_1164程序包(必须在设计实体前显示出来)

-- 实体(generic / port说明)

ENTITY light IS

PORT(clk, res:IN std_logic; -- 创建时钟端口clk和复位端口res(输入模式)

out1:OUT std_logic_vector(3 DOWNTO 0):="0000"); --(标准位矢类型,从高到低) 创建输出端口,对应4个led。要使用位移操作符(位输出模式)其左侧必须为BIT_VOCTOR类型(位矢量)

END light;

-- 创建结构体 behave并综合结构体behave到实体hello上 light 为实体名

ARCHITECTURE behave OF light IS

SIGNAL sta:std_logic_vector(3 DOWNTO 0) :="0001"; -- 初始化sta值

-- SIGNAL cnt:integer RANGE 0 TO 23; --创建整型的cnt,数值范围为0到23

SIGNAL count:integer:=0; -- SIGNAL 信号名:类型标识:[=初值]

SIGNAL tim:bit:='0';

BEGIN

PROCESS(clk) -- PROCESS() 进程语句,顺序执行,clk为关键词,只要发生变化,语句执行

BEGIN

IF (clk'event and clk='1') THEN --如果时钟上升沿,则cnt加1(一个进程只能有一个边缘触发)

count<=count+1;

IF(count = 5000000) THEN -- 主频为50MHZ 设置为50 000 000 为1s。5 000 000 为0.1s的闪烁速度

tim<='1';

count <=0;

else

tim<='0';

end if;

end if;

END PROCESS;

PROCESS(tim) -- 含有多个进程语句,都为并行执行

BEGIN

IF(tim'event and tim = '1') THEN

sta <= sta(2 DOWNTO 0) & sta(3);

END IF;

END PROCESS;

out1 <=sta;

END behave;

本文含有隐藏内容,请 开通VIP 后查看