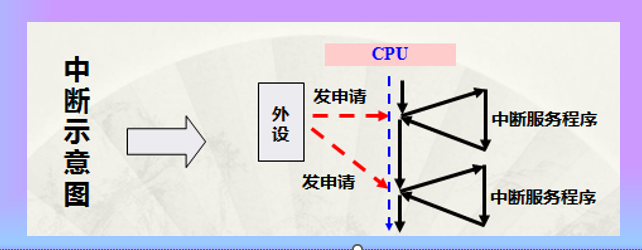

中断概念

CPU执行程序时,由于发生了某种随机的事件(外部或内部),引起CPU暂

时中断正在运行的程序,转去执行一段特殊的服务程序(中断服务子程序

或中断处理程序),以处理该事件,该事件处理完后又返回被中断的程序

继续执行,这一过程称为中断。引发中断的称为中断源。比如:看电视

时突然门铃响,那么门铃响就相当于中断源。

有些中断还能够被其他高优先级的中断所中断,那么这种情况又叫做中断的嵌套。

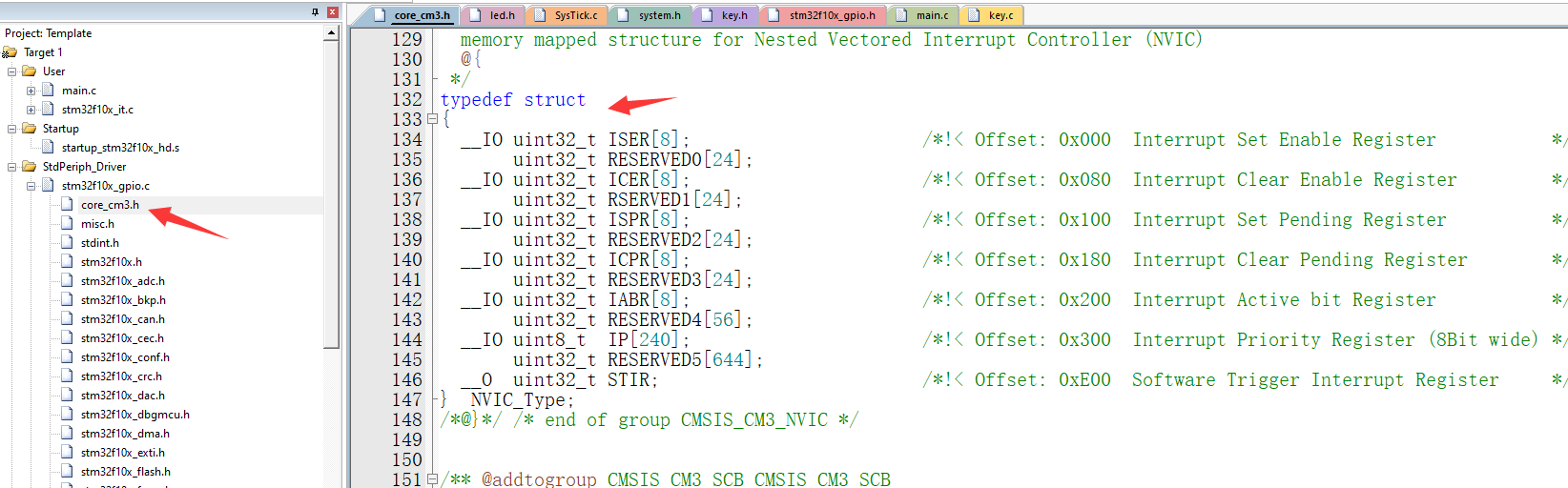

NVIC英文全称是Nested Vectored Interrupt Controller,嵌套(Nested)向量(Vectored)中断控制器(Interrupt Controllerv)

它属于M3内核的一个外设,控制着芯片的中断相关功能。由于ARM给NVIC预留了非常多的功能,但对于使用M3内核设计芯片的公司可能就不需要这么多功能,于是就需要在NVIC上裁剪。ST公司的STM32F103芯片内部中断数量就是NVIC裁剪后的结果。

中断控制相关寄存器在固件库core_cm3.h文件NVIC结构体内。可打开任意库函数工程即可查看到,如下:

中断优先级

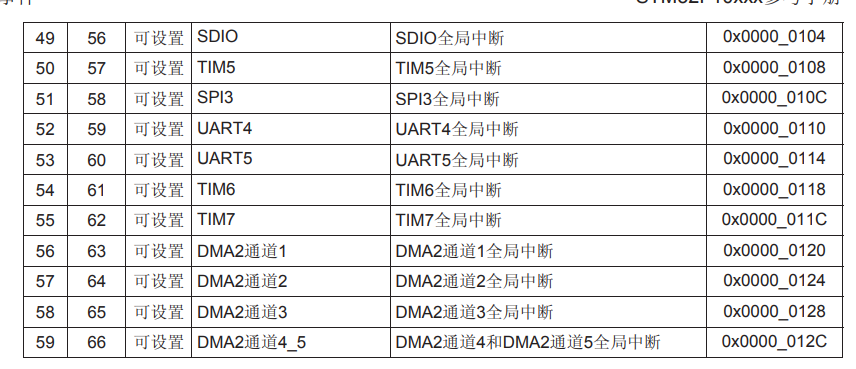

如上表所示,开发板上使用的STM32F103芯片支持60个可屏蔽中断通道(即上表中的0-59),和16个内核中断。

表中的位置栏,是指在同样优先级的顺序下,优先处理哪一个中断,数值越小,优先级越高。

表中的优先级栏是自然优先级,是指在没有设置的情况下的优先级。数值越小,优先级越高。可以看到,内核的复位中断,其优先级是-3,表明是最高优先级。而通常写程序中断时,都会配置。

表中的优先级类型就是写程序时可以自己配置的,可以看到,绝大多数中断源都是可以自己配置中断优先级的。

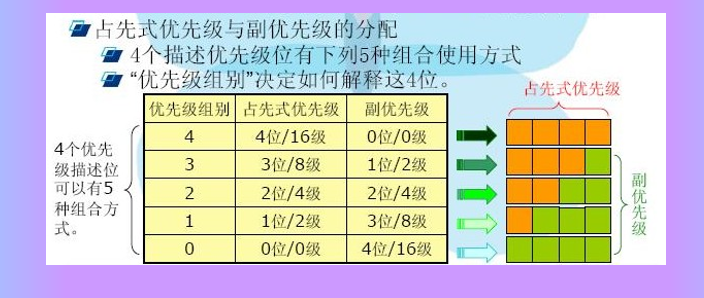

这些可设置中断优先级的中断源,每个都有一个8位的中断优先级控制寄存器,但是在实际中只使用了4位。

而这4位又可以配置5种组合方式如下

以图中的优先级组别2组为例,4位的高两位分成占先式优先级,两位就可以分成4级。同理,副优先级也占了2位,也有4级。

现在假定有两个中断,比如上表中的TIM6和TIM7,当他们都向CPU发出中断请求时,CPU将怎样决定先进入哪一个中断服务程序?

很简单,首先比较这两个中断的占先式优先级的,看哪一个的占先式优先级的数值更小,就先执行哪个。

甚 至就算CPU正在执行一个中断,只要新的中断的占先式优先级的数值更小,它就会先执行这个新的中断,这个就是中断的嵌套。

无论是CPU正执行一个中断而来了一个新的中断,还是CPU没有执行中断而新来了两个中断,只要两个中断的占先式优先级相同,那么都不会发生中断的嵌套。

如果占先式优先级相同,就比较两个同时到达的中断的副先级(又叫响应式优先级),先运行副先级更高的中断。

如果如果占先式优先级相同,两个副先级虽然不同的中断,先后到达,那么先运行先到达的中断,后面的中断到来后,就算其副先级更高,也不能抢断,只能等到前面中断运行后再运行。

如果占先式优先级和副先级都相同中断进行比较,就根据上表中的位置(其实就是自然优先级)顺序来决定。

以上理清逻辑关系,其实并不复杂~