SRAM(Static Random-Access Memory)

静态随机存取存储器(Static Random-Access Memory,SRAM)是随机存取存储器的一种。所谓的“静态”,是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。相对之下,动态随机存取存储器(DRAM)里面所储存的数据就需要周期性地更新。然而,当电力供应停止时,SRAM储存的数据还是会消失(被称为volatile memory),这与在断电后还能储存资料的ROM或闪存是不同的。

控制原理

STM32控制器芯片内部有一定大小的SRAM及FLASH作为内存和程序存储空间,但当程序较大,内存和程序空间不足时,就需要在STM32芯片的外部扩展存储器了。

扩展内存时一般使用SRAM和SDRAM存储器,但STM32F407系列的芯片不支持扩展SDRAM(STM32F429系列支持), 它仅支持使用FSMC外设扩展SRAM,我们以 SRAM为例讲解如何为STM32扩展内存。

给STM32芯片扩展内存与给PC扩展内存的原理是一样的,只是PC上一般以内存条的形式扩展,内存条实质是由多个内存颗粒(即SRAM芯片)组成的通用标准模块,而STM32直接与SRAM芯片连接。

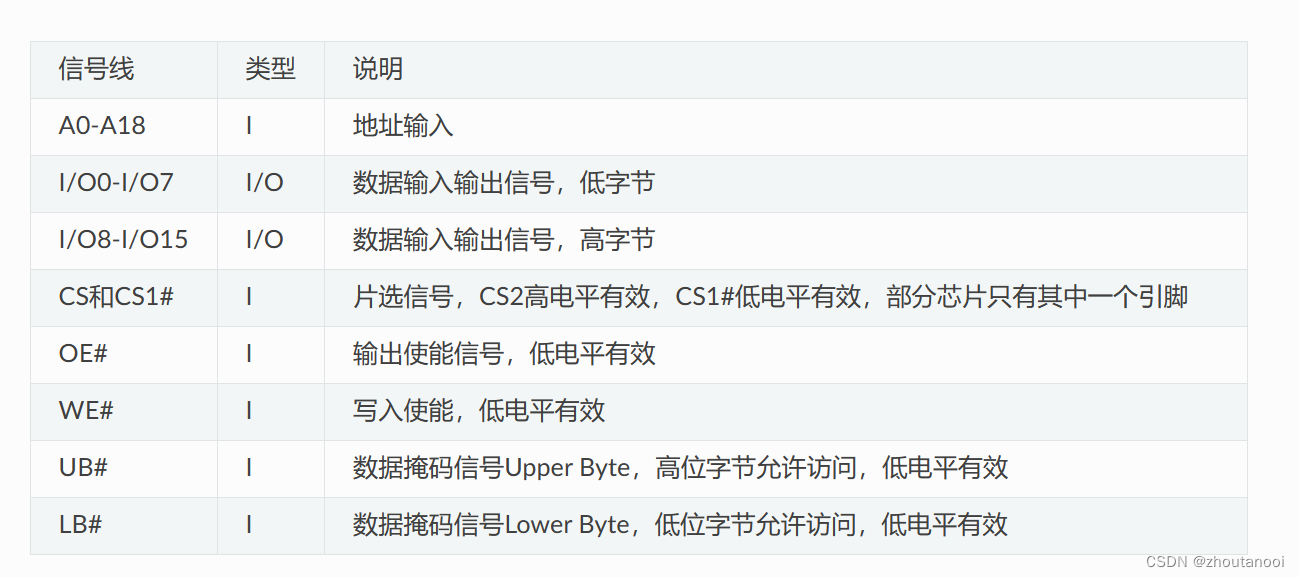

控制电路主要包含了片选、读写使能以及上面提到的宽度控制信号UB#和LB#。利用CS2或CS1#片选信号,可以把多个SRAM芯片组成一个大容量的内存条。OE#和WE#可以控制读写使能,防止误操作。

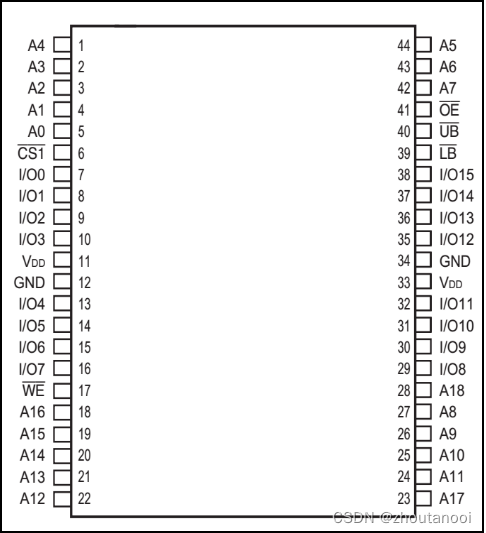

引脚描述

这是型号为IS62WV51216的SRAM芯片内部结构框图,以它为模型进行学习。

SRAM的控制比较简单,只要控制信号线使能了访问,从地址线输入要访问的地址,即可从I/O数据线写入或读出数据。

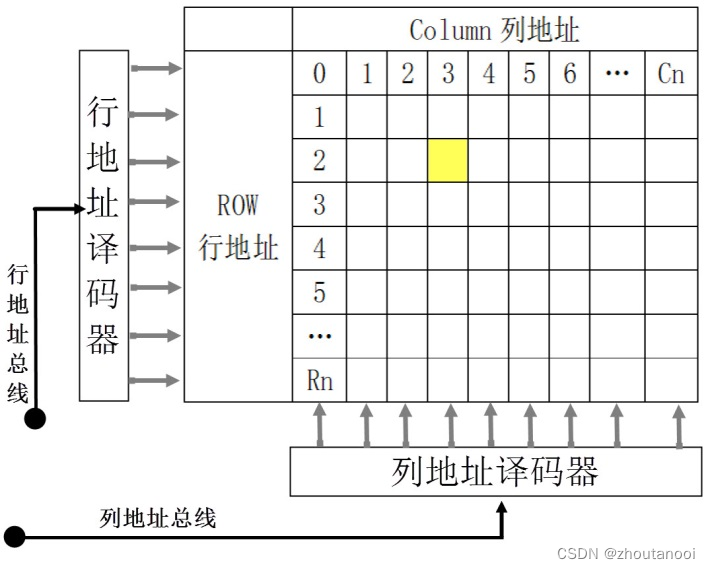

存储器矩阵

框图中标号处表示的是存储器矩阵,这个SRAM芯片的空间大小为512Kx16(bits)

SRAM内部包含的存储阵列,可以把它理解成一张表格,数据就填在这张表格上。和表格查找一样,指定一个行地址和列地址,就可以精确地找到目标单元格,这是SRAM芯片寻址的基本原理。这样的每个单元格被称为存储单元,而这样的表则被称为存储矩阵

地址译码器、列I/O及I/O数据电路

地址译码器把N根地址线转换成2N根信号线,每根信号线对应一行或一列存储单元,通过地址线找到具体的存储单元, 实现寻址。如果存储阵列比较大,地址线会分成行和列地址,或者行、列分时复用同一地址总线,访问数据寻址时先用地 址线传输行地址再传输列地址。本实例中的SRAM比较小,没有列地址线,它的数据宽度为16位,即一个行地址对应2字节空间,框 图中左侧的A0-A18是行址信号,18根地址线一共可以表示218=28x1024=512K行存储单元,所以它一 共能访问512Kx16bits大小的空间。访问时,使用UB#或LB#线控制数据宽度,例如,当要访问宽度为16位的数据时,使用行地 址线指出地址,然后把UB#和LB#线都设置为低电平,那么I/O0-I/O15线都有效,它们一起输出该地址的16位数据(或者接收16 位数据到该地址);当要访问宽度为8位的数据时,使用行地址线指出地址,然后把UB#或LB#其中一个设置为低电平,I/O会对 应输出该地址的高8位和低8位数据,因此它们被称为数据掩码信号。