基于EBAZ4205矿板的图像处理:02生成测试彩条图像

生成测试彩条图像可以有两种方式

VDMA缓存PS端生成彩条图像数据,PL端输出

这里可以直接看超级大电工开源的代码,写的很好详细,我就不再班门弄斧了(下面是链接)

EBAZ4205 第二十四个工程 用VDMA模块来缓存图像并在HDMI上显示(一)800X600分辨率测试

verilog生成彩条图像数据,PL端输出

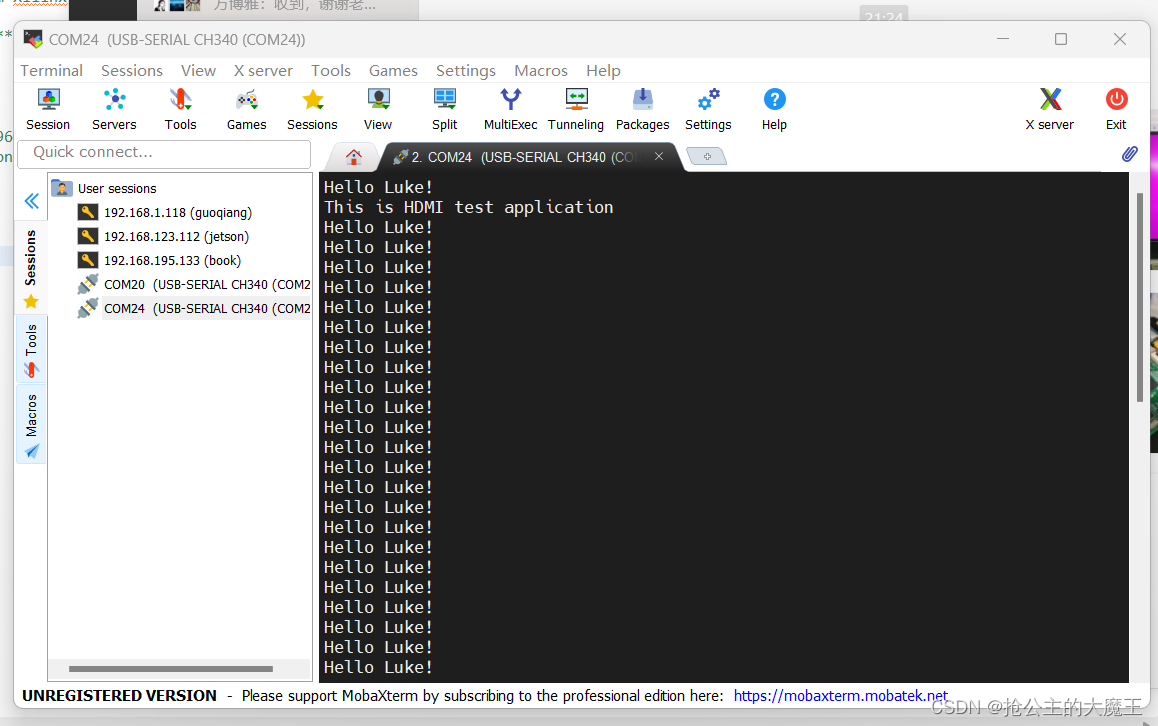

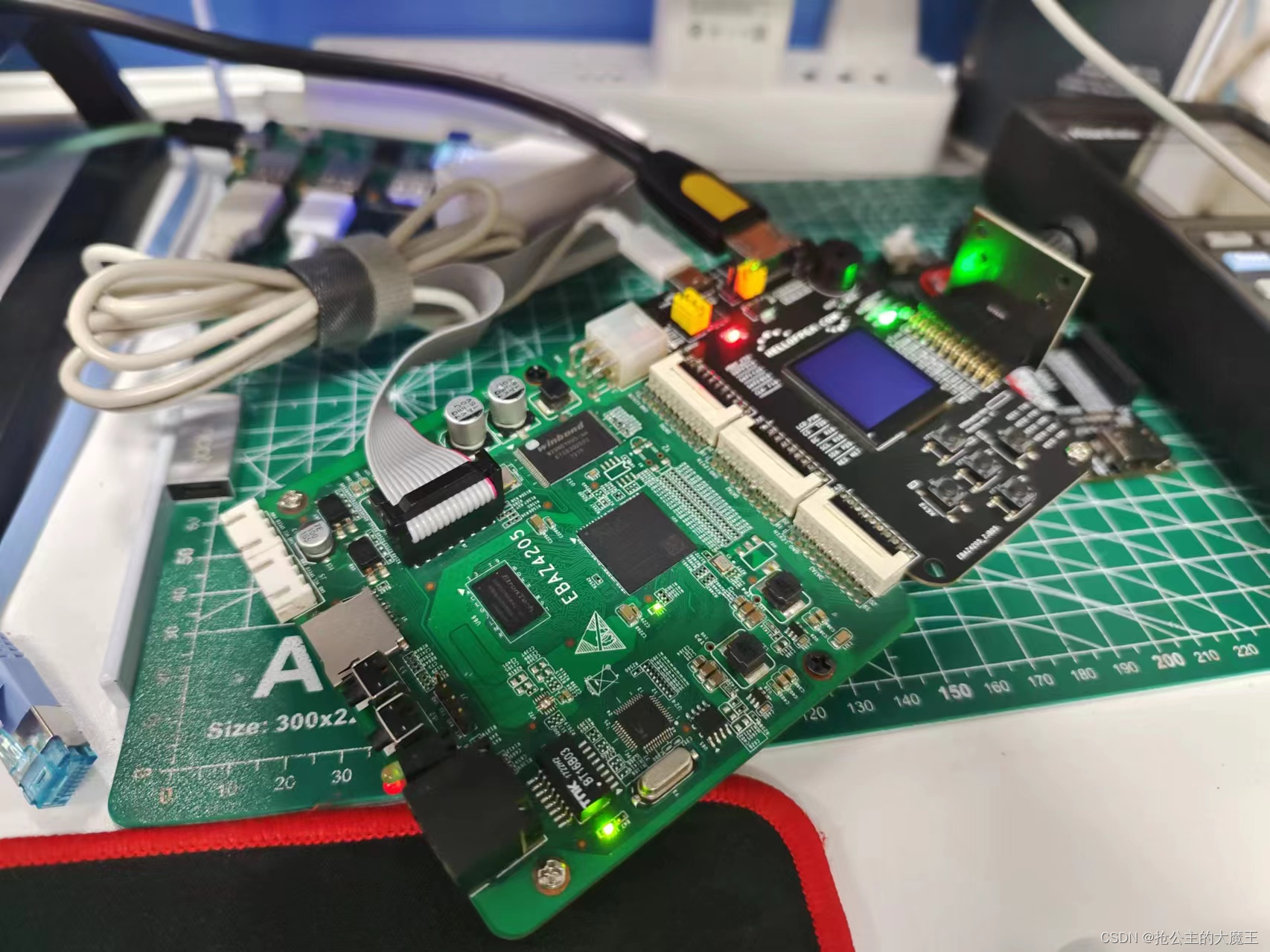

先看效果

项目讲解

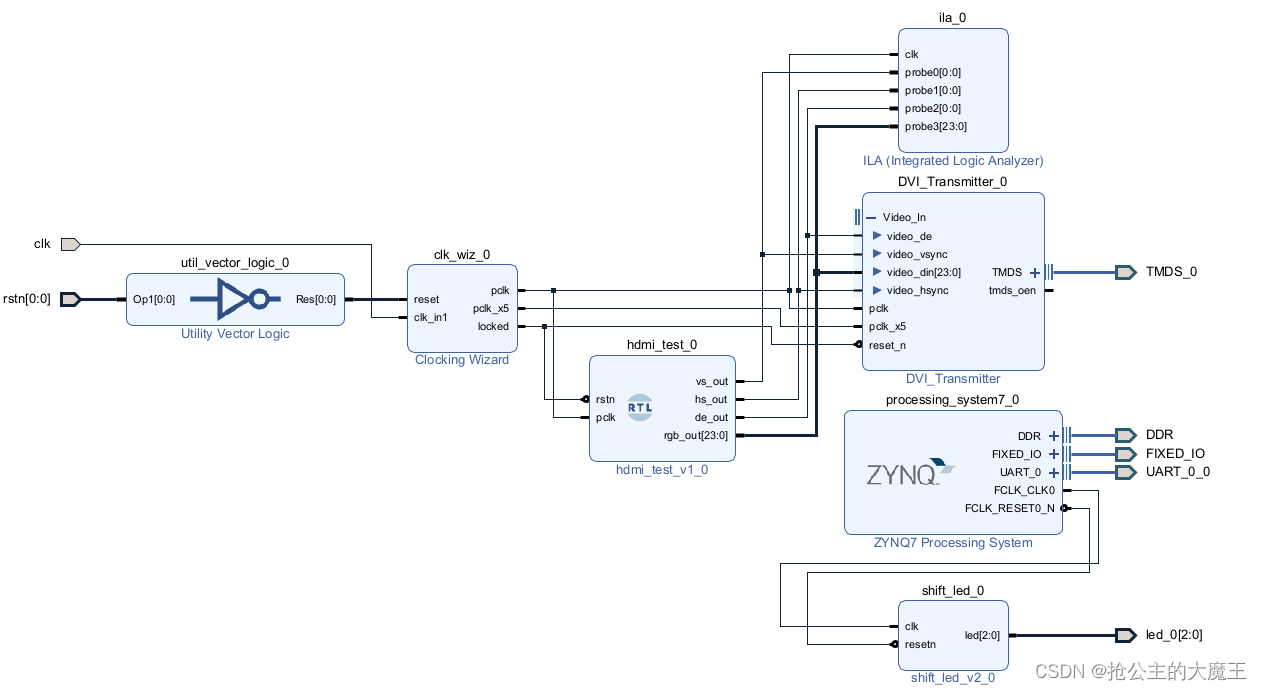

采用的是纯PL端的方案,PS只是用来点灯和uart打印了

下面是block design

时钟和复位,我用的都是片外的,实测用PS端生成的也可以,甚至那个clock wizard不用,时钟全都由PS生成也可以。

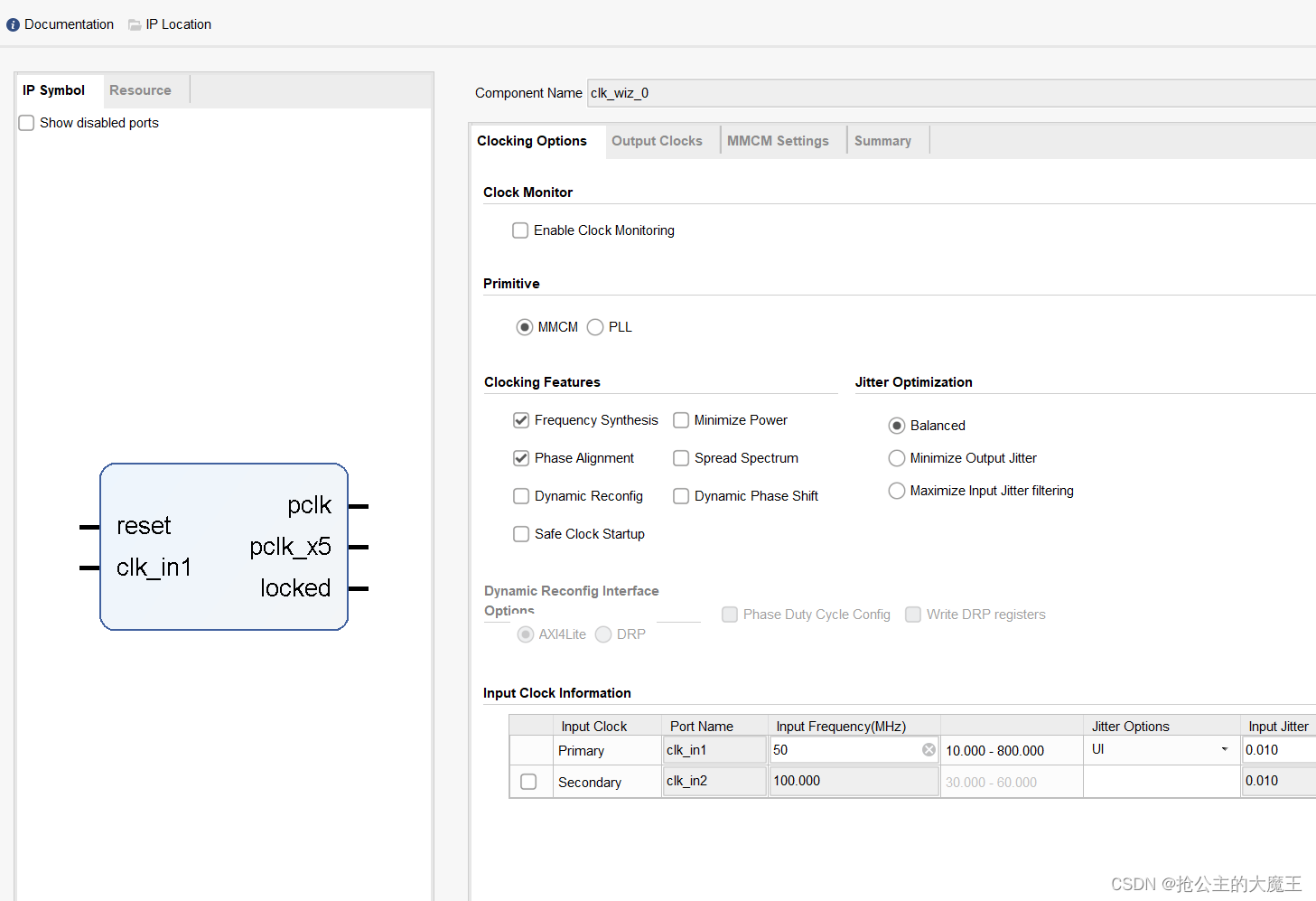

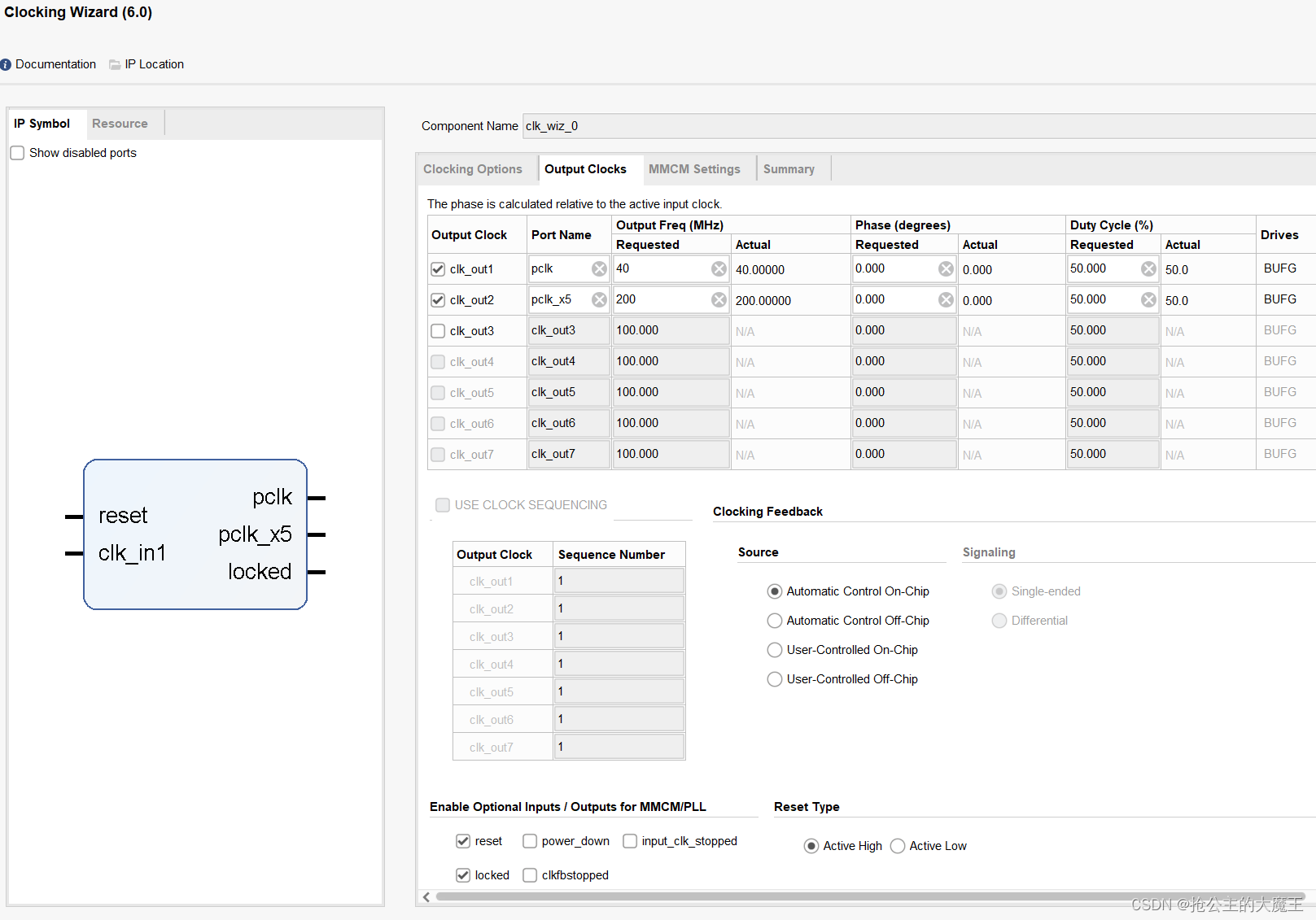

clock wizard的设置如下

这里根据800X600的分辨率设置了PCLK和PCLKX5。

在写这个项目之前,我有过疑惑,为啥他们都用的是800X600这种“远古”分辨率,老子要上1080P,但是实际写下来发现,clock wizard确实可以倍频到那么高的频率,但是生成的不准,timing约束时会报错。

所以我就老老实实的改成生成800X600分辨率了。

其他的就是HDMI_test模块了,它还包含了hdmi_timming_generator和hdmi_color_bar_generator模块,分别负责生成图像的行场同步信号和色彩数据。

代码

hdmi_test

`timescale 1ns / 1ps

`define UD #1

module hdmi_test(

input wire rstn ,

input pclk ,

output vs_out ,

output hs_out ,

output de_out ,

output [23:0] rgb_out

);

parameter X_WIDTH = 4'd12;

parameter Y_WIDTH = 4'd12;

//600p

parameter H_TOTAL = 12'd1056;

parameter H_ACT = 12'd800;

parameter H_FP = 12'd40;

parameter H_SYNC = 12'd128;

parameter H_BP = 12'd88;

parameter HV_OFFSET = 12'd0;

parameter V_TOTAL = 12'd628;

parameter V_ACT = 12'd600;

parameter V_FP = 12'd1;

parameter V_SYNC = 12'd4;

parameter V_BP = 12'd23;

wire [X_WIDTH - 1'b1:0] act_x ;

wire [Y_WIDTH - 1'b1:0] act_y ;

wire hs ;

wire vs ;

wire de ;

reg [3:0] reset_delay_cnt;

wire [7:0] r_out;

wire [7:0] g_out;

wire [7:0] b_out;

assign rgb_out = {r_out,g_out,b_out};

hdmi_timming_generator #(

.X_BITS ( X_WIDTH ),

.Y_BITS ( Y_WIDTH ),

.V_TOTAL ( V_TOTAL ),

.V_FP ( V_FP ),

.V_BP ( V_BP ),

.V_SYNC ( V_SYNC ),

.V_ACT ( V_ACT ),

.H_TOTAL ( H_TOTAL ),

.H_FP ( H_FP ),

.H_BP ( H_BP ),

.H_SYNC ( H_SYNC ),

.H_ACT ( H_ACT )

) hdmi_timming_generator1

(

.clk ( pclk ),

.rstn ( rstn ),

.vs_out ( vs ),

.hs_out ( hs ),

.de_out ( de ),

.x_act ( act_x ),

.y_act ( act_y )

);

hdmi_color_bar_generator #(

.COCLOR_DEPP ( 8 ),

.X_BITS ( X_WIDTH ),

.Y_BITS ( Y_WIDTH ),

.H_ACT ( H_ACT ),

.V_ACT ( V_ACT )

) // Number of fractional bits for ramp pattern

hdmi_color_bar_generator1 (

.rstn ( rstn_out ),

.pix_clk ( pclk ),

.act_x ( act_x ),

// input video timing

.vs_in ( vs ),

.hs_in ( hs ),

.de_in ( de ),

// test pattern image output

.vs_out ( vs_out ),

.hs_out ( hs_out ),

.de_out ( de_out ),

.r_out ( r_out ),

.g_out ( g_out ),

.b_out ( b_out )

);

endmodule

hdmi_timming_generator

`timescale 1ns / 1ps

`define UD #1

module hdmi_timming_generator # (

parameter X_BITS=4'd12,

parameter Y_BITS=4'd12,

parameter V_TOTAL = 12'd750,

parameter V_FP = 12'd5,

parameter V_BP = 12'd20,

parameter V_SYNC = 12'd5,

parameter V_ACT = 12'd720,

parameter H_TOTAL = 12'd1650,

parameter H_FP = 12'd110,

parameter H_BP = 12'd220,

parameter H_SYNC = 12'd40,

parameter H_ACT = 12'd1280

)(

input clk,

input rstn,

output reg vs_out,

output reg hs_out,

output reg de_out,

output reg [X_BITS-1:0] x_act,

output reg [Y_BITS-1:0] y_act

);

// parameter HV_OFFSET = 12'd0 ;

reg [X_BITS-1:0] h_count = 'd0;

reg [Y_BITS-1:0] v_count = 'd0;

always @(posedge clk)

begin

if (!rstn)

h_count <= `UD 0;

else

begin

if (h_count < H_TOTAL - 1)

h_count <= `UD h_count + 1;

else

h_count <= `UD 0;

end

end

always @(posedge clk)

begin

if (!rstn)

v_count <= `UD 0;

else

if (h_count == H_TOTAL - 1)

begin

if (v_count == V_TOTAL - 1)

v_count <= `UD 0;

else

v_count <= `UD v_count + 1;

end

end

always @(posedge clk)

begin

if (!rstn)

hs_out <= `UD 4'b0;

else

hs_out <= `UD ((h_count < H_SYNC));

end

always @(posedge clk)

begin

if (!rstn)

vs_out <= `UD 4'b0;

else

begin

if (v_count == 0)

vs_out <= `UD 1'b1;

else if (v_count == V_SYNC)

vs_out <= `UD 1'b0;

else

vs_out <= `UD vs_out;

end

end

always @(posedge clk)

begin

if (!rstn)

de_out <= `UD 4'b0;

else

de_out <= (((v_count >= V_SYNC + V_BP) && (v_count <= V_TOTAL - V_FP - 1)) &&

((h_count >= H_SYNC + H_BP) && (h_count <= H_TOTAL - H_FP - 1)));

end

always @(posedge clk)

begin

if (!rstn)

x_act <= `UD 'd0;

else

begin

if(h_count > (H_SYNC + H_BP - 1'b1))

x_act <= `UD (h_count - (H_SYNC + H_BP));

else

x_act <= `UD 'd0;

end

end

always @(posedge clk)

begin

if (!rstn)

y_act <= `UD 'd0;

else

begin

if(v_count > (V_SYNC + V_BP - 1'b1))

y_act <= `UD (v_count - (V_SYNC + V_BP));

else

y_act <= `UD 'd0;

end

end

endmodule

hdmi_color_bar_generator

`timescale 1ns / 1ps

`define UD #1

module hdmi_color_bar_generator # (

parameter COCLOR_DEPP=8,

parameter X_BITS=13,

parameter Y_BITS=13,

parameter H_ACT = 12'd1280,

parameter V_ACT = 12'd720

)(

input rstn,

input pix_clk,

input [X_BITS-1:0] act_x,

input vs_in,

input hs_in,

input de_in,

output reg vs_out,

output reg hs_out,

output reg de_out,

output reg [COCLOR_DEPP-1:0] r_out,

output reg [COCLOR_DEPP-1:0] g_out,

output reg [COCLOR_DEPP-1:0] b_out

);

localparam H_ACT_ARRAY_0 = H_ACT/8;

localparam H_ACT_ARRAY_1 = 2* (H_ACT/8);

localparam H_ACT_ARRAY_2 = 3* (H_ACT/8);

localparam H_ACT_ARRAY_3 = 4* (H_ACT/8);

localparam H_ACT_ARRAY_4 = 5* (H_ACT/8);

localparam H_ACT_ARRAY_5 = 6* (H_ACT/8);

localparam H_ACT_ARRAY_6 = 7* (H_ACT/8);

localparam H_ACT_ARRAY_7 = 8* (H_ACT/8);

always @(posedge pix_clk)

begin

vs_out <= `UD vs_in;

hs_out <= `UD hs_in;

de_out <= `UD de_in;

end

always @(posedge pix_clk)

begin

if (de_in)

begin

if(act_x < H_ACT_ARRAY_0)

begin

r_out <= 8'hff;

g_out <= 8'hff;

b_out <= 8'hff;

end

else if(act_x < H_ACT_ARRAY_1)

begin

r_out <= 8'hff;

g_out <= 8'hff;

b_out <= 8'h00;

end

else if(act_x < H_ACT_ARRAY_2)

begin

r_out <= 8'h00;

g_out <= 8'hff;

b_out <= 8'hff;

end

else if(act_x < H_ACT_ARRAY_3)

begin

r_out <= 8'h00;

g_out <= 8'hff;

b_out <= 8'h00;

end

else if(act_x < H_ACT_ARRAY_4)

begin

r_out <= 8'hff;

g_out <= 8'h00;

b_out <= 8'hff;

end

else if(act_x < H_ACT_ARRAY_5)

begin

r_out <= 8'hff;

g_out <= 8'h00;

b_out <= 8'h00;

end

else if(act_x < H_ACT_ARRAY_6)

begin

r_out <= 8'h00;

g_out <= 8'h00;

b_out <= 8'hff;

end

else

begin

r_out <= 8'h0;

g_out <= 8'h0;

b_out <= 8'h0;

end

end

else

begin

r_out <= 8'h00;

g_out <= 8'h00;

b_out <= 8'h00;

end

end

endmodule