pcie协议复位共有4中情况;cold reset;warm reset;hot reset;function level reset;

分类:

依据spec 6.6:

Conventional reset(传统复位):cold,warm,hot, reset;所有pcie 内部的寄存器必须恢复到复位状态;

按照复位方式:cold,warm,必须通过pcie复位信号#PERST信号复位;该信号通常接金手指上用于ep和rc链接;

in-band 复位:hot reset;function level reset(FLR);

Fundamental Reset:cold,warm reset;

当fundamental reset建立之后:RX为高阻态;TX输出短路电流;TX端电压为共模电压;

复位释放之后LTSSM从新开始训练;

cold reset:

power up复位;

warm reset:

除power up之外其他情况控制了#PERST复位(如通过内部寄存器等);

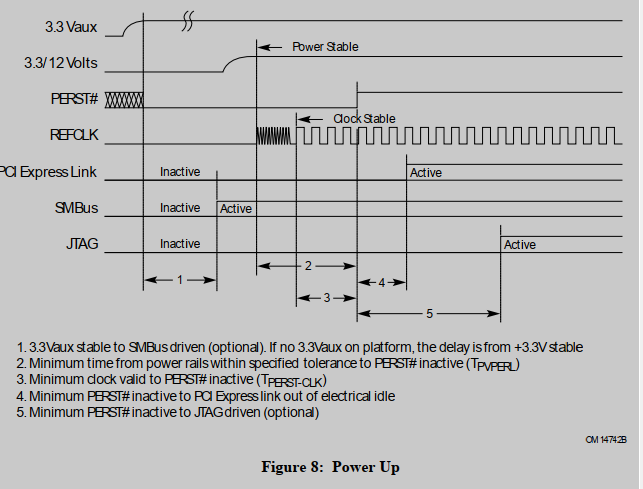

两者主要区别是复位保持时间的区别,以S IP为例在refclk稳定之后cold reset最小保持10us;而warm reset 保持时间为最小100ns;在CEM文档中说明了Tpvperl必须最小100ms;

即图中2处的时间;

hot reset:

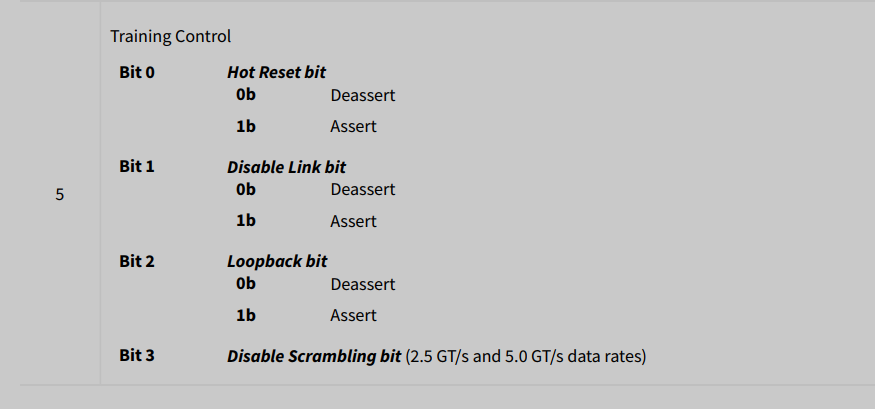

TS1 order set中Hot reset bit为1;

一:有上层(app layer)控制发起hot reset:

- 如果任意lane中接收到两个连续的TS1的order set;hot reset bit Assert;之后开始进入hot reset流程:(4.2.6.11 hot reset)

- linkup=0;

- 如果没有继续保持hot reset;之后Ltssm会进入到detect;

- 否则会继续发送TS1系列,带hot reset信息

2.所有tx lane中TS1 hot reset bit都为1;

3. 2ms后超时,自动回退到Detect状态;

二:没有上层控制(通常指接收侧,如收到两个连续的Ts1 hot reset bit被置位)

1.linkup=0;

2. 当SW 的USP任意lane 端口接收到两个连续的TS1 hot reset assert;其所有下行端口都开始发送TS1 hot reset assert;

- 任意两个crosslink不受该约束影响;

3. 当任意已配置lane收到两个连续的TS1 hot reset bit assert;会进入到Hot reset状态;且内部2ms计数器开始计数;

4. 2ms后超时,自动回退到Detect状态;

注:在S IP中操作对端进入hot reset方法:

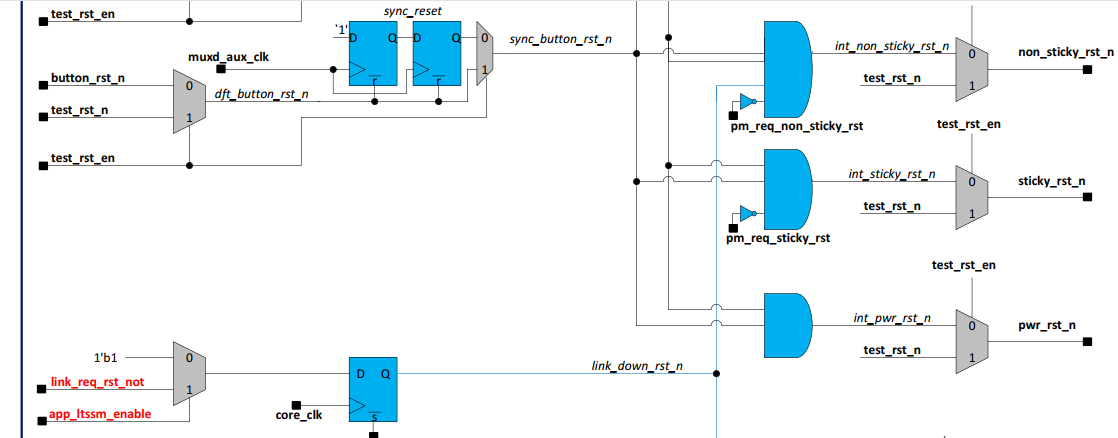

DSP可以hot reset USP;通过拉高app_init_rst 信号DSP会发送两个连续的TS1 hot reset bit assert; 并且会输出一个link_req_rst_not 信号用于指示复位信号(低有效);且该信号还会引起non_sticky_rst_n;以及int_phy_rst_n的复位;

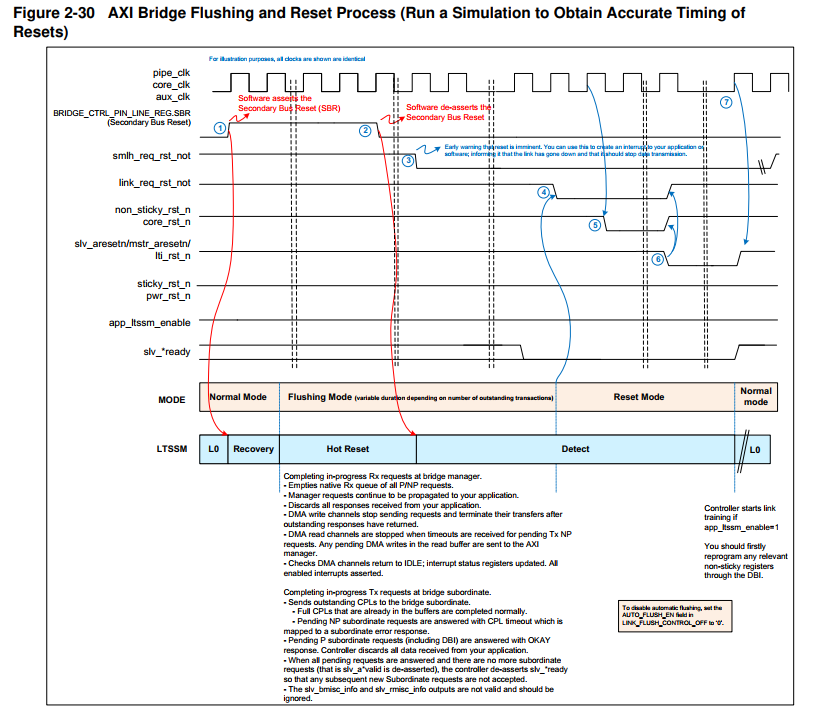

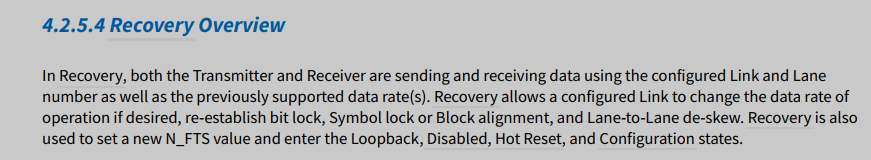

带axi端口的流程;需要将rx 数据flush;LTSSM会从L0状态跳转到Recovery之后进入到hot reset;

FLR reset:

flr reset不会复位:

1.sticky reg(非sticky reg会被复位)

2. HwInit 类型reg(硬件初始化reg)

FLR:非sr-iov可选;支持sr-iov必选;

使用方式:

DSP:无

USP:

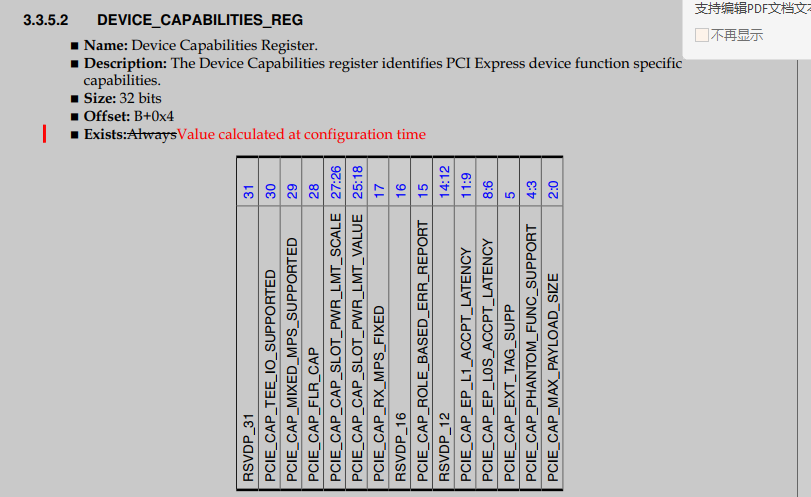

device_capabilities_reg bit28为1,表示支持FLR;

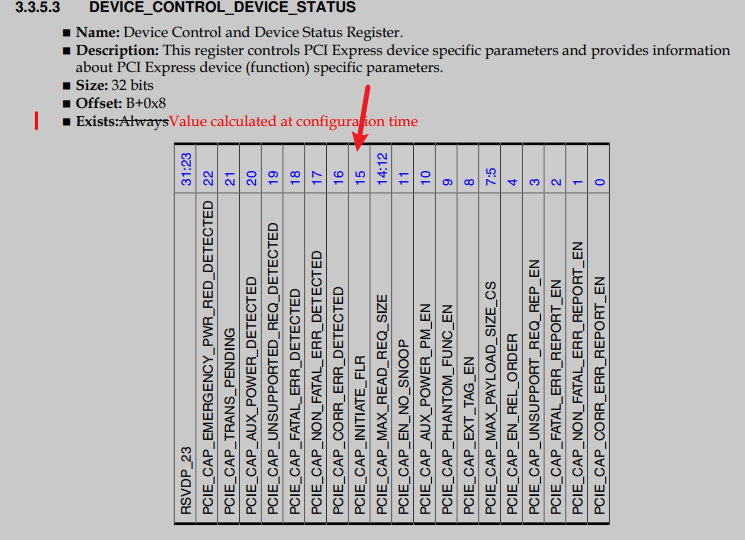

device_control_device_status;bit15写1开始进行usp的function level reset;写1清0该bit。

注:有些内容是英译过来的。建议去查看spec原文!!!!!!笔者写的也只是为了记录一下。