👉 写在前面

👉 本系列博客记录牛客网刷题记录

👉 日拱一卒,功不唐捐!

目录

题目描述

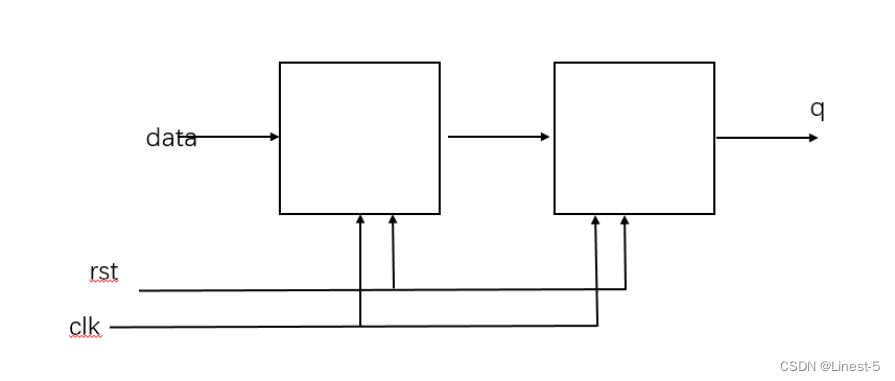

用verilog实现两个串联的异步复位的T触发器的逻辑,结构如图:

信号示意图:

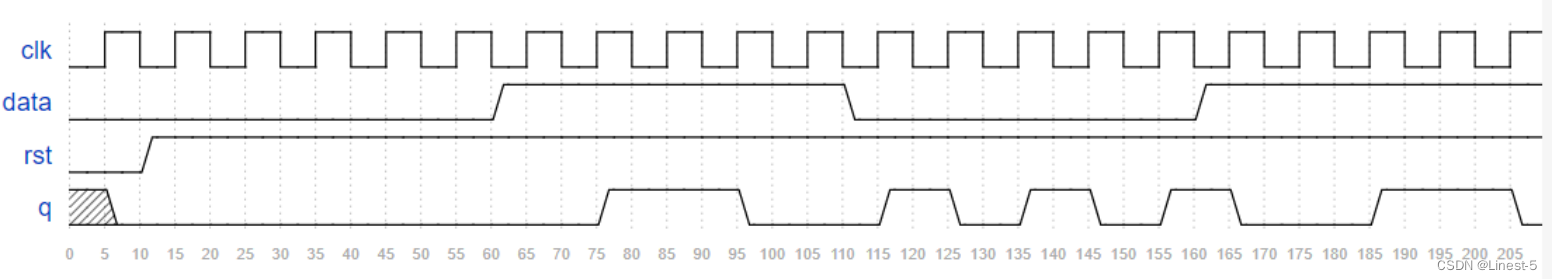

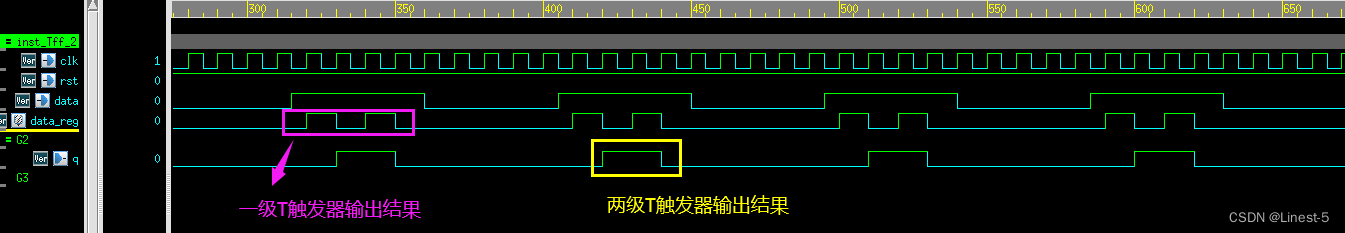

波形示意图:

输入描述:

输入信号 |

data |

clk |

rst |

类型 |

wire |

wire |

wire |

在 testbench 中,clk 为周期 5ns 的时钟,rst 为低电平复位

输出描述:

输出信号 |

q |

类型 |

reg |

题目分析

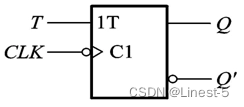

T 触发器

T 触发器是在数字电路中,凡在 CP 时钟脉冲控制下,根据输入信号 T 取值的不同,具有保持和翻转功能的触发器,即当 T=0 时能保持状态不变,当 T=1 时一定翻转的电路。

将 JK 触发器的输入端 J、K 连接在一起,作为输入端 T,就构成了 T 触发器。

T 触发器的特性方程

Qn+1 = T Qn ' +T ' Qn = T⊕Qn

(其中 Qn 为现态,Qn+1 为次态)

T触发器的特性表

T |

Q |

Q* |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

本题就是要实现两个 T 触发器串联,并且采用同源时钟且异步复位的形式。

Verilog 代码

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

// Engineer : Linest-5

// File : Tff_2.v

// Create : 2022-09-29 22:18:20

// Revise : 2022-09-29 22:18:22

// Module Name : Tff_2

// Description : 两个T触发器串联,T触发器的输出逻辑为 Q = D ^ Q

// Editor : sublime text3, tab size (4)

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

`timescale 1ns/1ps

module Tff_2(

input wire clk,

input wire rst, //低电平复位

input wire data,

output reg q

);

//*************code***********//

reg data_reg;

always @(posedge clk or negedge rst) begin

if (!rst) begin

data_reg <= 'd0;

q <= 'd0;

end

else begin

data_reg <= data ^ data_reg;

q <= data_reg ^ q;

end

end

//*************code***********//

endmoduletestbench 代码

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

// Engineer : Linest-5

// File : tb_Tff_2.v

// Create : 2022-09-29 22:20:30

// Revise : 2022-09-30 09:52:35

// Module Name :

// Description :

// Editor : sublime text3, tab size (4)

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

`timescale 1ns/1ps

module tb_Tff_2();

reg clk;

reg rst; //低电平复位

reg data;

wire q;

initial begin

clk = 'd1;

rst = 'd0;

data = 'd0;

#100

rst = 'd1;

#1000

$finish;

end

always #5 clk = ~clk;

always #45 data = ~data;

Tff_2 inst_Tff_2 (

.clk(clk),

.rst(rst),

.data(data),

.q(q)

);

//verdi

initial begin

$fsdbDumpfile("tb_Tff_2.fsdb");

$fsdbDumpvars(0);

end

endmodule

仿真结果

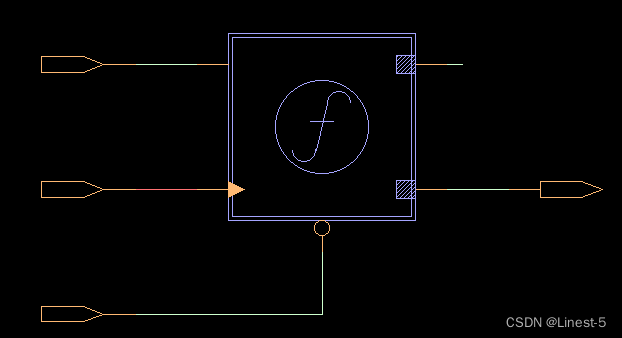

电路结构

仿真波形

经过两级 T 触发器,结果 q 输出与设计一致。

本文含有隐藏内容,请 开通VIP 后查看