1、流控机制

在数据发送过程中,发送者向接收者发送数据,通常需要接收者通知发送者自身是否可以接收数据,当接收者即将无法接收数据时(如FIFO快满时),发送者需要停止发送数据,这就是流控机制。

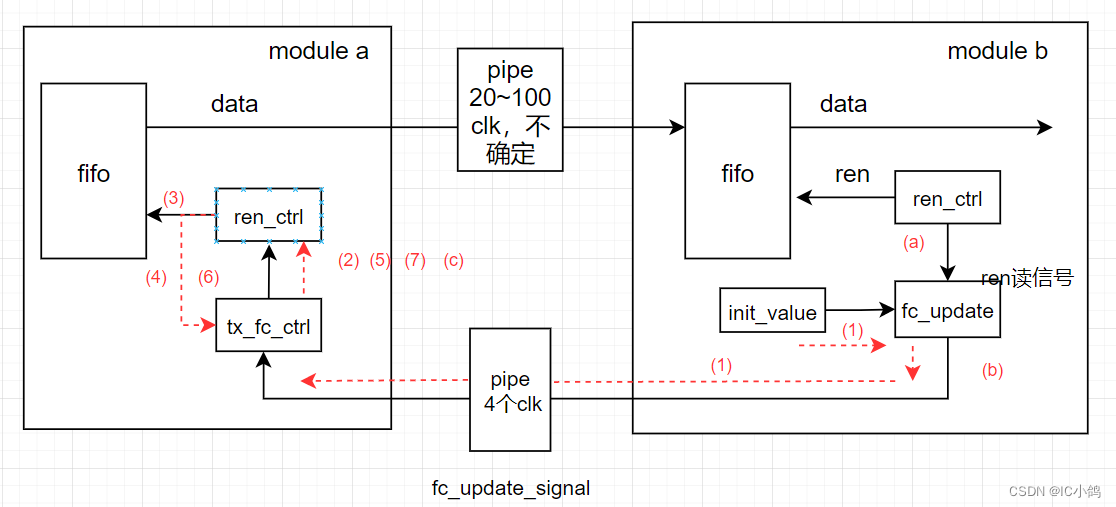

2、流控机制过程

初始化流程:

(1)复位释放后,初始化,module b 通过信号fc_update_signal 通知module a 自身fifo深度是多少

(2)Tx_fc_ctrl 收到初始化信息后,得知module b存在有效fifo 缓存,通知ren_ctrl允许产生读使能ren

(3)ren_ctrl产生读使能ren

(4)ren输出给tx_fc_ctrl,module b的有效fifo深度减一

(5)tx_fc_ctrl计算module b是否存在有效数据,有则允许ren_ctrl产生读使能

(6)ren_ctrl产生读使能ren,并通知到tx_fc_ctrl,module b的有效fifo深度减一

(7)tx_fc_ctrl计算module b是否存在有效数据,有则允许ren_ctrl产生读使能,没有则不允许ren_ctrl产生读使能

(a)Module b模块fifo已存在有效数据,从fifo读取一个数据,此时已释放出一个fifo深度

(b)Fc_update更新fc_update_signal,通知tx_fc_ctrl模块module b已释放一个fifo空间,tx_fc_ctrl记录的有效深度加1

(c)此时tx_fc_ctrl允许ren_ctrl产生读使能

3、特点说明

此种流控机制需要发送端和接收端配合管理有效缓存空间。相对比单一bit的flow ctrl信号来说,稍微复杂一些,但是有个显著的优点,相对于被动流控机制(见IC设计高级006:流控反压机制导致的路径延时),能够有效减少module b中的Data fifo的深度。

如图,data pipeline的深度是不确定的,可能是20~100个周期,而流控信号只有4个pipe,在考虑其他方面的延时有3拍,

不考虑性能的情况下:保证不溢出,module b的fifo深度最小需要:

本文流控机制:深度为1 ; 被动流控机制:深度为1+100+4+3

满足最大性能的情况下,保证下游不断流:module b的fifo深度需要:

本文流控机制: 100+4+3+1 ; 被动流控机制:2*(100+4+3+1)