声明

下面的题目作答都是自己认为正确的答案,并非官方答案,如果有不同的意见,可以评论区交流。

这些题目也是笔者从各个地方收集的,感觉有些题目答案并不正确,所以在个别题目会给出自己的见解,欢迎大家讨论。

题目

1.standard cell库中寄存器的D pin的setup required time 既可以是正值可以是负值()

答案:对

2.为了降低功耗,在某个状态下,对不关心的存器的输出值(即对系统运行没有影响的寄存器),优化的低功耗设计方法是将其固定为0或者1()

答案:错

解析:将其值保持不变,降低翻转。

3.关于时钟门控描述错误的是()

A模块级时钟门控可以手动例化

B代码书写风格(codingstyle)会影响时钟门控的插入

C插入时钟门控会导致静态功耗增加

D为降低动态功耗,应尽量多的插入时钟门控

答案:C

解析:门控时钟降低静态功耗

5.I2C协议采用推挽(push-pul)输出,输出1和输出0时分别由MOS管驱动输出高电平和低电平()

答案:错

解析:I2C协议采用开漏输出,输出1时由上拉电阻上拉为1。

6.有符号数右移需要使用哪种操作符()

解析:使用>>>进行算数右移,左侧扩位符号位n位,右侧删除n位即进行除n运算。

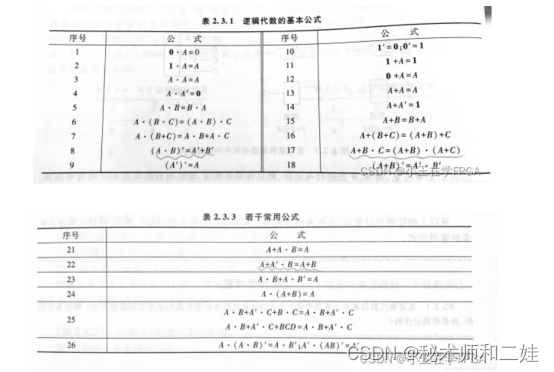

7.逻辑化简Y=ABC+AB+B C+BD结果为()

8.时序逻辑中case分支未写全时,可以不用加default分支()

答案:正确

解析:组合逻辑未写defalut会生成锁存器,时序逻辑不会。

9.在DC优化timing的时候,工具采用下面那个命令可以通过移动寄存器来达到调整时序优化的目的()

A. compile_ultra -retime

B. compile ultra -timing high effort

C.compile ultra -incremental

D.compile ultra -piple

在DC(Design Compiler)优化时,通过移动寄存器来进行时序优化的命令是:

A. compile_ultra -retime

选项A中的命令compile_ultra -retime用于启用寄存器重定位(retiming)操作,它会尝试重新安排逻辑和寄存器的位置,以改善时序性能。该命令会对设计进行全局的时序优化,并通过移动寄存器来调整时序。

选项B的命令compile ultra -timing high effort没有明确的指令来移动寄存器来达到调整时序优化的目的。该命令中的"-timing high effort"参数表示对时序约束进行更高的优化尝试。

选项C的命令compile ultra -incremental用于增量编译,它并不是针对移动寄存器进行时序优化的命令。

选项D的命令compile ultra -piple也不是用于移动寄存器的命令,它是用于进行流水线优化的命令。

因此,正确的选项是A. compile_ultra -retime。

10、下列不属于动态数组内建函数的是()

A.length() B.delete() C.new[] D.size()

答案:A

12.关于外设中断树说法错误的是()

A中断树结构便于中断源的管理

B中断树结构便于中断源的查询

C中断对可以挂接不可屏蔽中断

D中断树上所有中断节点都可以清除

答案:D

解析:硬件中断不可清除

13、一般来说,静态功耗受温度的影响很大,翻转功耗受温度影响不是很大()

答案:正确

解析:通常情况下,静态功耗(也称为漏电流功耗)确实受到温度的显著影响。当温度升高时,半导体材料中载流子(如电子和空穴)的活动增加,导致漏电流增大,因此静态功耗会随着温度的升高而增加。而翻转功耗(也称为动态功耗或切换功耗)主要由电路中的电荷和放电活动造成,与电路的操作频率、电容负载以及供电电压有关。虽然温度的变化也会影响电子器件的特性,例如电容的变化,从而间接影响翻转功耗,但相比静态功耗,温度对翻转功耗的影响通常较小。动态功耗主要与电路中的活动量相关,例如时钟频率和逻辑切换频率

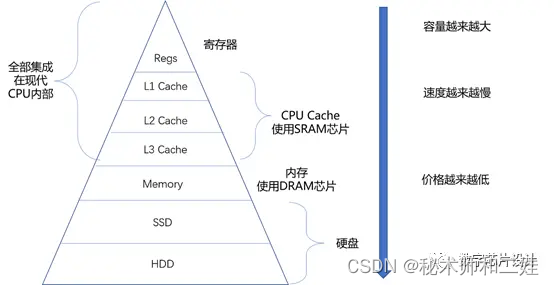

14、下列速度最快的存储器件是()

A.DDR SDRAM

B.SRAM

C.Register File

D.NVME SSD

答案:C

15.CPU Load访问L1 Cache hit平均时延为2-cycle,Miss率为5%,L2 Cache hit平均延时为40-cycle;假设L2 Cache Hit率为100%,那么CPU的100个Load指令的平均时延是多少? ()

A.4.5 cycle

B.2 cycle

C.3 cycle

D.3.9 cycle

答案:D

解析:CPU load指令为访问外部存储器指令,若是存储器的数据已经缓存在cache中,则可以直接访问高速的cache,这称为命中hit。100个load指令,有5%没有命中L1cache,但是命中了L2cache;因此100个load指令的总时延为:295+405=390(cycle),平均时延=390/100=3.9(cycle)

16、

reg [1:0] a;

wire [1:0] b[2:0];

integeri;

assign b[0] = 2'b00;

assign b[1]= 2b01;

assign b[2] = 2'b10;

always@(*)begin

a=2'b11;

for (i=0:i<3;i=i+1) begin

if (i>0)

a=b[i];

end

end

a的输出值为()

A2b10

B.2b01

C.2b11

D.2b00

答案:A

解析:阻塞赋值,最后赋值2’b10

17、十进制负整数-10的8bit补码表示正确的是? ()

A.8h76

B.8hF6

C.8hF5

D.8hA

答案:B

解析:符号位不变,其余位按位取反+1,源码8’b10001010,补码8’b11110110

18、以下关于异步处理的说法正确的是()

A.多bit数据信号处理可以用“打3拍”的方式

B时钟域A的3个单bit信号可以分别同步到时钟域B后再做组合处理;

C时钟域A的3个单bit信号不能分别同步到时钟域B后再做组合处理

D每个时钟周期跳变的数据信号可以用dmux的方式实现异步处理

答案:C

解析:A:多bit打拍会由于不同bit的布线延时,出现亚稳态。D:DMUX要求数据在采样时钟域未完成采样,即valid持续几个时钟周期,等待采样时钟域采样。

19、DC综合过程中,GTECH网表是在那个过程中产生的()

A.mapping

B.translate

C.optimization

D. write file

答案:B

解析:DC综合分为:translate,mapping,optimization。translate将RTL编译为GTECH门级网表,mapping将门级网表映射到对应的工艺库。

21、关于宏定义说法正确的是()

A综合时不同文件列表内的宏定义仅在本列表生效

B宏定义最好在各文件中随用随定义

C宏定义会覆盖,不需要单独undef

D仿真时出现宏定义冲突以最后一次值为准

答案:D

22、以下哪个表示的工艺最快?()

A.TT

B.SS

C.FF

D FS

答案:C

解析:FF:fast PMOS fast NMOS。

23、$signed(4b1011)>>>2的值为()

A.4b0011

B.4b0010

C.4b1110

D.4b1100

答案:C

解析:有符号数使用逻辑右移,高位补符号位。

24.同步复位说法错误的是()

A.同步复位的电路逻辑可能产生毛刺,毛刺会作用于触发器产生误复位

B.要求复位时间足够长,至少为最大时钟周期+相关组合逻辑延过

C.对时钟有依赖,难以对整芯片电路进行全局复位控制

D.100%同步时序电路,频率高

答案:A

解析:同步复位不易产生毛刺,但是必须等待时钟上升沿才会有效。异步复位若是在时钟上升沿进行释放,则会产生毛刺,造成亚稳态

25.input signed[3:0]a,b;代表()

A.ab均为4bit有符号数

B.a为4bit有符号数,b为1bit无符号数

C.a为4bit有符号数,b为4bit无符号数

D.a为4bit有符号数,b为1bit有符号数

答案:A

26、不能使用std::randomize()对于非rand类型的变量进行随机()

答案:错误

不止rand,randc,常规变量都可以,可以看一下ieee sv1800-1200中18.12节内容

27、随着器件的阈值电压增大,器件的延时将(),漏电流功耗将()

A.增大,减小

B.增大,增大

C.减小,减小

D.减小,增大

答案:A

解析:阈值电压越大,信号翻转越慢,器件延时越大,静态功耗减小。

28.时序逻辑中,所有if都必须要有else语句对应,以避免产生latch,且有助于综合(Design CompleDC)自动插icg,降低寄存器反转率()

答案:错误

解析:时序逻辑中if不写else不会生成latch,并且有助于综合器自动插入门控时钟(推荐写法)。组合逻辑if必须写else,不然会生成latch。

29、PLL锁定指的是()

A.VCO输出的时钟频率不再发生变化

B.VCO不再震荡

C.VCO输出的时钟相位不再发生变化

D.输入时钟与反馈时钟的频率和相位差稳定

答案:D

30、dc shell> create clock -name CLK -period 20 -waveform(10 18)以上命令的时钟周期为 (A)

A.20ns

B.18ns

C.28ns

D.10ns

答案:A

解析:period后面跟的时钟周期。Waveform(10 18),代表第一个上升沿在第10ns周期到来,第一个时钟下降沿在第18ns到来。即定义了占空比为40%,周期为20ns的时钟。

31、以下对verilog中任务的描述哪些是正确的 ()

A.任务中可以直接赋值和采样全局信号

B.任务调用中的输出和输入参数必须是寄存器类型

C.任务定义中可以包含时延控制

D.一个任务也可以调用其他任务和函数

答案:ABCD

32、对于无复位寄存器的使用,描述正确的是 ()

A.相比于同步复位寄存器面积有收益,但功耗会恶化

B.可以在状态机中使用以减少翻转功耗

C.通常在datapath上使用

D.相比于异步复位寄存器面积和功耗均有收益

答案:BCD

33、关于dmux同步,以下说法正确的是 ()

A.DMUX做异步处理的时候,要考虑两侧时钟的频率差异,确保各种频率范围下,DMUX的数强采样信号都采样到数据稳定的窗口

B.DMUX不需要care两侧的时钟频率关系

C.利用DMUX电路结果做异步处理时,valid信号要符合单bit同步信号要求,同步的数据要保持缓变,并被同步信号正确采样

D.DMUX的输入数据信号是跨异步时钟域的,STA不会检查异步路径的tming,设计上可以保证采样时信号是稳定的。

答案:ACD

34、关于12C协议描述错误的是()

A.I2C的master与slave之间只能采用一对一的联接方式

B.12C的上拉电阻越小,能支持的速度越快

C.挂在同一条12C总线上的12C从设备地址不能相同

D.12C的上拉电阻越大,能支持的速度越快

解析:I2C协议可以多主多从。

答案:AD

35、以下关于存储管理单元MMU的描述正确的是()

A.MMU可以控制Master访问Memory 的权限

B.MMU可以完成虚拟地址到物理地址的转换

C.一个物理地址只能被映射到一个虚拟地址

D.MMU的页表本身只能通过物理地址访问

答案:AB

解析:D。MMU负责总线的仲裁,虚拟地址到物理地址的转换。MMU的页表本身只能通过虚拟地址访问

36、8hAA相同的数值表示方式有?()

A.8d180

B.8d170

C.8o252

D.8b10101010

答案:BCD

37、关于异步复位同步释放,正确的是()

A.复位生效的时候,复位信号不受时钟信号的影响

B.复位生效的时候,复位信号受时钟信号的影响

C.复位释放的时候,复位信号不受时钟信号的影响

D.复位释放的时候,复位信号受时钟信号的影响

答案:AD

38针对Specify语句(posedge clock =>(out +in))=(8,10)如下描述正确的是()

A时钟上升沿到输出的最大延时是10

B.时钟上升沿到输出的最小延时是8

C.时钟上升沿到输出高变低延时是10

D.时钟上升沿到输出低变高延时是8

答案:CD

题属于边沿敏感路径,(out+in)表示的是从in到out的数据路径是同向的,(8,10)表示的是在clk上升沿,clk到out的路径上升延迟为8,下降延迟为10.参考菜鸟教程中的verilog教程

//在 clk 上升沿,从 clk 到 out 的路径上升延迟为 1,下降延迟为 2

//从 in 到 out 的数据路径是同向的,即 out = in

(posedge clk => (out +: in)) = (1,2);

//在 clk 下降沿,从 clk 到 out 的路径上升延迟为 1,下降延迟为 2

//从 in 到 out 的数据路径是反向的,即 out = ~in

(negedge clk => (out -: in)) = (1,2);

//clk 任意变化时,从 clk 到 out 的路径上升延迟为 1,下降延迟为 2

//从 in 到 out 的数据路径是不可以预知的,同向、反向或不变

(negedge clk => (out : in)) = (1,2);

39、添加断言的作用主要包含以下哪些方面:()

A.关键节点添加assertion,帮助设计人员迅速找到代码出错点,提高问题定位的效率

B.部分bug需要累积效应才会暴露,验证环境难以构造足够长时间的用例中击出来,通过assehion来保证这种问题在第一次发生时便被发观

C.增加覆盖率的检查,保证自己希望冲击的场景都被冲击到。

D.复杂逻辑中添加assertion,增加微观检查,做补充验证,相当于验证的白盒检查

答案:ABCD

40、改善亚稳态的措施()

A.使用反应更快的寄存器,减少建立保持时间

B.使用同步机制,防止亚稳态传播

C.降低数据变化频率

D.降低采样时钟频率

答案:ABD