目录

2.2 Serial Data Input, Output and IOs (DI, DO and IO0, IO1, IO2, IO3)

5.2.3 BP2, BP1, BP0 (S2-S3-S4)

概述

W25Q16JV (16M bit)串行闪存为空间有限的系统提供了存储解决方案。插针和电源。25Q系列提供的灵活性和性能远远超过普通的串行闪存设备。它们是理想的代码阴影到RAM,执行代码直接从双/四SPI (XIP)和存储语音,文本和数据。该设备工作在一个2.7V到3.6V的单电源与电流消耗低至1µA断电。

1 认识W25Q16

1.1 核心特性

New Family of SpiFlash Memories

1) W25Q16JV: 16M-bit / 2M-byte (2,097,152)

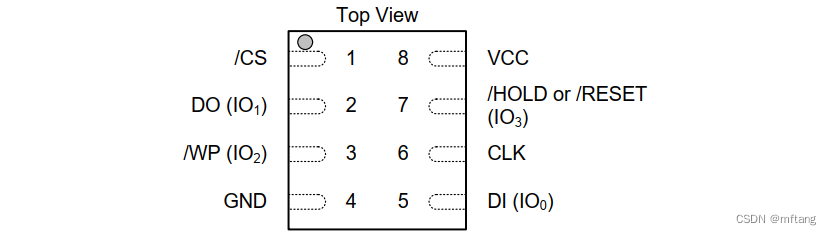

2) Standard SPI: CLK, /CS, DI, DO, /WP, /Hold

3) Dual SPI: CLK, /CS, IO0, IO1, /WP, /Hold

4) Quad SPI: CLK, /CS, IO0, IO1, IO2, IO3

5) QPI: CLK, /CS, IO0, IO1, IO2, IO3

6) SPI/QPI DTR(Double Transfer Rate) Read

7) Software & Hardware Reset

Highest Performance Serial Flash

1) 133MHz Single, Dual/Quad SPI clocks

2) 266/532MHz equivalent Dual/Quad SPI

3) 66MB/S continuous data transfer rate

4) Min. 100K Program-Erase cycles per sector

5) More than 20-year data retention

1.2 W25Q16介绍

W25Q16JV阵列被组织成8192个可编程页面,每个页面256字节。最多可达256字节一次被编程。页可以以16为一组(4KB扇区擦除),128为一组(32KB)进行擦除块擦除),组256 (64KB块擦除)或整个芯片(芯片擦除)。W25Q16JV有512个可擦扇区和32个可擦块。较小的4KB扇区允许更大的灵活性需要数据和参数存储的应用程序。

W25Q16JV支持标准串行外设接口(SPI),双/四路I/O SPI四路外设接口(QPI)以及双传输速率(DTR):串行时钟,芯片选择,串行数据I/ o (DI),I/O1 (DO)、I/O2 (/WP)和I/O3 (/HOLD)。

支持高达133MHz的SPI时钟频率双路I/O的等效时钟速率为266MHz (133MHz × 2),四路I/O的等效时钟速率为532MHz (133MHz × 4)使用快速读取双/四元I/O和QPI指令。这3种传输速率可以超过标准异步8位和16位并行闪存。连续读取模式允许高效读取24位地址时,只需8个时钟的指令开销从而实现真正的XIP(就地执行)操作。

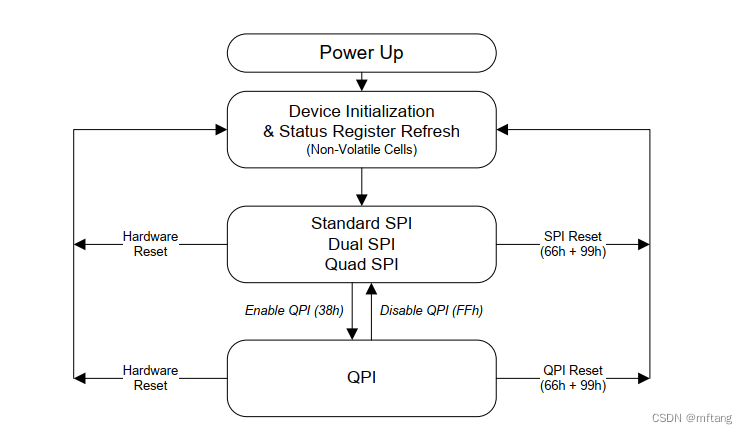

1.3 SPI / QPI Operations

W25Q16JV在使用“快速读取四路输出”等指令时支持四路SPI操作(6Bh)”和“快速读四元I/O (EBh)”。这些指令允许数据从设备传输到设备速度是普通串行闪存的四到六倍。Quad Read指令提供了一个重要的改进连续和随机访问传输速率,允许快速代码映射到RAM或直接从SPI总线(XIP)执行。当使用四路SPI指令时,DI和DO引脚变成双向IO0和IO1, /WP和/HOLD引脚分别变为IO2和IO3。四SPI指令要求设置Status Register-2中的非易失的Quad Enable位(QE)。

W25Q16JV仅在设备切换时支持QPI (Quad Peripheral Interface)操作使用“输入QPI (38h)”指令标准/双/四SPI模式切换到QPI模式。典型的SPI协议要求字节长的指令码只能通过DI引脚在8中被转移到设备中串行时钟。QPI模式利用所有四个IO引脚来输入指令代码,因此只有两个串行时钟是必需的。这可以显著减少SPI指令开销,提高系统性能在XIP环境中。不支持标准/双/四SPI模式和QPI模式。只有一种模式可以在任何时候都要活跃起来。使用“Enter QPI (38h)”和“Exit QPI (FFh)”指令进行切换这两种模式。在上电或使用“reset (99h)”指令进行软件复位后,默认状态设备的SPI模式为Standard/Dual/Quad。开启QPI模式时,非易失的Quad enable位需要设置Status Register-2中的QE。当使用QPI指令时,DI和DO引脚变成双向IO0和IO1, /WP和/HOLD引脚分别变为IO2和IO3。

2 QSPI 模式引脚介绍

2.1 Chip Select (/CS)

SPI芯片选择(/CS)引脚启用和禁用设备操作。当/CS值高时,设备为串行数据输出(DO,或IO0, IO1, IO2, IO3)引脚处于高阻抗。当取消选择,设备功耗将处于待机水平,除非内部擦除,程序或

写状态寄存器周期正在进行中。当/CS降至低时,设备将被选中,断电消耗将增加到活动水平,指令可以写入设备,数据可以从设备读取。上电后,/CS必须从高电平过渡到低电平,才能接受新的指令。/ CS输入必须在上电和下电时跟踪VCC供电电平。如果需要,在/CS引脚上的上拉电阻可以用来实现这一点。

2.2 Serial Data Input, Output and IOs (DI, DO and IO0, IO1, IO2, IO3)

W25Q16JV支持标准SPI,双SPI和四SPI操作。标准SPI指令使用单向DI(输入)引脚串行地将指令、地址或数据写入上升器件上串行时钟(CLK)输入引脚的边缘。标准SPI也使用单向DO(输出)来读取数据或CLK下降沿上设备的状态。双和四SPI指令使用双向IO引脚串行写入指令,地址或数据

到CLK上升沿的设备,并从CLK下降沿的设备读取数据或状态。Quad SPI指令需要在Status Register-2中设置非易失的Quad Enable位(QE)。当QE=1, /WP引脚变为IO2, /HOLD引脚变为IO3。

2.3 Write Protect (/WP)

写保护(/WP)引脚可以用来防止状态寄存器被写入。中使用的结合状态寄存器的块保护(CMP, SEC, TB, BP2, BP1和BP0)位和Status寄存器保护(SRP)位,小到4KB扇区的一部分或整个存储器阵列都可以是硬件保护。/WP引脚低电平有效。当状态寄存器-2的QE位设置为Quad I/O时,/WP引脚功能不可用,因为这个引脚用于IO2。

2.4 HOLD (/HOLD)

/HOLD引脚允许设备在被主动选择时暂停。当/HOLD降低时,当/CS为低时,DO引脚将处于高阻抗,并且DI和CLK引脚上的信号将被忽略(不在乎)。当/HOLD为高值时,设备可以恢复行。/HOLD函数可能很有用当多个设备共享相同的SPI信号时。/HOLD引脚激活低。当量化宽松有点状态寄存器-2设置为四路I/O, /HOLD引脚功能不可用,因为这个引脚用于IO3。

2.5 Serial Clock (CLK)

SPI串行时钟输入(CLK)引脚为串行输入和输出操作提供时序。

2.6 Reset (/RESET)

/RESET引脚允许控制器复位设备。对于8引脚封装,当QE=0时,IO3根据状态寄存器设置,引脚可以配置为/HOLD引脚或/RESET引脚。当QE=1时,8针配置的/HOLD或/RESET功能不可用。在16针的SOIC上封装时,提供了一个专用/RESET引脚,它独立于QE位设置。

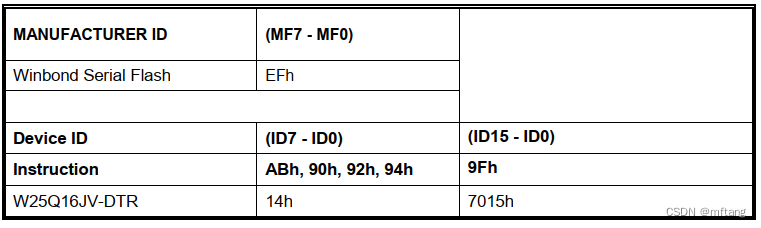

3 设备ID和设备标识

4 指令列表

5 状态和配置寄存器

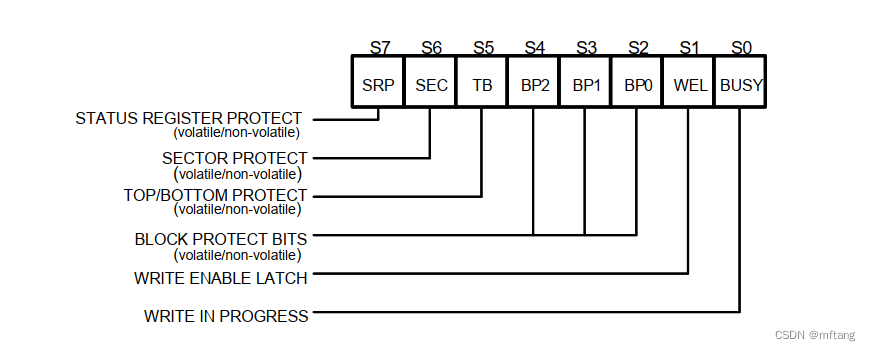

W25Q16JV提供了三个状态寄存器和配置寄存器。读状态寄存器-1/2/3指令可用于提供关于闪存阵列可用性的状态,功能包括:是否设备是写启用或禁用,写保护状态,Quad SPI设置,安全寄存器锁定状态,擦除/程序暂停状态,输出驱动强度,电源和当前地址模式。

写状态寄存器指令可用于配置器件的写保护功能,Quad SPI设置,安全寄存器OTP锁,保持/重置功能,输出驱动强度和上电地址模式。对状态寄存器的写访问由非易失状态寄存器的状态控制保护位(SRP, SRL),写使能指令,在标准/双SPI操作期间,/WP销。

5.1 状态寄存器

5.2 bit位介绍

5.2.1 BYSY-S0

BUSY是状态寄存器(S0)中的一个只读位,当设备执行a时,它被设置为1状态页程序,四页程序,扇区擦除,块擦除,芯片擦除,写状态寄存器或擦除/程序安全寄存器指令。在此期间,设备将忽略进一步的指令除了读状态寄存器和擦除/程序暂停指令(参见tW、tPP、tSE、be和tCE)交流性)。当程序、擦除或写状态/安全寄存器指令完成时,BUSY位将被清除为0状态,表明设备已准备好接受进一步的指令。

5.2.2 WEL-S1

写使能锁存(WEL)是状态寄存器(S1)中的一个只读位,在执行写操作后被设置为1启用指令。当设备禁止写时,WEL状态位清零。写禁用状态发生在电源启动或以下任何指令之后:写入禁用,页面程序,Quad页程序,扇区擦除,块擦除,芯片擦除,写状态寄存器,擦除安全寄存器和程序安全寄存器。

5.2.3 BP2, BP1, BP0 (S2-S3-S4)

块保护位(BP2、BP1、BP0)是状态寄存器(S4、S3、S3)中的非易失读写位S2)提供写保护控制和状态。块保护位可以通过“写状态”设置寄存器指令(见交流特性中的tW)。存储器阵列的全部、无或部分可以不受程序和擦除指令的保护(参见状态寄存器存储器保护表)。工厂块保护位的默认设置为0,表示不保护任何阵列。

5.2.4 TB-S5

非易失性的Top/Bottom位(TB)控制块保护位(BP2, BP1, BP0)是否对Top进行保护(TB=0)或array的Bottom (TB=1),如Status Register Memory Protection表所示。的出厂默认设置为TB=0。TB位可以根据写状态寄存器指令来设置SRP、SRL和WEL钻头的状态。

5.2.5 SEC-S6

非易失的扇区/块保护位(SEC)控制块保护位(BP2, BP1, BP0)是否保护数组的顶部(TB=0)或底部(TB=1)中的4KB扇区(SEC=1)或64KB块(SEC=0)如“Status Register Memory Protection”表所示。缺省值为SEC=0。

5.2.6 CMP-S7

补码保护位(CMP)是状态寄存器(S14)中的一个非易失读写位。它用于配合SEC、TB、BP2、BP1和BP0位,为阵列保护提供更大的灵活性。一次CMP设置为1,之前SEC、TB、BP2、BP1和BP0设置的阵列保护将被逆转。例如,当CMP=0时,可以保护顶部64KB的块,而数组的其余部分不受保护;当CMP=1时,顶部64KB块将变得不受保护,而数组的其余部分变为只读。请参阅状态注册内存保护表了解详细信息。默认值为CMP=0。